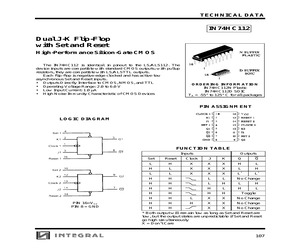

- IN74HC112D

- Integral

- Dual J-K flip-flop with set and reset, high-performance silicon-gate CMOS

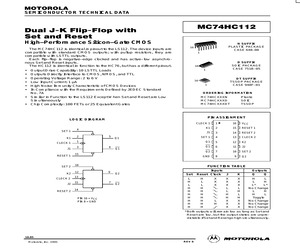

- MC74HC112D

- Motorola / Freescale Semiconductor

- Dual J-K Flip-Flop with Set and Reset

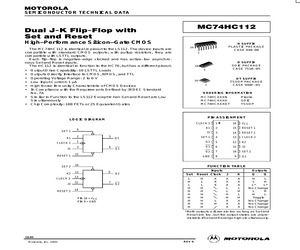

- MC74HC112DT

- Motorola / Freescale Semiconductor

- Dual J-K Flip-Flop with Set and Reset

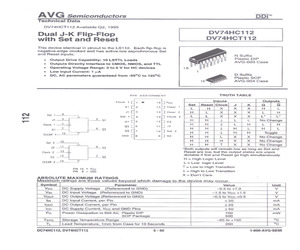

- DV74HC112D

- Avg Semiconductors

- Dual JK Flip Flop With Set and Reset Plastic Sop Surface Mount

- 74HC112DB-T

- N/a

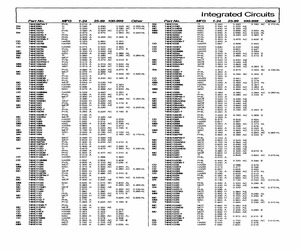

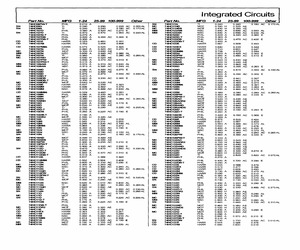

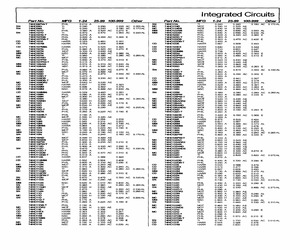

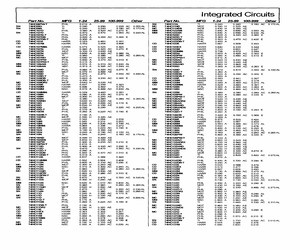

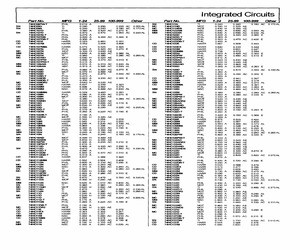

- Historical semiconductor price guide (US$ - 1998). From our catalog scanning project.

- 74HC112D-T

- N/a

- Historical semiconductor price guide (US$ - 1998). From our catalog scanning project.

- SN74HC112D

- N/a

- Historical semiconductor price guide (US$ - 1998). From our catalog scanning project.

- 74HC112D,652

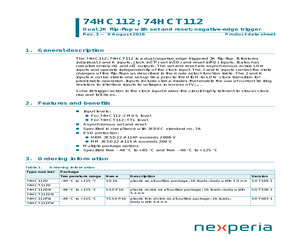

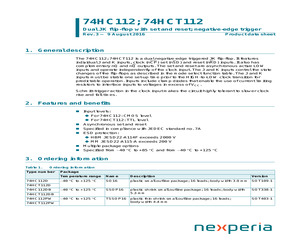

- Nexperia

- Flip Flop JK-Type Neg-Edge 2-Element 16-Pin SO Bulk

- 74HC112D,653

- Nexperia

- Flip Flop JK-Type Neg-Edge 2-Element 16-Pin SO T/R

- 74HC112D

- Nxp Semiconductors

- IC DUAL JK F-F NEG-EDGE 16SOIC - 74HC112D,652

- 74HC112D,652

- Nxp Semiconductors

- IC DUAL JK F-F NEG-EDGE 16SOIC - 74HC112D,652

- 74HC112D,653

- Nxp Semiconductors

- IC FLIP FLOP DUAL JK NEG 16SOIC - 74HC112D,653

- 74HC112DB

- Nxp Semiconductors

- IC DUAL JK F-F NEG-EDGE 16-SSOP - 74HC112DB,112

- 74HC112DB,112

- Nxp Semiconductors

- IC DUAL JK F-F NEG-EDGE 16-SSOP - 74HC112DB,112

- 74HC112DB,118

- Nxp Semiconductors

- IC DUAL JK F-F NEG-EDGE 16SSOP - 74HC112DB,118

- 74HC112DB-T

- Nxp Semiconductors / Philips Semiconductors

- dual JK flip-flop with set and reset; negative-edge trigger - Description: Dual J-K Flip-Flop with Set and Reset; Negative-Edge Trigger ; F<sub>max</sub>: 66 MHz; Logic switching levels: CMOS ; Output drive capability: +/- 5.2 mA ; Power dissipation considerations: Low Power or Battery Applications ; Propagation delay: 17@5V ns; Voltage: 2.0-6.0 V

- 74HC112D-T

- Nxp Semiconductors / Philips Semiconductors

- dual JK flip-flop with set and reset; negative-edge trigger - Description: Dual J-K Flip-Flop with Set and Reset; Negative-Edge Trigger ; F<sub>max</sub>: 66 MHz; Logic switching levels: CMOS ; Output drive capability: +/- 5.2 mA ; Power dissipation considerations: Low Power or Battery Applications ; Propagation delay: 15@5V ns; Voltage: 2.0-6.0 V

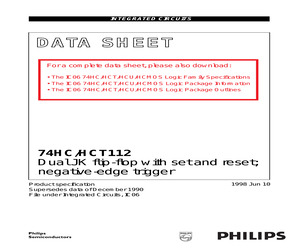

- 74HC112D

- Philips Semiconductors / Nxp Semiconductors

- dual JK flip-flop with set and reset negative-edge trigger

- 74HC112DB

- Philips Semiconductors / Nxp Semiconductors

- dual JK flip-flop with set and reset negative-edge trigger

- SL74HC112D

- System Logic Semiconductor

- Dual J-K Flip-Flop with Set and Reset

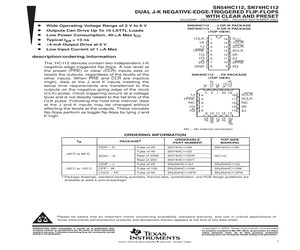

- SN74HC112D

- Texas Instruments

- IC DUAL F-F W/CLR/PRESET 16-SOIC - SN74HC112D

- SN74HC112DE4

- Texas Instruments

- IC FLIP FLOP DUAL JK NEG 16-SOIC - SN74HC112DE4

- SN74HC112DG4

- Texas Instruments

- IC FLIP FLOP JK TYPE DUAL 16SOIC - SN74HC112DG4

- SN74HC112DR

- Texas Instruments

- IC DUAL JK NEG-EDG-TRG F-F16SOIC - SN74HC112DR

- SN74HC112DRE4

- Texas Instruments

- IC FLIP FLOP DUAL JK NEG 16-SOIC - SN74HC112DRE4

- SN74HC112DRG4

- Texas Instruments

- IC FLIP FLOP JK TYPE DUAL 16SOIC - SN74HC112DRG4

- SN74HC112DT

- Texas Instruments

- IC FLIP FLOP DUAL JK NEG 16-SOIC - SN74HC112DT

- SN74HC112DTE4

- Texas Instruments

- IC FLIP FLOP DUAL JK NEG 16-SOIC - SN74HC112DTE4

- SN74HC112DTG4

- Texas Instruments

- IC FLIP FLOP JK TYPE DUAL 16SOIC - SN74HC112DTG4