# Z10040B Broadband Norton Amplifier

**Assembly and Operation Manual**

Version 1.3 August 2009

Clifton Laboratories

7236 Clifton Road

Clifton, VA 20124

(703) 830 0368

www.cliftonlaboratories.com

# **Table of Contents**

| Model Z10040B Broadband Norton Amplifier                                   | 3        |

|----------------------------------------------------------------------------|----------|

| Trademarks and Copyright                                                   | 3        |

| Warranty                                                                   | 3        |

| Safety Information                                                         | 4        |

| General Information and Specifications                                     | 5        |

| Description                                                                | 5        |

| Specifications                                                             | <i>6</i> |

| Assembly                                                                   | 7        |

| Parts Provided                                                             | 7        |

| Errata:                                                                    | 13       |

| Component Layout                                                           | 14       |

| Assembly Order                                                             | 16       |

| Post Construction Adjustment and Checkout                                  | 26       |

| Input and Output Connections                                               | 29       |

| Schematic and Theory of Operation                                          | 32       |

| Theory of Operation                                                        | 32       |

| Schematic                                                                  | 35       |

| Troubleshooting Guide                                                      | 36       |

| Voltage Data                                                               | 36       |

| Resistance Data                                                            | 37       |

| Appendix A Typical Performance Data                                        | 38       |

| Bandwidth                                                                  | 38       |

| Third Order Intermodulation                                                | 39       |

| Second Harmonic                                                            | 40       |

| 1 dB Gain Compression                                                      | 41       |

| Input VSWR                                                                 | 41       |

| Common Mode Rejection                                                      | 42       |

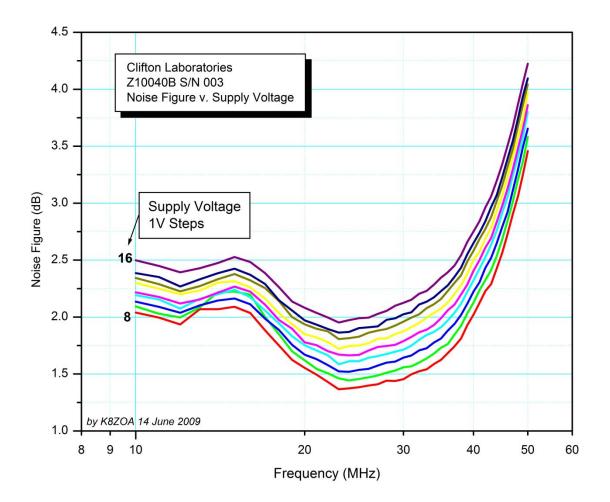

| Noise Figure                                                               | 43       |

| Appendix B – PCB Mounting Hole Dimensions                                  | 44       |

| Appendix C – Norton Amplifier Patent, US Patent No. 3,891,934              | 45       |

| Appendix D IP3, Noise Figure and Gain Performance versus Operating Voltage | 51       |

| Appendix E Manual Backdating                                               | 54       |

# **Model Z10040B Broadband Norton Amplifier**

Version 1.2 2009

(c) 2009 Jack R. Smith d/b/a/ Clifton Laboratories.

Last Revised 29 August 2009

#### **Trademarks and Copyright**

Material in this document copyrighted © 2009 Clifton Laboratories. All rights reserved. It is provided to allow the Z10040B purchasers to maintain their equipment and such other purposes as may not be prohibited by law.

#### Warranty

This warranty is effective as of the date of first consumer purchase.

**What is covered:** During the ninety (90) days after date of purchase, Clifton Laboratories will correct any defects in the Z10040B due to defective parts or workmanship (if purchased as an assembled unit) free of charge (post-paid). You must send the unit at your expense to Clifton Laboratories, but we will pay return shipping. Clifton Laboratories' warranty does not extend to defects caused by your incorrect assembly or use of unauthorized parts or materials or construction practices.

What is not covered: If the Z10040B is purchased as a kit, this warranty does not cover correction of assembly errors or misalignment; repair of damage caused by misuse, negligence, or builder modifications; or any performance malfunctions involving non-Clifton Laboratories accessory equipment. The use of acid-core solder, water-soluble flux solder, or any corrosive or conductive flux or solvent will void this warranty in its entirety. Damage to the Z10040B or equipment connected to it caused by lightning strikes is not covered under the warranty. Whether purchased as an assembled unit or as a kit, also not covered is reimbursement for loss of use, inconvenience, customer assembly or alignment time, or cost of unauthorized service.

**Limitation of incidental or consequential damages:** This warranty does not extend to non-Clifton Laboratories equipment or components used in conjunction with our products. *Any such repair or replacement is the responsibility of the customer. Clifton Laboratories will not be liable for any special, indirect, incidental or consequential damages, including but not limited to any loss of business or profits.*

Under no circumstances is Clifton Laboratories liable for damage to your equipment connected to the Z10040B resulting from use of the Z10040B, whether in accordance with the instructions in this Manual or otherwise.

# **Safety Information**

The Z10040B operates with a user-supplied DC power supply of 13 to 15 Volts at 100 to 120 mA. The Z10040B, although designed as a low signal level preamplifier, is capable of RF output power approaching the 1 watt level. This output power is capable of damaging receivers or the receiver section of a transceiver or test equipment. It is the user's responsibility to ensure that the Z10040B is properly connected to whatever devices it will be used with.

The Z10040B has no replaceable fuses; rather a self-resetting polyfuse limits short circuit current to approximately 200 mA.

The Z10040B is designed to be used only with receive-type power levels. It should not be used with transmitting equipment. The Z10040B's maximum permitted input RF power is 100 mW (+20 dBm). Power in excess of this level may damage the Z10040B or equipment connected to it, or both. In addition, since the Z10040B has appreciable gain, output power levels sufficient to damage connected equipment may occur with input signal levels well below +20 dBm.

Although the Z10040B contains protective measures, all of these protection measures assume that the Z10040B is properly grounded and that good engineering practices have been used in its installation and construction of the ground system. The Z10040B is not intended to survive a direct lightning strike to an antenna connected to its input, whether powered up or not. However, the protective measures incorporated into the Z10040B's design should aid in reducing damage.

## **General Information and Specifications**

#### **Description**

The term "Norton Amplifiers" refers to a class of transformer feedback amplifiers developed by Dr. David Norton and described in his US Patent No. 3,891,934, granted June 24, 1975 and now in the public domain. (A copy of Dr. Norton's patent is Appendix C to this Manual.) A Norton amplifier permits the distortion reducing benefits of negative feedback to be applied without impairing the amplifier's noise figure. Hence, Norton amplifiers are also known as "noiseless feedback" amplifiers.

The Z10040B is a broadband (75 KHz to 30 MHz) Norton-style amplifier providing 11 dB gain (other gain values are possible) with very high 3<sup>rd</sup> order and 2<sup>nd</sup> order intermodulation intercepts, IP3 and IP2, respectively, with a noise figure below 3.5 dB over the range 10-30 MHz. The Z10040B is designed for either indoor or outdoor use, with DC power supplied through either separate connections or duplexed over the output coaxial cable. Optional indoor and outdoor die cast enclosures are available for the Z10040B.

The Z10040B is derived from the Norton Amplifier developed by Dr. Dallas Lankford and described in his publication *Common Base Transformer Feedback Norton Amplifiers*, dated 8 June 1994, revised 21 May 2007, available at

http://www.kongsfjord.no/dl/Amplifiers/Common%20Base%20Transformer%20Feedback%20Norton%20Amplifiers.pdf.

The Z10040B modifies Dr. Lankford's design in several respects:

- Automatic input disconnect upon DC power removal along with over-voltage gas trap protection

- Improved performance below 500 KHz.

- Over voltage and reverse voltage protection on the DC Power.

- DC power either separately or duplex power.

- Optional balanced or unbalanced input.

Clifton Laboratories also offers the Z1202A DC power injector usable with the Z10040B to provide DC power over the coaxial cable.

The Z10040B is available as a kit, including a double sided, silk screened solder masked printed circuit boards and all electronic parts or as an assembled and tested printed circuit board. Options include an indoor die cast enclosure or an outdoor weatherproof die cast enclosure with BNC, UHF or Type N connectors.

Typical kit construction time is three to five hours depending on your work practices. The kit is suitable for relatively inexperienced builders, although Clifton Laboratories does not recommend it to purchasers who have never built an electronic kit before. Also, if you have never wound a toroid inductor or transformer, you might wish to ask an experienced builder to show you how it's done.

# **Specifications**

| Parameter                | Value                                                                                                |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------|--|--|

| DCD Dimensions           | 3.00" x 3.50" x 0.75" vertical clearance required. (76.2mm x 88.9mm x 19mm).                         |  |  |

| PCB Dimensions           | Four mounting holes for 4-40 screws provided, template in Appendix B.                                |  |  |

|                          | Maximum: 15V                                                                                         |  |  |

|                          | Minimum: 13.8V [may not meet specifications below this voltage. See Appendix                         |  |  |

| DC Power Required        | D for performance versus supply voltage considerations.]                                             |  |  |

| ·                        | Negative to ground, typical DC current 80-100 mA depending on bias                                   |  |  |

|                          | adjustment.                                                                                          |  |  |

| Maximum RF Power         | Do not exceed 100 milliwatts (+20 dBm). IP3 performance specifications are                           |  |  |

|                          | based upon -10 dBm signal input; performance not warranted at greater input                          |  |  |

| Input                    | levels.                                                                                              |  |  |

|                          | Performance data is for a 1:11:4 turns ratio design, 13.8 VDC after adjusting                        |  |  |

| Test Conditions          | balance trimpots for minimum 2 <sup>nd</sup> harmonic distortion. Unless otherwise                   |  |  |

| Test Conditions          | indicated, performance measurements are made with direct DC power, not                               |  |  |

|                          | duplexed. Figures stated as "typical" are not warranted.                                             |  |  |

| 3 dB Bandwidth           | 100 KHz – 30 MHz. Typical bandwidth 75 KHz - 45 MHz                                                  |  |  |

| 3 <sup>rd</sup> Order    | LEO dDm. Moscurad at 12 MHz, input signal lovel, 10 dDm. Protocol as discussed                       |  |  |

| Intermodulation          | +50 dBm. Measured at 12 MHz, input signal level -10 dBm. Protocol as discussed later in this manual. |  |  |

| Intercept                | iatei iii tiiis iiiailuai.                                                                           |  |  |

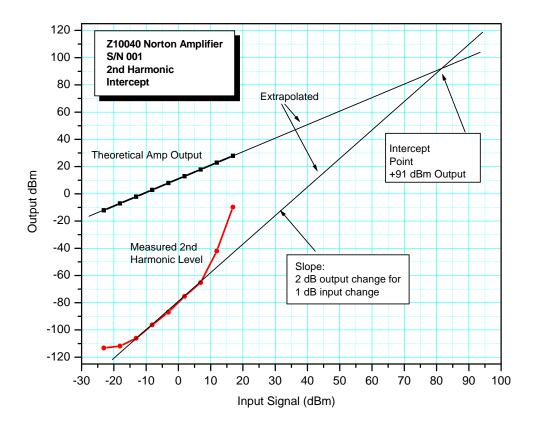

| 2 <sup>nd</sup> Harmonic | +90 dBm. Measured at 5.35 MHz, input signal level -3 dBm. Protocol as discussed                      |  |  |

| intercept                | later in this manual.                                                                                |  |  |

| Gain                     | 11 dB nominal at 1 MHz.                                                                              |  |  |

| 1 dB Gain                | +19 dBm input.                                                                                       |  |  |

| Compression              | +19 ubili lliput.                                                                                    |  |  |

| Noise Figure             | 3.5 dB maximum 10-30 MHz. Typically less than 3 dB 10-30 MHz.                                        |  |  |

| Input VSWR               | When terminated with 50 ohm load, input VSWR is less than 2:1 over the range                         |  |  |

| IIIput vovk              | 300 KHz – 30 MHz, and is typically below 1.5:1 over this range.                                      |  |  |

| Common Mode              |                                                                                                      |  |  |

| Rejection in             | Typically 50 dB at 1 MHz, decreases with increasing frequency.                                       |  |  |

| Balanced Input           | Typically 30 up at 1 Minz, decreases with increasing frequency.                                      |  |  |

| Mode                     |                                                                                                      |  |  |

# **Assembly**

#### **Parts Provided**

Before starting your build, please take a moment and inventory the parts provided against the list below. The ruler is marked in inches and  $1/16^{th}$  fractions (some photos use a ruler marked in inches and tenths, identified at 10 THS.).

# A note on how component values are identified in this manual

This document follows the international practice of using the value multiplier to indicate the decimal point. Thus, a  $1.0\mu F$  capacitor is identified as  $1\mu 0$  and a 10,000 ohm resistor is identified as 10K0.

| Photograph | Qty | ID                                                                                | Description and Comments                                                                                                                                                                                                                                     | Component<br>Marking |

|------------|-----|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|            | 4   | C1, C5, C8,<br>C9                                                                 | 1000pF leaded ceramic capacitor. Lead spacing 0.1 inches. Parts may be loose or taped as shown.                                                                                                                                                              | 102                  |

|            | 14  | C10, C11,<br>C12, C13,<br>C14, C15,<br>C16, C17,<br>C18, C2,<br>C3, C4, C6,<br>C7 | 1u0 leaded ceramic capacitor. Lead spacing 0.2 inches. Parts may be loose or taped as shown and may or may not have a "crimped" lead.                                                                                                                        | 105                  |

| 2          | 1   | C19                                                                               | 33u 63V electrolytic capacitor. This component is polarized. Polarity is identified by two methods. The negative lead is the shorter one and the negative lead is marked with a negative symbol on the capacitor case. The longer lead is the positive lead. | 33uF 63V             |

| Photograph  | Qty                        | ID         | Description and Comments                                                                                       | Component<br>Marking                                     |

|-------------|----------------------------|------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 7 8 9 1 2 8 | 2                          | C20, C21   | 1000 pF, 1206 surface mount ceramic capacitor. (Photo shows capacitors still inside the paper tape.)           | none                                                     |

| (DX)        | 1                          | D1         | Silicon diode, 1A or greater,<br>100V or greater. Typically a<br>1N4007 part                                   | 1N400x<br>where X may<br>be any<br>number<br>from 0 to 7 |

|             | 1                          | F1         | 200 mA Raychem "polyfuse"<br>PTC varistor. The supplied<br>part may or may not have a<br>"crimped" lead.       | XF020                                                    |

|             | 1                          | FB2        | Ferrite bead [FB1 designator is not used]                                                                      | No marking                                               |

|             | 2 [3-place]<br>1 [4-place] | J1, J2, J3 | J1: 4-place<br>J2 & J3: 3 place<br>0.1 inch header sockets                                                     | None                                                     |

|             | 1                          | J4         | 2 place 0.1 inch header pin<br>May be supplied as a<br>multiple pin strip to be<br>broken as needed by builder | None                                                     |

| Photograph     | Qty | ID                | Description and Comments                                            | Component<br>Marking |

|----------------|-----|-------------------|---------------------------------------------------------------------|----------------------|

|                | 1   | None              | Shorting jumper for 2 place 0.1 inch header pins                    | None                 |

| CONTROL STATES | 1   | K1                | G6H-2F-DC12 double pole,<br>double throw 12V surface<br>mount relay | G6H-2F-<br>12VDC     |

| 2              | 4   | L1, L2, L3,<br>L4 | 1m0 RF choke (shielded)<br>high current                             | None                 |

| 2              | 1   | L5                | 1m0 RF choke, high current unshielded                               | 5800-102             |

|                | 2   | Q1, Q2            | NPN transistors, VHF, type<br>2N5109                                | 2N5109               |

|   | Qty | ID   | Description and Comments                                                                          | Marking |

|---|-----|------|---------------------------------------------------------------------------------------------------|---------|

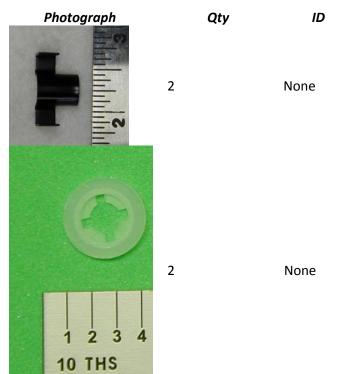

| 2 |     | None | Heat sinks for Q1 and Q2                                                                          | None    |

| 2 |     | None | Nylon insulating spacer for Q1 and Q2.  Note this spacer has four serrations in the inner opening | None    |

1/4 watt, 1/8 metal film resistors

These parts have five color bands:

- 1. 1<sup>st</sup> significant figure

- 2. 2<sup>nd</sup> significant figure

- 3. 3<sup>rd</sup> significant figure

- 4. Multiplier (number of zeros or N in 10<sup>N</sup> notation)

- 5. Tolerance (1% = brown)

Example: brown-green-black-brown-brown = 1 5 0 1 1:  $150 \times 10^{1}$ , 1% tolerance = 1500 ohms, ±1%

| 2 | R1,R6             | 560R                                                                             | Green-blue-<br>black-black-<br>brown      |

|---|-------------------|----------------------------------------------------------------------------------|-------------------------------------------|

| 2 | R4,R12            | 49R9 *first band is yellow, but looks more like green with some lighting sources | Yellow*-<br>white-white-<br>gold-brown    |

| 2 | R10, R5           | 1K50                                                                             | Brown-<br>green-black-<br>brown-<br>brown |

| 4 | R2, R7,<br>R9,R11 | 10R0                                                                             | Brown-<br>black-black-<br>silver-brown    |

Component

| Photograph  | Qty ID Description and Comments |                 | Component<br>Marking                                                                                   |                                           |

|-------------|---------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------|

| - N         | 2                               | R3, R8          | 100R Trim-pot                                                                                          | 101                                       |

|             | 1                               | RV1             | 14mm dia. 18V over-voltage<br>MOV                                                                      | 180M                                      |

|             | 2                               | SA1, SA2        | Spark gap Either of the following may be provided: 90V 75V                                             | 90V (and date code) EC 75 (and date code) |

| Same as J4. | 2                               | TP1, TP2        | Test points. Use header pin. May be supplied as a multiple pin strip to be broken as needed by builder | None                                      |

| Same as J4  | 3                               | None            | 3 place header pins. May be supplied as a multiple pin strip to be broken as needed by builder         | None                                      |

| 0           | 4                               | T1,T2,T3,<br>T4 | 0.5 inch diameter ferrite cores; builder to wind                                                       | None                                      |

| Photograph          | Qty                   | Qty ID Description and Comments |                                                                                                                                                                                                                                                                    | Qty ID Description and Commer     |  | Component<br>Marking |

|---------------------|-----------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|----------------------|

|                     | 1                     | РСВ                             | Printed circuit board.<br>Identified as Z10040B                                                                                                                                                                                                                    | Z10040B<br>and revision<br>number |  |                      |

| None                | 1 length #24<br>wire  | None                            | No. 24 AWG magnet wire, use for T2 and T4                                                                                                                                                                                                                          | None                              |  |                      |

| None                | 2 lengths #26<br>wire | None                            | No. 26 AWG magnet wire, use for T1 and T3. One length red, one length green.                                                                                                                                                                                       | None                              |  |                      |

| 1 2 3 4 5<br>10 THS | 4                     | None                            | Washers for L1-L4. Note these washers do not have serrations in the inner opening and are larger diameter than the two insulators for Q1 and Q2.  The supplied parts may be nylon as illustrated in the upper photograph or hard fiber as in the lower photograph. | None                              |  |                      |

| _ | <br> |    | _ |   |

|---|------|----|---|---|

| - | -    | ۱Т | _ | ۰ |

|   |      |    |   |   |

None known for Rev 02 PCB.

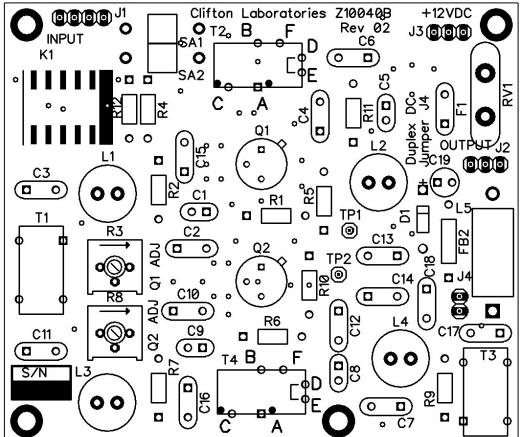

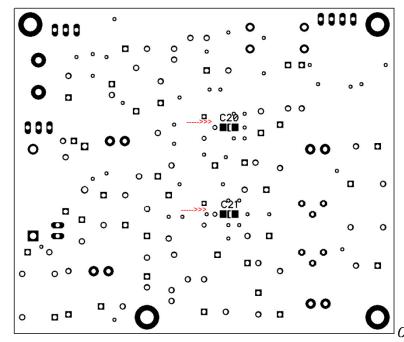

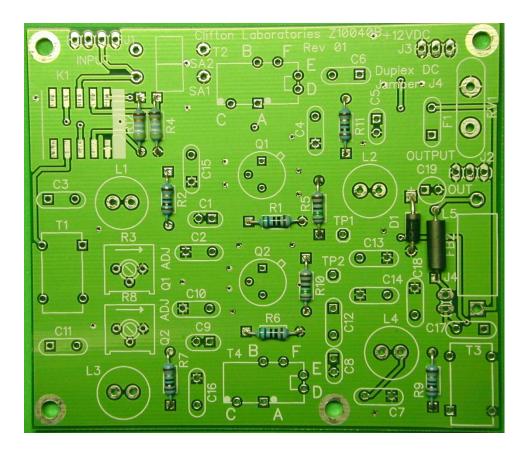

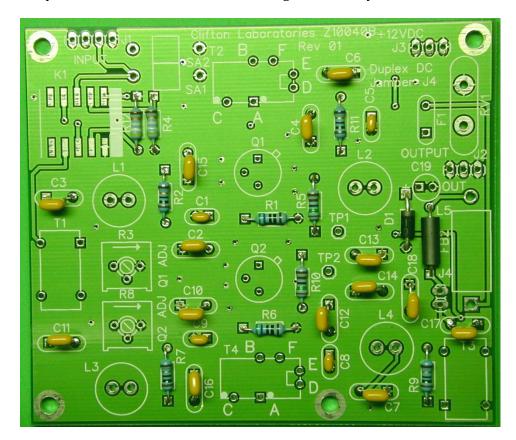

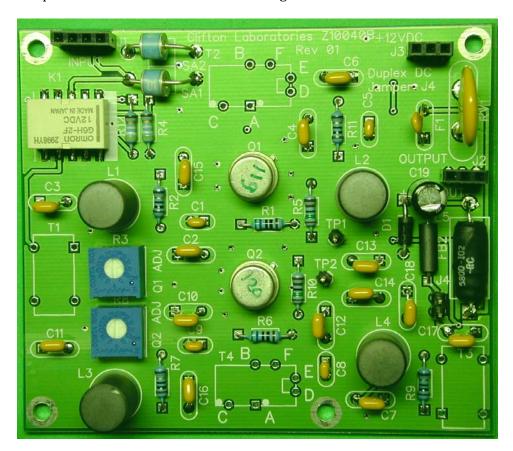

#### **Component Layout**

Top view

C20 and C21 install on the PCB

bottom. There is no silk screening identifying the location for these parts.

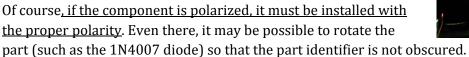

## Component Orientation

As a matter of good construction practice, most builders orient <u>non-polarized components</u> in the following fashion:

- If the component is color coded, such as most resistors, orient so that the color code reads in the same direction as the silk screening designator. R1, for example, is a 560 ohm 1% resistor; color coded green blue black black brown. Note that the color code is oriented so it reads left-to-right, just as the component silk screened R1 designation.

- Parts with a printed value code are oriented so that the part value may be easily read. For example, C11 is a 1u0 capacitor, marked 105. The part is installed with the printed "105" identification facing away from T1 so that the marking is more easily read.

# **Assembly Order**

The Z10040B is a relatively simple kit. The most complex part is winding the transformers, and even this is not difficult.

The assembly order generally follows component height—the smallest components are installed first, and the transformers last. (Where there is no difference, the photos are of the rev 02 PCB.)

| Install the ¼ watt 1% metal film resistors                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R1 560R green-blue-black-brown-brown                                                                                                                                                                                                                                                                                                            |

| R6 560R green-blue-black-brown-brown                                                                                                                                                                                                                                                                                                            |

| R4 49R9 yellow-white-white-gold-brown (yellow may look greenish under fluorescent lighting)                                                                                                                                                                                                                                                     |

| R12 49R9 yellow-white-white-gold-brown (yellow may look greenish under fluorescent lighting)                                                                                                                                                                                                                                                    |

| R5 1K50 brown-green-black-brown                                                                                                                                                                                                                                                                                                                 |

| R10 1K50 brown-green-black-brown-brown                                                                                                                                                                                                                                                                                                          |

| R11 10R0 brown-black-black-silver-brown                                                                                                                                                                                                                                                                                                         |

| R9 10R0 brown-black-black-silver-brown                                                                                                                                                                                                                                                                                                          |

| R2 10R0 brown-black-black-silver-brown                                                                                                                                                                                                                                                                                                          |

| R7 10R0 brown-black-black-silver-brown                                                                                                                                                                                                                                                                                                          |

| Install D1, the reverse polarity protection diode. This will be a $1N400x$ series device, marked $1N400x$ where x may by any digit from 0 to 7. Observe polarity when installing the diode; the diode body will be marked with a bar or ring around one end. The lead from the marked end goes into the pad marked with a bar and the $+$ sign. |

| Install FB2, the ferrite bead. (FB1 is not used.) The ferrite bead is not marked and is not polarity sensitive.                                                                                                                                                                                                                                 |

| The photo below shows the PCB at this stage of assembly.                                                                                                                                                                                                                                                                                        |

Install 1u0 capacitors (marked 105) at:

- □ C3

- □ C11

- ☐ C10

- □ C2

- □ C4

- □ C14

- ☐ C18

- ☐ C17

- ☐ C16

- □ C15

- □ C6

- ☐ C13

- □ C12

- □ C7

Install 1000pF capacitors (marked 102 or ) at:

- □ C1

- □ C9

- □ C8

- □ C5

The photo below shows the PCB at this stage of assembly.

- ☐ Install L5, 1m0 RF choke, marked 5800-102.

- Install F1 (RXE020 200 mA polyfuse, marked XF020). Depending on the available product, this component may have parallel, crimped leads or angled leads.

To install the crimped lead version, slip one lead into the mounting hole so that the kink or crimp snaps across the PCB. Put the second lead into the other mounting hole and gently pull (with long nose pliers) the second lead from the underside of the board until it

likewise snaps into the mounting hole. If this process is too difficult, you may simply install F1 with the crimped leads above the PCB surface. Solder.

If the angled leaded device is provided, install until the bend in the lead contacts the top of the printed circuit board pad. Solder.

| Install RV1, the MOV over-voltage protector, marked 180M. RV1 is not polarized and may |

|----------------------------------------------------------------------------------------|

| be installed in either orientation.                                                    |

☐ Install R3, a 100R trimpot, marked 101.

Install R8, a 100R trimpot, marked 101.

Install the four 1m0 shielded RF chokes. These chokes are constructed with a ferrite cylinder for shielding and potted with epoxy. It is common for the epoxy to slightly extend beyond the shield bottom. To provide better mechanical support, install a nylon or fiber washer between the choke and the PCB as illustrated to the right. Trial fit the choke and washer in the PCB. In some cases, the epoxy will still prevent a good mechanical fit. In this case, trim or slot the inside of the nylon washer with a hobby knife, being careful not to cut yourself during the process.

Alternatively, you may use the washer without trimming, accepting a small gap between the choke/washer/PCB assembly.

Recommended assembly process: Fit all four of the RF choke and washer assemblies to the PCB but do not solder. Put a small piece of flat material, such as a piece of metal or thin wood or plastic on top of all four chokes, creating a "sandwich" with the chokes as the filler and the PCB and metal the bread. Hold the sandwich together and flip the assembly upside down so that the choke leads are sticking up and place the "sandwich" on the workbench. Hold the PCB down to apply pressure to seat the choke/washer assembly against the PCB. Solder one lead of each choke. After soldering one lead of all four chokes, pick up the PCB and verify each choke is seated as well as possible against the washer and the PCB. If any choke is not fully seated, press it against the PCB while heating the solder joint. After all chokes are fully seated, solder the remaining leads.

| Ч | P1                                                                                                                                                                                                                                                                                                                            |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | L2                                                                                                                                                                                                                                                                                                                            |

|   | L3                                                                                                                                                                                                                                                                                                                            |

|   | L4                                                                                                                                                                                                                                                                                                                            |

|   | Install the three-pin header socket (female) at J2.                                                                                                                                                                                                                                                                           |

|   | Install C19 (33µF, 63V electrolytic capacitor). This is a polarized part. Polarity may be indicated by either (or both) of the following: (a) The capacitor has a negative side marking; (b) the positive lead is the longest. Install C1 ensuring the positive lead is inserted into the pad marked with the + sign. Solder. |

| Locate the two 2N5109 transistors and the two nylon insulators. Note that the insulator has four notches.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Slip one insulator over each transistor, orienting it so that the three leads fit into notches.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Install Q1 (marked 2N5109) with its insulator at Q1. The transistor body / insulator combination should be flush against the PCB surface. Verify that no leads have been bent and that Q1's emitter tab aligns with the silk screen tab mark before soldering.                                                                                                                                                                                                                                                             |  |  |

| Install Q2 (marked 2N5109) with its insulator at Q2. The transistor body / insulator combination should be flush against the PCB surface. Verify that no leads have been bent and that Q2's emitter tab aligns with the silk screen tab mark before soldering.                                                                                                                                                                                                                                                             |  |  |

| Install K1 relay, marked as G6H-2F; orient the marking bar on the relay to match the thick bar on the PCB silkscreen as shown in the photo at right. To install K1, first apply a light solder coat to one of the end pads on the PCB. Hold K1 on top of the pad and gently press down on it whilst heating the tinned pad. Check K1's alignment to verify that all pins are centered in their associated pads. Solder the diagonal pad. Recheck alignment and solder the remaining pins in place. Touch up the first pad. |  |  |

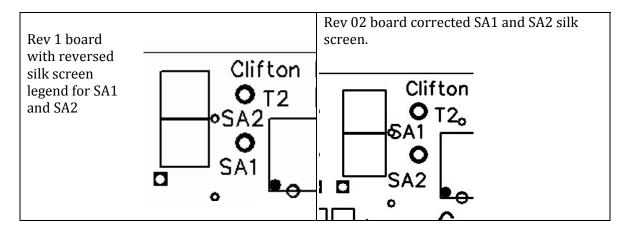

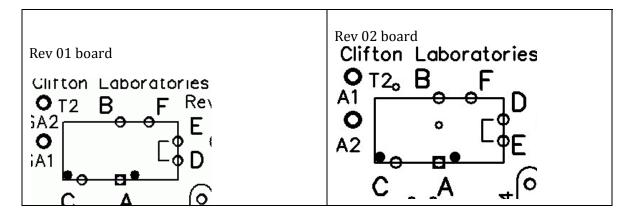

| Install SA1, the spark gap, marked either 90V plus a date code or EC75 plus a date code. SA1 is not polarized and may be installed in either orientation. Be careful when bending the leads as the ceramic body is fragile. SA1 should be installed so that the body is approximately 1/8th inch (3 mm) above the PCB surface.                                                                                                                                                                                             |  |  |

| Install SA2, the spark gap, marked either 90V plus a date code or EC75 plus a date code. SA2 is not polarized and may be installed in either orientation. Be careful when bending the leads as the ceramic body is fragile. SA1 should be installed so that the body is approximately 1/8th inch (3 mm) above the PCB surface.                                                                                                                                                                                             |  |  |

| SA1 and SA2 should not contact each other. Slightly bend SA1 or SA2 or both, if necessary to provide approximately $1/8^{th}$ inch (3 mm) horizontal spacing between SA1 and SA2. Be careful when bending these parts not to over-stress SA1 and SA2's ceramic body.                                                                                                                                                                                                                                                       |  |  |

| Note: The silk screen legends for SA1 and SA2 are reversed in Board Rev. 01.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Install the three-pin header sockets (female) at J3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Install the four-pin header sockets (female) at J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Locate the header pin (male) strip and break or cut two pins from the strip. Install the two pins at J4. (The short side goes into the pad holes.)                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Cut or break two individual pins from the header pin strip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Install one pin at TP1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

☐ Install one pin at TP2.

At this point, all components should be installed on the PCB's top surface, except for the four transformers and the two heat sinks. The two 1000pF surface mount capacitors are installed later in the build.

The photo below shows the PCB at this stage.

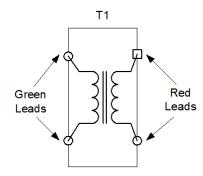

Locate the No. 26 AWG magnet wire. (It is the smaller diameter of the two wire sizes.) One length of green insulated wire is provided and one of red insulated wire.

Cut four lengths of the wire:

Two pieces green, each 11 inches (280 mm) long. Two pieces red, each 11 inches (280 mm) long.

Take one piece of red wire and one piece of green wire and twist approximately 60 turns. Repeat for the second pair of red and green wires. (A variable speed drill, running slow speed, speeds up the twisting process.)

At this point, you should have two twisted wire sections, each approximately 11 inches (280 mm) long, each twisted pair with one red and one green wire.

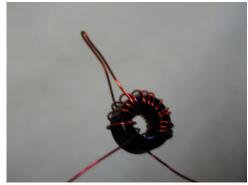

Wind the twisted wire 10 turns onto one of the ferrite cores.

As a reminder, a turn is counted when the wire passes through the hole in the core.

Start by inserting the cut end approximately one inch (25 mm) through the core. Thread the doubled end through and wind 10 turns. Space the turns so that the windings

occupy approximately 75% of the core perimeter (270 degrees if you prefer to think in those terms).

Repeat for the second transformer.

Congratulations. You have completed winding two bifilar broadband transformers, T1 and T3.

Locate the PCB and look at the silk screen outline for T1 and T3. Note that each has four pads, comprised of three round pads and one square pad, oriented as shown in the drawing.

The green wires connect to the two round pads on one side and the red wires connect to the one square and one round pad on the opposite side. [This is not critical and one can interchange the green and red leads, but troubleshooting will be easier if all the Z10040B's are built the same way.]

Un-twist the pigtails so that you have four separated wires. Remove the insulation and tin the four wires.

The wire leads should be formed as illustrated in the photo to the right. Install the transformer as shown in the drawing at T1.

Note: The red and green wire supplied is "solderable" and the insulation will melt if heated with a blob of molten solder. This heating and tinning must be done <u>before</u> the transformers are installed in the PCB.

A common error in installing T1 and T3 (as well as T2 and T4) is that the insulation is not fully removed from the wire due to insufficient heating.

Repeat this process for T3 and install.

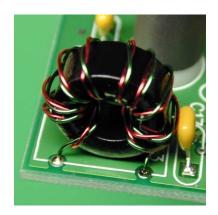

Your transformers should resemble the one photographed at the right.

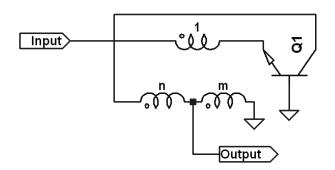

The remaining step is to wind T2 and T4, the matching and feedback transformers. These transformers should be as identical as possible and <u>must</u> be phased (wound) the same way or else you will build an oscillator instead of an amplifier. If you <u>carefully</u> follow the instructions in this manual, your transformers will work the first time. Before winding T2 and T4, take a moment to read the installation steps and study the drawing and photographs.

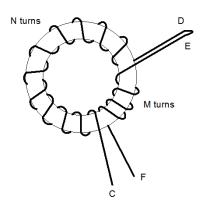

This manual describes transformers resulting in 11 dB nominal gain, with a 1:11:4 winding ratio. Other winding ratios are possible with different gain as described elsewhere in this manual. In the context of drawing below, this configuration is N=11, M=4.

Cut two lengths of #24 AWG magnet wire, each length 16 inches (400 mm) long.

This wire will be wound 15 turns on a ferrite core, as illustrated at the right. The letters C...F on the drawing correspond to T2 and T4's PCB pads.

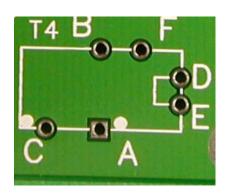

Before winding the transformers, take a moment and look at the PCB outline for T2 and T4.

Start by threading the wire through the core with approximately one inch (25 mm) projecting from the core. This short starting end is C in the drawing.

Wind 11 turns (N) following the orientation shown in the drawing. Note the direction of winding. (I'm left handed and this is how I wind a toroid.) When completed with all 15 turns, the winding will occupy 80 to 85% of the core perimeter.

As a reminder, a turn is counted when the wire passes through the hole in the core.

Extend the 11<sup>th</sup> turn approximately one inch (25 mm) and double it back. (The doubled wire will become ends

D and E). Wind four more turns (M), ending at end F. Trim the F wire to be approximately one inch (25 mm) long.

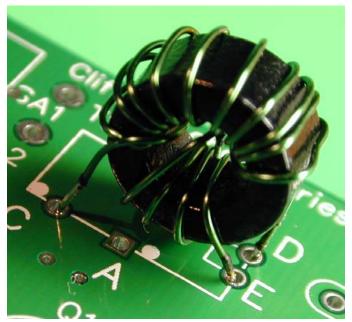

The photos below shows a transformer at this stage, before the loop is cut and the end wires trimmed.

Cut the loop so that the two free ends are approximately one inch (25 mm) long. Remove the insulation on all four ends and tin. You may find it helpful to fit the transformer into the PCB to see how it fits before continuing to the next step.

Insert the leads into T2 holes C, D, E and F, following the drawing, and solder these four leads.

Locate the remaining length of No. 24 AWG magnet wire and cut two lengths 1.25 inch (32 mm) long. These will be the single turn winding A-B. Strip and tin each end approximately 0.25 to 0.375 inches (6.5 mm to 9.5 mm) and install between pads A and B, passing the wire through the transformer's central hole. Installing this wire will be easier if you install the wire vertically (not passed through the core) in the pad away from the board edge. Solder the wire in place. Then pass it through the transformer core and into the outside pad hole. Solder.

Repeat this process for T4 with the second transformer.

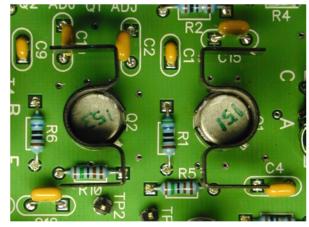

The photographs below show T4 installed.

Install the heat sinks on Q1 and Q2. If you have it, a small amount of heat sink compound or thermal grease can be used to improve the thermal connectivity between the heat sink and

the transistor body.

In order to provide maximum stability, orientate the heat sinks so as to minimize capacitive coupling between Q1 and Q2, following the photograph at the right.

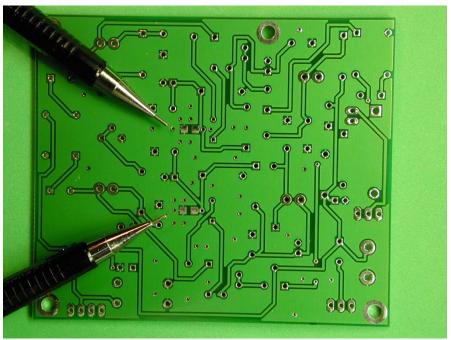

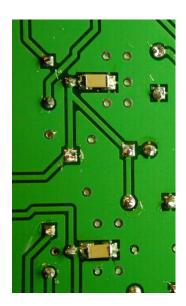

The last construction step is to install C20 and C1, the 1000pF 1206 surface mount capacitors. Both C20 and C21 are mounted on the bottom of the PCB. After installing C20 and C21, please handle the PCB with care to avoid damage to it. DO NOT FLEX the PCB as you may easily crack C20 or C21.

Flip the PCB so that the trace side is up. The pencils shows where C20 and C21 are installed.

# ☐ Installation procedure:

- 1. Lightly tin the non-ground pads for C21 and C21.

- 2. Using forceps or a very light touch with long nose pliers, slide C20 into place while heating C20's nonground pad. Check that C20 is more or less centered on the pads and remove the soldering iron when centered. Too much pressure will crack these parts so use a light touch.

- 3. Solder the ground pad. Touch up the non-ground pad.

- 4. Repeat steps 2 and 3 for C21.

- 5. Although the ground pad uses "thermal relief" it may still be difficult to make with a small soldering pencil, as the large foil area requires more heat capacity than a normal floating pad.

## **Post Construction Adjustment and Checkout**

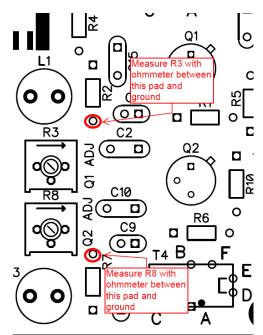

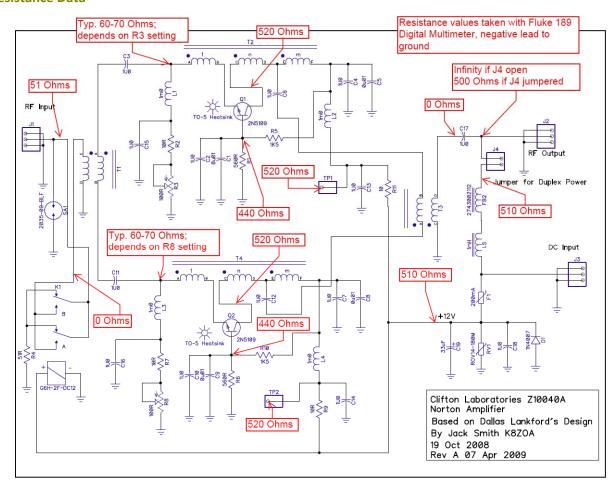

Before powering up the Z10040B, take a moment to make resistance checks and pre-set R3 and R8.

With an ohmmeter measure and adjust R3 and R8 to 50 ± 2 ohms. (Both measuring points are with respect to ground, with the negative lead of the ohmmeter to ground.)

R3: Measuring point is junction of R3 and R2, as illustrated to the right.

R8: Measuring point is junction of R8 and R7 as illustrated to the right.

You may wish to make a complete set of resistance measurements as developed in the maintenance section of this manual, or you may wish to make an abbreviated set of resistance measurements described below before apply power for the first time.

All readings are taken with a Fluke 189 digital multimeter with low-voltage ohms. Negative lead to ground and positive lead to the indicated test point. Look for gross divergence from these values, not small differences, as different ohmmeters may yield different results where semiconductor junctions are in the path. Since the Z10040B has two identical sections comprising the push-pull design, look for differences in symmetry, where the equivalent point reads significantly different in one section compared with the other.

| Abbreviated Resistance Checks Before Applying Power |              |                                                     |  |  |  |

|-----------------------------------------------------|--------------|-----------------------------------------------------|--|--|--|

| Test Point                                          | Value (Ohms) | Comment                                             |  |  |  |

| TP1                                                 | 510          |                                                     |  |  |  |

| TP2                                                 | 510          |                                                     |  |  |  |

| Q1 collector                                        | 520          | Q1's case is internally connected to the collector. |  |  |  |

| Q2 collector                                        | 520          | Q2's case is internally connected to the collector. |  |  |  |

| DC Input (J3) center                                | 510          | Should be the same with and without a jumper at     |  |  |  |

|                                                     |              | J4                                                  |  |  |  |

If you have not already done so, make up a power cable using a three-pin male header pin. Positive to the center pin and negative to the two outside pins.

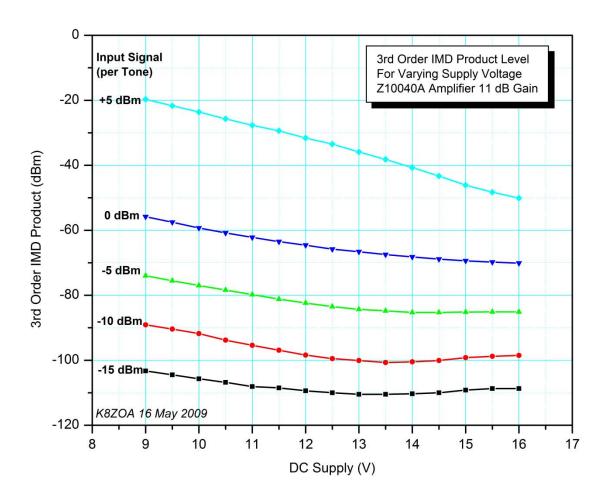

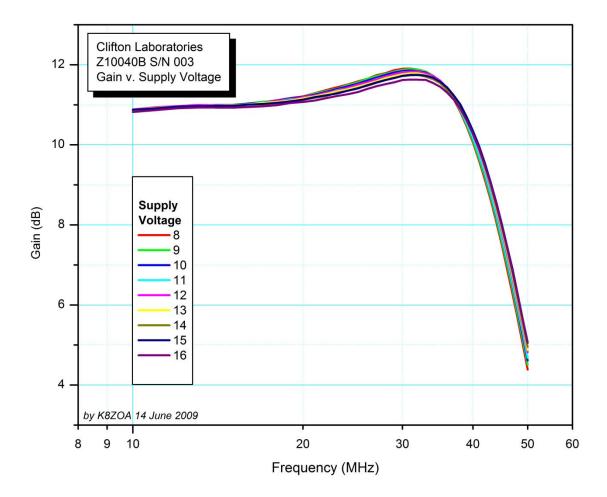

| The Z10040B will work with DC supply voltages up to 15V and down to 12V. Performance data is based upon 13.8V DC and in general slightly improved intermodulation performance will be seen with supply voltages between 13.8 and 15.0V.                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If a laboratory power supply with current limiting is available, set it for a maximum short circuit current of 175 mA and set the voltage to 0V. Connect the supply to the Z10040B at J3 (J4 duplex jumper open) and bring up the voltage slowly whilst observing the current. With R3 and R8 set for 50 ohms, the maximum current observed should be approximately 100 mA at 13.8V. If significant deviations from this value are observed, immediately remove power and investigate.                                                                                                           |

| Adjusting R3 and R8. With the normal DC supply voltage applied through J3 (J4 duplex jumper open) preferably with a laboratory power supply with current limiting set to 175 mA, adjust R3 and R8.                                                                                                                                                                                                                                                                                                                                                                                               |

| Note: If you adjust R3 or R8 to the zero ohms extreme, it may be possible to damage components in the Z10040B. Some current limiting is built into the circuit, via R2 and R7, together with the resistance of L1 and L3. However, in order to provide the maximum adjustment range to compensate for variations in Q1 and Q2, complete protection against mis-adjustment is not possible. Accordingly, when adjusting R3 and/or R8, it is imperative that you observe the total current being drawn by the amplifier, and, if possible, use a power supply with current limiting set to 175 mA. |

| In particular, the 1mH shielded inductors used at L1, L2, L3 and L4 are rated for a maximum DC current of 90 mA. <u>Under no circumstances should Q1 or Q2 be biased to draw more than 75 mA each.</u>                                                                                                                                                                                                                                                                                                                                                                                           |

| <u>Alternative 1</u> : If you do not have the ability to measure $3^{\rm rd}$ order and $2^{\rm nd}$ order intermodulation products, adjust R3 and R8 such that Q1 and Q2 have substantially equal collector currents of approximately 45 mA each.                                                                                                                                                                                                                                                                                                                                               |

| Collector current is determined by measuring the voltage drop across the 10R0 resistors, R11 and R9 via TP1 and TP2. The drop across R9 and R11 represents the sum of the collector current and the current drawn by the base bias network, which is approximately 6 mA.                                                                                                                                                                                                                                                                                                                         |

| Connect a DC voltmeter between the junction of F1/RV1 (positive lead) and TP1 (negative lead.) Adjust R3 until the voltmeter reads $0.500\pm0.050$ volts. This corresponds to $50$ mA total current, consisting of approximately 44 mA collector current through Q1 and 6 mA bias network current. Record the DC voltage:                                                                                                                                                                                                                                                                        |

| Move the negative lead to TP2 and adjust R8 for the same reading recorded above. This will set Q2's collector current to approximately match Q1's current.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Alternative 2: Adjust R3 and R8 for best $3^{rd}$ and $2^{nd}$ order intermodulation performance using the test equipment configuration you normally use for these measurements. During the adjustment process do not exceed 75 mA in either Q1 or Q2 as it is possible to damage components with over-current.                                                                                                                                                                                                                                                                                  |

A bias adjustment service for kit builders not equipped to measure IP2 and IP3 is available. Contact Clifton Laboratories for details.

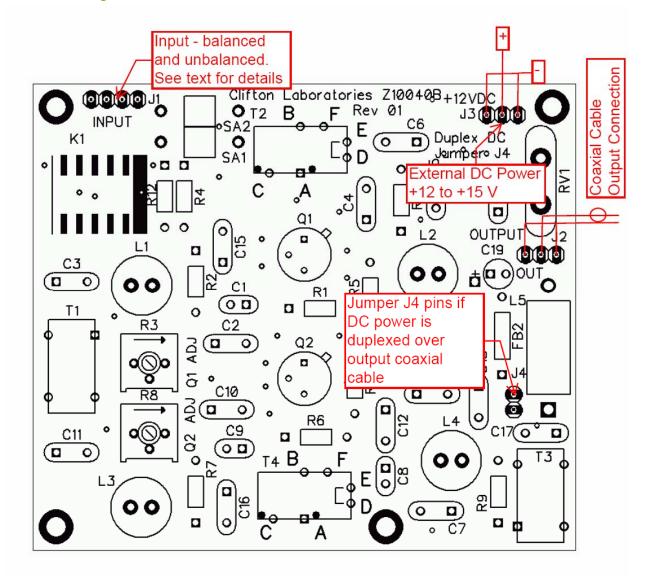

#### **Input and Output Connections**

Output and DC power connections are made to the Z10040B with 3-pin headers. Since the outside pins are always ground, either orientation is permitted. Input to the Z10040B is made with a 4-pin header and may be configured for either balanced or unbalanced input.

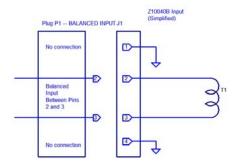

#### **Balanced Input**

To make a balanced connection to the Z10040B, use J1's two center pins, as illustrated in the drawing to the right.

If a shielded pair is used for the balanced input, the shield should be connected to the two outside pins, which are common with the Z10040B's ground plane.

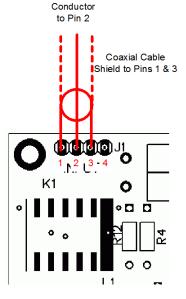

#### **Unbalanced Input**

An unbalanced input to the Z10040B should be made as described. The described method is necessary for improved stability.

The pencil point in the photo identifies J1, pin 4.

When using unbalanced input, connect the coaxial cable so that the center conductor mates with pin 2 and the shield connects to pins 1 and 3. Pin 4 may be left unconnected.

Do not use a connection that places the shield on J1, pin 2 and the center conductor on J1, pin 3.

As always when making connections to a high gain amplifier, shielded coaxial cable should be used on the output (and the input if unbalanced) and the output cable should not be routed near the input. If balanced input is used, the input cable should be twisted pair or shielded pair to avoid unwanted signal pickup or feedback and oscillation.

#### **Connections Diagram**

This completes the assembly and verification of your Z10040B Norton Amplifier.

# **Schematic and Theory of Operation**

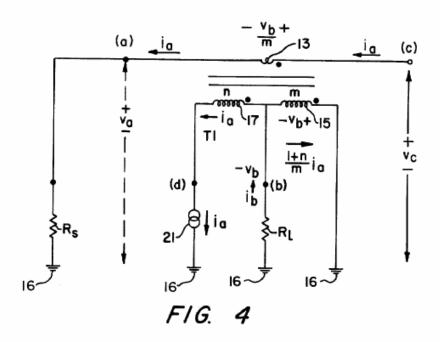

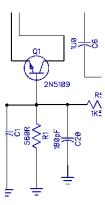

#### **Theory of Operation**

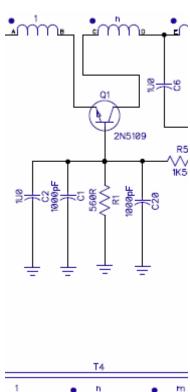

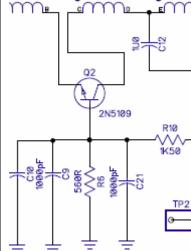

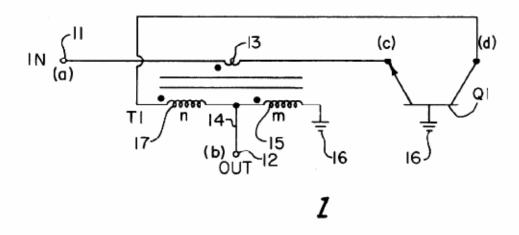

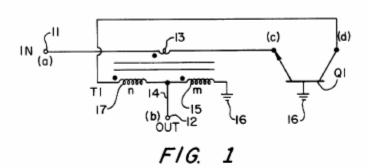

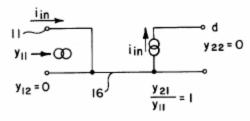

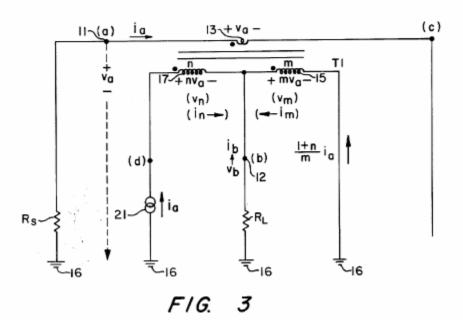

The Z10040B Norton amplifier consists of two identical amplifier sections arranged in push-pull.

The discussion below uses component designations for the section associated with Q1.

Each section is a common base (also known as "grounded base") amplifier. As such, essentially identical signal currents flow through all three sections of T2 and T1's secondary winding. Gain is achieved in the grounded base amplifier because the collector load, represented by T2's n and m windings operating as an auto-

transformer has greater impedance than the emitter input, and hence power gain results.

The figure at the right is a simplified view of an amplifier section, with all DC biasing and blocking components removed so that we may concentrate on the signal flow. The transformer turns ratios are shown as 1:n:m, but this does not mean the emitter

feedback winding must have only one turn. Rather, it is the ratio of turns that is important, so that if the emitter winding has, for example, two turns, then the number of turns in windings n and m should also be doubled.

Consider windings n and m and assume a load of impedance Z is connected from output to ground. Windings n and m form an auto-transformer with Q1's collector seeing an impedance of:

$$Z_C = Z_O \left(\frac{n+m}{m}\right)^2$$

Since the same signal current flows through the emitter and collector (neglecting base current), the gain of the common base amplifier is proportional Zc or n and m in this relationship.

The transformer turns ratios should not be arbitrarily selected, if the full benefits of the Norton amplifier are to be realized. From Patent No. 3,891,934, the following equation governs the transformer turns relationship:

$$n = m^2 \left(\frac{R_S}{R_L}\right) - m - 1$$

$$n = m^2 \left(\frac{R_S}{R_L}\right) - m - 1$$

Where

R<sub>S</sub> is the source (input) impedance

R<sub>L</sub> is the load (output) impedance

n and m are the transformer winding ratios, normalized to an emitter winding with one turn.

In our case, we wish the input and output impedances to be equal, and hence  $R_S/R_L$  = 1. Thus the turns relationship is simplified to:

$n = m^2 - m - 1$

The amplifier's transducer gain<sup>1</sup> is stated as:

$$G_t = m^2 \frac{R_S}{R_L}$$

Again, since our normal operation is with equal input and output impedances, the transducer gain  $G_t$  is simply  $m^2$ .

| Winding Ratio 1:n:m | Transducer Gain (dB) |

|---------------------|----------------------|

| 1:1:2               | 6.0                  |

| 1:5:3               | 9.5                  |

| 1:11:4              | 12.0                 |

| 1:19:5              | 14.0                 |

These figures are theoretical and the actual realizable gain is typically a dB or so less.

One significant advantage of the Norton amplifier is that the input impedance automatically tracks the output impedance. Thus, if terminated into a 50 ohm load, the input impedance is 50 ohms. If the output impedance is changed to 75 ohms, the input impedance becomes 75 ohms. (This relationship is again not perfect, but it is reasonably good with less than a 2:1 VSWR over the range 300 KHz – 30 MHz when measured in a 50 ohm system.)

DC power may be provided to the Z10040B via two feed points. First, a three-pin connector permits direct DC power connection. Secondly, adding a jumper at connector J4 permits DC power to be duplex fed over the coaxial cable transmission line carrying the amplifier's output. Of course, an appropriate DC power injector, such as Clifton Laboratories model Z1202A, will be required and the power source that is used should be selected to have low noise at the frequencies of interest.

<sup>1</sup> Transducer gain is defined as: "the ratio of the power delivered by a network to a load (PdL) to the power available from the source (Pas). Transducer gain is a function of the source and load reflection coefficients and the network sparameters." http://www.maurymw.com/support/faqs/faqs/faq9.html

Over current protection is provided by F1, a 200 mA positive temperature coefficient "polyfuse." Should the amplifier draw more than 200 mA, F1 will heat and switch to a high resistance state, thereby limiting the current drawn by the power source. So long as the voltage remains applied, F1 will remain in the high resistance state.

Over voltage protection is provided by RV1, an 18V DC (nominal) bipolar metal oxide varistor. The primary purpose of RV1 is to limit damage to the DC power source, should a nearby lightning strike or other incident induce a greater than normal voltage on the DC power line. Although RV1 is rated to begin clamping at 18V (1.0 mA clamp current at 18V), the actual onset voltage may be 20% above this figure and the clamping voltage may rise as high as 36V at 50A clamping current. Hence, even with RV1 in place and functioning properly, excessive over voltage may still occur if the disturbing event is sufficiently energetic. (The ROV14-180M device used in the Z10040B is rated at a one-time 1,000A clamp or two-times 500A clamp. However, at 1000A, the expected clamping voltage is 80V.)

Reverse voltage protection is provided by D1, a 1N400x series diode connected to be forward biased if the input polarity reverses. This causes two things to happen. First, the maximum voltage across the DC power distribution circuitry will be limited to approximately 1V by D1. Secondly, fuse F1 will enter into high resistance mode by virtue of the over current. Of course, a sufficiently robust power supply connected with reverse polarity may destroy D1 before F1 can enter high resistance mode.

The Z10040B's input is through a bifilar wound, broadband transformer, T1. Both of T1's primary terminals are brought out to J1 through K1's contacts so that either balanced or unbalanced input may be used. Balanced input signals are applied across T1's primary, which remains floating with respect to ground. If unbalanced input is used, one of T1's primary terminals is connected to ground through appropriate jumper settings at J1.

The Z10040B's input circuit is protected in two ways. First, when DC power is removed from the Z10040B, relay K1 removes the input connection and connects it to ground through R4 and R12, 49R9 ohm resistors. (If desired, the user may replace R4 and R12 with wire jumpers to the input when power is removed.) Secondly, SA1 and SA2, "gas trap" or spark protector devices are always connected across the Z10040B's input connector. Although SA1 and SA2 limit the voltage for fast rise time pulses, their break over voltage may be several hundred volts. The primary purpose of SA1 and SA2 is to limit the voltage that might otherwise be coupled over the coaxial transmission line and, secondarily, to provide some protection to the Z10040's components.

When the input is configured as unbalanced, only one of SA1 and SA2 is operational. In balanced mode, SA1 and SA2 are connected between the two balanced inputs and the Z10040B's common ground point. Likewise in balanced mode, when the Z10040B is unpowered, R4 and R12 are connected across the balanced input to the Z10040B's common ground point.

All of these protection measures assume that the Z10040B is properly grounded and that good engineering practices have been used in its installation and construction of the ground system. The Z10040B is not intended to survive a direct lightning strike to an antenna connected to its input, whether powered up or not. However, the protective measures incorporated into the Z10040B's design should aid in reducing damage, particularly where the strike is not directly to the antenna system.

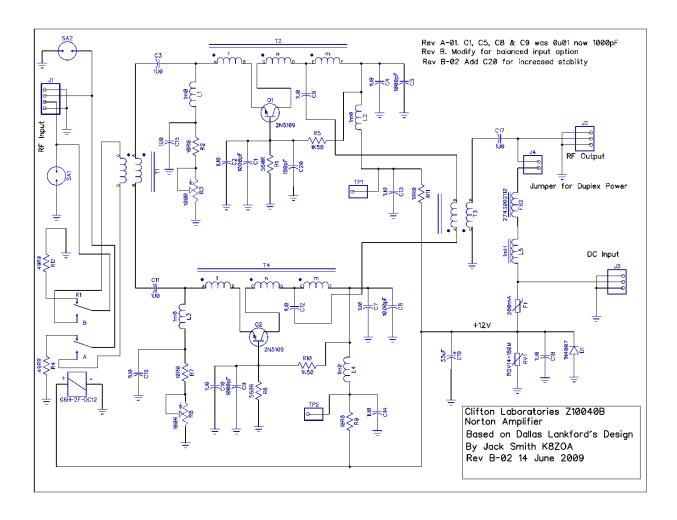

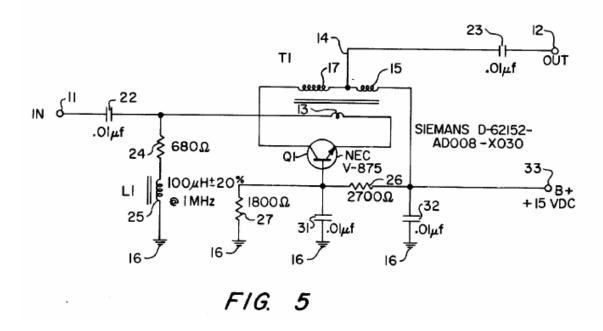

#### **Schematic**

## **Troubleshooting Guide**

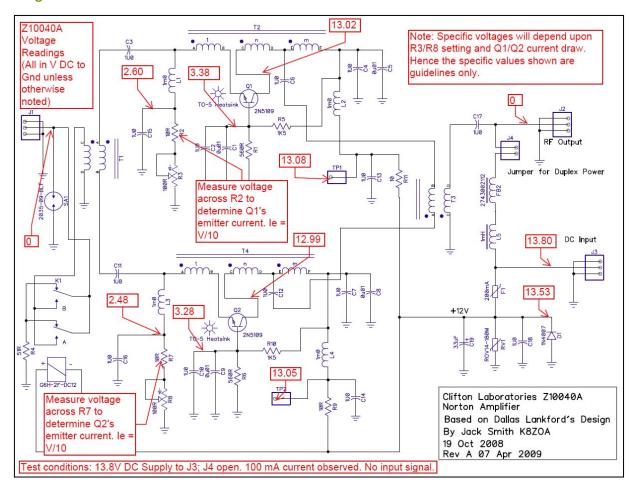

The following annotated schematics provide resistance and typical operating voltage data for the Z10040B. (The schematic shown is the Z10040A. No resistance or voltage changes exist between the "A" and "B" versions of the Z10040.)

# **Voltage Data**

#### **Resistance Data**

# **Appendix A Typical Performance Data**

Except for common mode rejection, the data presented below is taken from one Z10040A amplifier. There is no significant performance difference between the "A" and "B" versions of the Z10040, except for differences associated with operating a balanced input.

While it is believed representative of Z10040A and B amplifiers, due to component tolerance, assembly practices and test setup, the performance level seen in these measurements should be regarded as *typical* and is not guaranteed.

Unless otherwise specifically noted, the data is taken with unbalanced input.

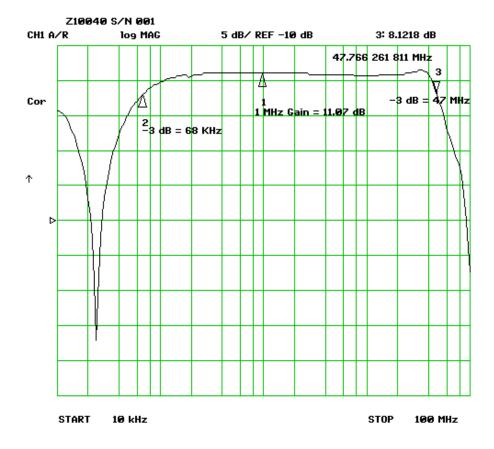

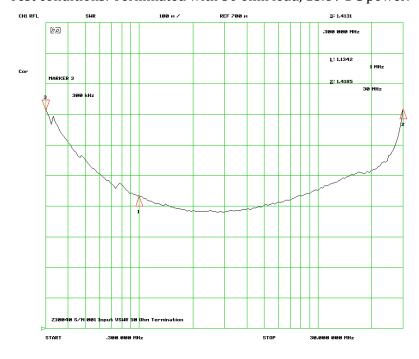

### **Bandwidth**

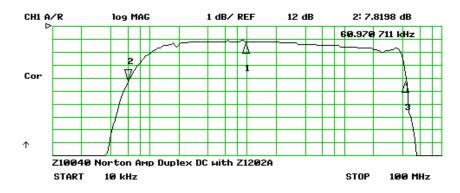

Test Conditions: Direct DC feed.

Test Conditions: Duplex DC feed over coaxial cable with Clifton Laboratories Z1202A power coupler.

N STIMULUS val

1 1 MHz 10.832 dB

2 60.970 711 kHz 7.8198 dB

3 43.064 683 001 MHz 7.8390 dB

## **Third Order Intermodulation**

Test conditions: Two test signals at 900 KHz and 1100 KHz at 0 dBm (each tone).

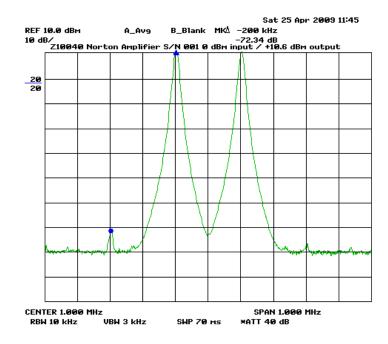

# **Second Harmonic**

Test Conditions: 5.4 MHz

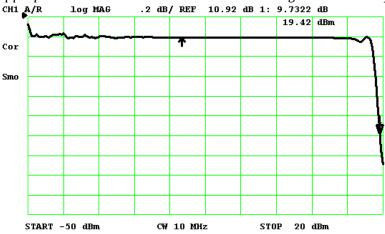

# 1 dB Gain Compression

Test Conditions: CW signal at 10 MHz, Z10040 input level between -50 dBm and +20 dBm. 1 dB gain compression point +19.42 dBm input.

Note: This test can easily damage test equipment as the output power approaches 1 watt.

Appropriate attenuators must be used to limit signal levels to safe values.

# **Input VSWR**

Test conditions: Terminated with 50 ohm load, 13.8V DC power.

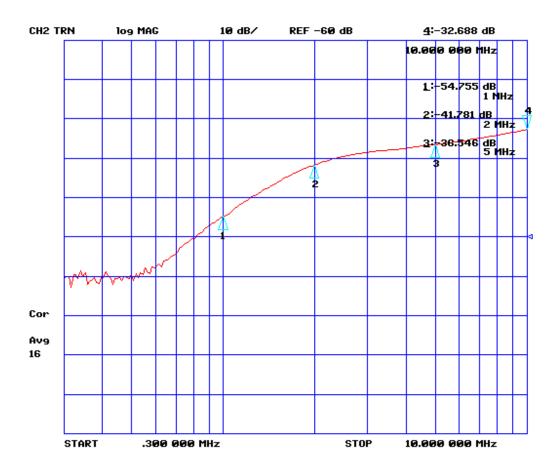

# **Common Mode Rejection**

Test conditions: Unbalanced input applied to J1 pins 2 and 3 in parallel. Ground to J1 pins 1 and 4. Frequency range: 300 KHz – 10 MHz. Input signal level -15 dBm. Plot shows output signal level, with 0 dB being a direct connection between input and output.

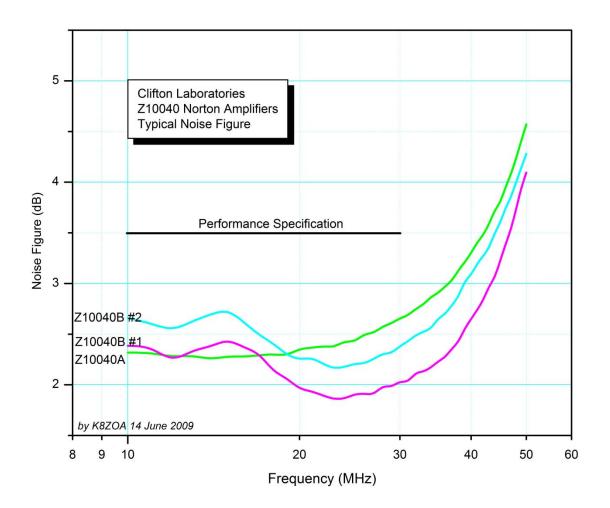

# **Noise Figure**

Data taken with an HP8970A noise figure meter and AIL 7615 noise source at 15V supply. Noise figure differs by as much as 1 dB from amplifier to amplifier.

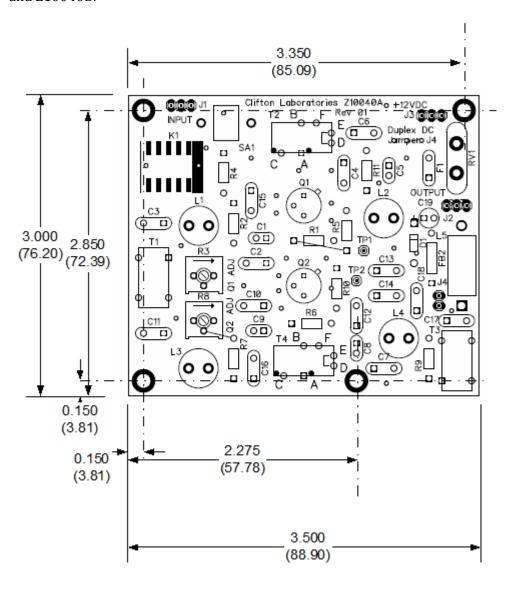

# **Appendix B – PCB Mounting Hole Dimensions**

Drawing is  $\underline{not}$  to scale. There is no change in mounting hole spacing and size between the Z10040A and Z10040B.

Dimensions in inches and (mm)

# United States Patent [19] [11] 3,891,934 Norton et al. [45] June 24, 1975

| [54] | TRANSISTOR AMPLIFIER WITH IMPEDANCE MATCHING TRANSFORMER |                                                                              |  |

|------|----------------------------------------------------------|------------------------------------------------------------------------------|--|

| [75] | Inventors:                                               | David E. Norton, Framingham,<br>Mass.; Allen F. Podell, Los Altos,<br>Calif. |  |

| [73] | Assignee:                                                | Adams-Russell Co., Inc., Waltham, Mass.                                      |  |

| [22] | Filed                                                    | May 22, 1974                                                                 |  |

| [21] | Appl. No.:                                               | 472,281                                                                      |  |

|      |                                                          |                                                                              |  |

| [52] | U.S. Cl                                                  |                                                                              |  |

| (511 | Int. Cl.                                                 | H03f 3/0                                                                     |  |

| [58] | Field of Sc                                              | earch                                                                        |  |

|      |                                                          |                                                                              |  |

References Cited

UNITED STATES PATENTS

10/1954

2/1955

Kores...... 330/40 X

DeWhite et al. ..... 330/12 X

[56]

2,691,077

2,701,281

Primary Examiner—R. V. Rolinec

Assistant Examiner—Lawrence J. Dahl

Attorney, Agent, or Firm—Charles Hieken, Esq.; Jerry

Cohen, Esq.

# [57] ABSTRACT

An amplifier includes a transistor and transformer having a primary winding and a tapped secondary winding. The primary winding is connected in series between the input terminal and the transistor emitter. The transistor base and one end of the secondary winding is grounded. The other end of the secondary winding is connected to the transistor collector. The transformer secondary tap is connected to an output terminal. The ratio of that portion of the secondary turns connected between the tap and  $r \cdot f$  ground and the primary turns is m. The ratio of that portion of the secondary turns connected between the tap and the transistor collector and the primary turns is n. For two-way impedance match between a source resistance  $R_s$  and a load resistance  $R_t$ ,  $n = m^2 (R_s/R_t) \cdot m \cdot 1$ .

#### 8 Claims, 5 Drawing Figures

1

F1G. 2

3,891,934

SHEET 2

#### TRANSISTOR AMPLIFIER WITH IMPEDANCE MATCHING TRANSFORMER

#### BACKGROUND OF THE INVENTION

The present invention relates in general to ampifying 5 and more particularly concerns a novel amplifier with high dynamic range and efficiency especially useful in matching both a source impedance and a load impedance while providing r-f amplification over a relatively broad band with a single transformer and single transistor

CATV coaxial cable systems that transmit and amplify television signals use many amplifiers representing a significant cost of the system. To avoid reflections that cause undesirable visible ghosts on a television 15 screen, care is taken to properly terminate the transmission lines. Thus, both the input and output of an amplifier should match that of the transmission line to which it is connected. While techniques for achieving this result are known, conventional prior art circuits involve many components that are relatively costly to acheive this result.

Still another problem arises from the range of signal levels to be amplified. It is difficult to amplify low level signals adequately and avoid overloading the amplifier with high level signals. Furthermore, dissipation of r-f power in amplifying circuit resistors reduces efficiency.

Accordingly, it is an important object of this invention to provide an economical low-noise r-f amplifier 30 with high dynamic range and efficiency capable of conveniently matching both a source impedance and a load impedance while providing good amplification over a relatively broad bandwidth.

preceding object with relatively few components.