## **DAC161S055**

# Precision 16-Bit, Buffered Voltage-Output DAC

# **General Description**

The DAC161S055 is a precision 16-bit, buffered voltage output Digital-to-Analog Converter (DAC) that operates from a 2.7V to 5.25V supply with a separate I/O supply pin that operates down to 1.7V. The on-chip precision output buffer provides rail-to-rail output swing and has a typical settling time of 5  $\mu$ sec. The external voltage reference can be set between 2.5V and  $V_A$  (the analog supply voltage), providing the widest dynamic output range possible.

The 4-wire SPI compatible interface operates at clock rates up to 20 MHz. The part is capable of Diasy Chain and Data Read Back. An on board power-on-reset (POR) circuit ensures the output powers up to a known state.

The DAC161S055 features a power-up value pin (MZB), a load DAC pin (LDACB) and a DAC clear (CLRB) pin. MZB sets the startup output voltage to either GND or mid-scale. LDACB updates the output, allowing multiple DACs to update their outputs simultaneously. CLRB can be used to reset the output signal to the value determined by MZB.

The DAC161S055 has a power-down option that reduces power consumption when the part is not in use. It is available in a 16-lead LLP package.

# **Key Specifications**

Resolution (guaranteed monotonic)16 bits

■ INL ±3 LSB (max)

■ Very low output noise 120 nV/√Hz (typ)

Glitch impulse 7 nV-s (typ)

■ Output settling time 5 µs (typ)

Power consumption 5.5 mW @ 5.25V (max)

#### **Features**

- 16-bit DAC with a two-buffer SPI interface

- Asynchronous load DAC and reset pins

- Compatibility with 1.8V controllers

- Buffered voltage output with rail-to-rail capability

- Wide voltage reference range of +2.5V to V<sub>A</sub>

- Wide temperature range of -40°C to +105°C

- Packaged in a 16-pin LLP

# **Applications**

- Process control

- Automatic test equipment

- Programmable voltage sources

- Communication systems

- Data acquisition

- Industrial PLCs

- Portable battery powered instruments

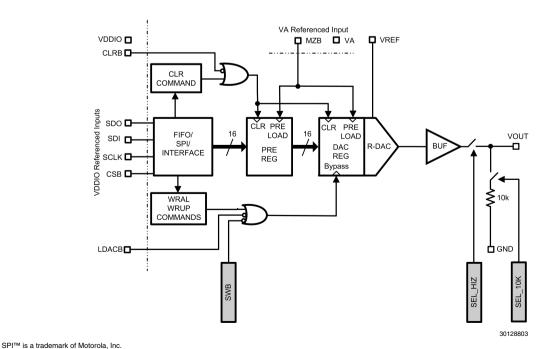

# **Block Diagram**

© 2012 Texas Instruments Incorporated

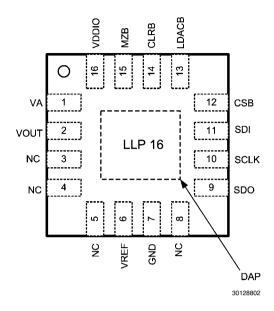

# **Connection Diagram**

# **Pin Descriptions**

| Function and Connection                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI, CLRB, LDACB Supply Voltage.                                                                                                                                      |

| Analog Supply Voltage.                                                                                                                                                |

| DAC output.                                                                                                                                                           |

| Voltage Reference Input.                                                                                                                                              |

| Ground (Analog and Digital).                                                                                                                                          |

| SPI data input .                                                                                                                                                      |

| Chip select signal for SPI interface. On the falling edge of CSB the chip begins to accept data and output data with the SCLK signal. This pin is active low.         |

| Ground (Analog and Digital).  SPI data input .  Chip select signal for SPI interface. Or edge of CSB the chip begins to accept output data with the SCLK signal. This |

| Pin Name | Pin #<br>LLP-16 | ESD Structure | Туре           | Function and Connection                                                                                                                         |

|----------|-----------------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK     | 10              |               | Digital Input  | Serial data clock for SPI Interface.                                                                                                            |

| SDO      | 9               | TO OUT DRIVE  | Digital Output | Data Out for daisy chain or data read back verification.                                                                                        |

| LDACB    | 13              |               | Digital Input  | Load DAC signal. This signal transfers DAC data from the SPI input register to the DAC output register. The signal is active low.               |

| CLRB     | 14              |               | Digital Input  | Asynchronous Reset. If this pin is pulled low, the output will be updated to its power up condition set by the MZB pin. This pin is active low. |

| MZB      | 15              |               | Digital Input  | Power up at Zero/Mid-scale. Tie this pin to GND to power up to Zero or to VA to power up to mid-scale.                                          |

| NC       | 3,4,5,8         |               |                | No connect pins. Connect to GND in board layout will result in the lowest amount of coupled noise.                                              |

| DAP      | DAP             |               |                | Attach die attach paddle to GND for best noise performance.                                                                                     |

# **Ordering Information**

| Order Number    | NS Package Number | Transport Media        |

|-----------------|-------------------|------------------------|

| DAC161S055CISQ  |                   | Tape and Reel: 1000pcs |

| DAC161S055CISQE | SQA16A            | Tape and Reel: 250psc  |

| DAC161S055CISQX |                   | Tape and Reel: 4500pcs |

## Absolute Maximum Ratings (Note 1, Note

2)

If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

Supply Voltage, VA -0.3V to 6.0V Supply Voltage V<sub>DDIO</sub> -0.3V to  $V_{\Delta}+0.3V$ Any pin relative to GND 6V, -0.3V Voltage on MZB or VREF Input Pin -0.3V to  $V_A+0.3V$ Voltage on any other Input Pin (Note -0.3V to  $V_{DDIO}+0.3V$ Voltage on V<sub>OUT</sub> (Note 3) -0.3V to  $V_{\Lambda}+0.3V$ Voltage on SDO (Note 3) -0.3V to  $V_{DDIO}+0.3V$ Input Current at Any Pin (Note 3) 5mA Output Current Source or Sink by Vout 10mA Output Current Source or Sink by 3mA Total Package Input and Output Current 20mA Storage Temperature Range  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$  Junction Temperature  $+150^{\circ}\text{C}$

For soldering specifications:

see product folder at www.national.com and www.national.com/ms/MS/MS-SOLDERING.pdf

# **Recommended Operating**

## Conditions(Note 1, Note 2)

Operating Temperature Range -40°C to +105°C Supply Voltage, V<sub>△</sub> +2.7V to 5.25V Supply Voltage VDDIO +1.7 V to  $V_{\Delta}$ Reference Voltage VREF +2.5V to  $V_A$ Digital Input Voltage 0 to VDDIO **Output Load** 0 to 200 pF Package Thermal Resistance  $\theta_{JA}$  (Note 4) 41°C/W  $\theta_{JC}$ 6.5°C/W

# **Electrical Characteristics**

Charged Device Model (CDM)

**ESD Susceptibility**

Human Body Model

Machine Model

The following specifications apply for  $V_A = 2.7V$  to 5.25V, VDDIO = VA, VREF = 2.5V to VA, RL = 10k to GND,  $C_L = 200$  pF to GND,  $f_{SCLK} = 20$  MHz, input code range 512 to 65023. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}**: all other limits apply to  $T_A = 25^{\circ}$ C, unless otherwise specified.(*Note 1, Note 2, Note 5*)

3000V

250V

1250V

| Symbol      | Parameter                        | Conditions                                                                                  | Min   | Тур   | Max            | Units   |

|-------------|----------------------------------|---------------------------------------------------------------------------------------------|-------|-------|----------------|---------|

| TATIC PERFO | PRMANCE                          |                                                                                             |       | ,     | ,              | -       |

| N           | Resolution                       |                                                                                             | 16    |       |                | Bits    |

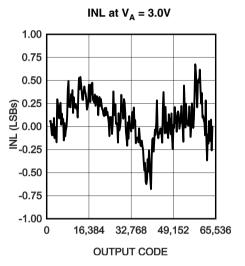

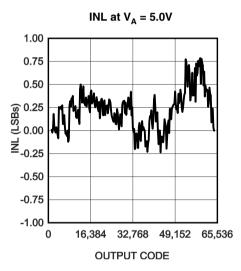

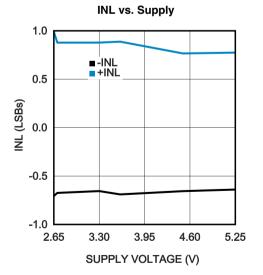

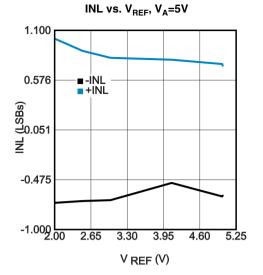

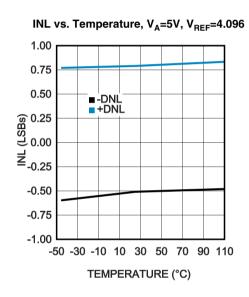

| INL         | Integral Non-Linearity           | No load. From code 512 to Full Scale<br>- 512. V <sub>A</sub> =5V, V <sub>REF</sub> =4.096V |       | ± 1   | ±3             | LSB     |

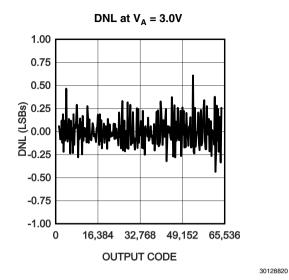

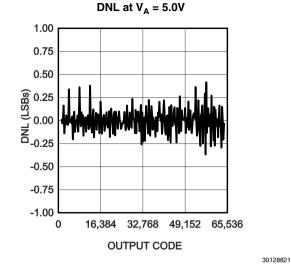

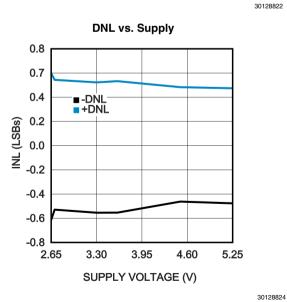

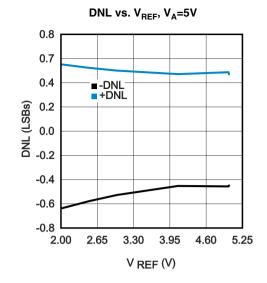

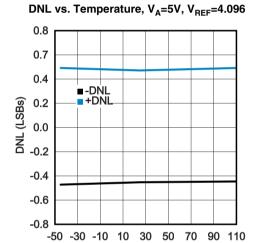

| DNL         | Differential Non-Linearity       | No load. From code 512 to Full Scale<br>- 512. V <sub>A</sub> =5V, V <sub>REF</sub> =4.096V | -1    |       | 1.1            | LSB     |

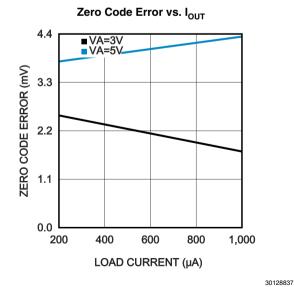

| ZE          | Zero Code Error                  |                                                                                             |       | 4     | 15             | mV      |

| FSE         | Full Scale Error                 |                                                                                             | -15   |       | 15             | mV      |

| OE          | Offset Error                     |                                                                                             | -11   | ±1    | 11             | mV      |

|             | Offset Error Drift               |                                                                                             |       | ±4    |                | μV/°C   |

| GE          | Gain Error                       | No load. From code 512 to Full Scale                                                        |       | ±0.05 |                | % of FS |

|             |                                  | - 512. V <sub>A</sub> =5V, V <sub>REF</sub> =4.096V                                         | -25   |       | 25             | mV      |

|             | Gain Temperature<br>Coefficient  | No load. From code 512 to Full Scale<br>- 512. V <sub>A</sub> =5V, V <sub>REF</sub> =4.096V |       | ± 2   |                | ppm FS. |

| FERENCE IN  | IPUT CHARACTERISTICS             |                                                                                             |       |       | ,              |         |

| $V_{REF}$   | Reference Input Voltage<br>Range | V <sub>A</sub> = 2.7V to 5.25V                                                              | 2.5   |       | V <sub>A</sub> | V       |

|             | Reference Input<br>Impedance     |                                                                                             |       | 12.5  |                | kΩ      |

| NALOG OUTF  | PUT CHARACTERISTICS              |                                                                                             |       | ,     |                |         |

|             | Output Voltage Range             | No load.                                                                                    | 0.015 |       | VA-0.04        | V       |

|             | DC Output Impedance              |                                                                                             |       | 2     |                | Ω       |

| Symbol                              | Parameter                    | Conditions                                                              | Min            | Тур   | Max | Units |

|-------------------------------------|------------------------------|-------------------------------------------------------------------------|----------------|-------|-----|-------|

|                                     |                              | V <sub>A</sub> =3V, I <sub>OUT</sub> =200 μA; V <sub>REF</sub> =2.5     |                | 3     |     |       |

| 700                                 |                              | V <sub>A</sub> =3V, I <sub>OUT</sub> =1mA; V <sub>REF</sub> =2.5        |                | 4     |     | 1 ,,  |

| ZCO                                 | Zero Code Output             | V <sub>A</sub> =5V, I <sub>OUT</sub> =200 μA; V <sub>REF</sub> =4.096   |                | 4     |     | mV    |

|                                     |                              | V <sub>A</sub> =5V, I <sub>OUT</sub> =1mA; V <sub>BEF</sub> =4.096      |                | 4     |     | 1     |

|                                     |                              | V <sub>A</sub> =3V, I <sub>OUT</sub> =200 μA; V <sub>REF</sub> =2.5     |                | 2.495 |     |       |

|                                     |                              | $V_A=3V$ , $I_{OUT}=1$ mA; $V_{REF}=2.5$                                |                | 2.494 |     | †     |

| FSO                                 | Full Scale Output            | V <sub>A</sub> =5V, I <sub>OUT</sub> =200 μA; V <sub>REF</sub> =4.096   |                | 4.091 |     | - V   |

|                                     |                              | $V_A = 5V$ , $I_{OUT} = 1mA$ ; $V_{REF} = 4.096$                        |                | 4.089 |     | †     |

| C <sub>L</sub>                      | Maximum Capacitive Load      | Parallel R = $10K\Omega$                                                |                | 500   |     | pF    |

| ΟĽ                                  | Waximum Gapaonivo Load       | Series R = $50\Omega$                                                   |                | 15    |     | μF    |

|                                     | Minimum Resistive Load       | Series n = 5012                                                         |                | 10    |     | + :   |

| R <sub>L</sub>                      |                              | VA 5V .V 4.000                                                          |                |       |     | kΩ    |

| I <sub>SC</sub>                     | Short Circuit Current        | VA = +5V, V <sub>REF</sub> =4.096                                       |                | 353   |     | mA    |

| t <sub>PU</sub>                     | Power-up Time                | From Power Down Mode                                                    |                | 25    |     | ms    |

|                                     | UT DYNAMIC CHARCTERIS        | 1                                                                       |                | _     |     | 1     |

| SR                                  | Voltage Output Slew Rate     | Positive and negative                                                   |                | 2     |     | V/µs  |

| t <sub>s</sub>                      | Voltage Output Settling Time | 1/4 scale to $3/4$ scale V <sub>REF</sub> = VA = +5V, settle to ±1 LSB. |                | 5     |     | μs    |

|                                     | Digital Feedthrough          | Code 0, all digital inputs from GND to VDDIO                            |                | 1     |     | nV-s  |

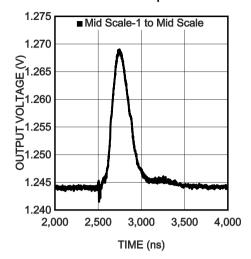

| <u> </u>                            | Major Code Transition        | V <sub>A</sub> =5V, V <sub>REF</sub> =2.5V. Transition from             |                | 7     |     | nV-s  |

|                                     | Analog Glitch Impulse        | mid-scale - 1LSB to mid-scale.                                          |                |       |     |       |

|                                     | Output Noise                 | Spot noise at 20 kHz                                                    |                | 120   |     | nV/√H |

|                                     | Integrated Output Noise      | 1Hz to 10 kHz                                                           |                | 18    |     | μV    |

| GITAL INPUT                         | CHARACTERISTICS              |                                                                         |                |       |     | •     |

| I <sub>IN</sub>                     | Input Current                |                                                                         |                |       | ±1  | μA    |

| V <sub>IL</sub>                     | Input Low Voltage            | VDDIO=5V                                                                |                |       | 0.8 |       |

|                                     |                              | VDDIO=3V                                                                |                |       | 0.8 | 7 v   |

|                                     |                              | VDDIO=1.8V                                                              |                |       | 0.4 | 1     |

|                                     |                              | VDDIO=5V                                                                | 2.1            |       |     |       |

| $V_{IH}$                            | Input High Voltage           | VDDIO=3V                                                                | 2.1            |       |     | 7 v   |

|                                     |                              | VDDIO=1.8V                                                              | 1.4            |       |     | 1     |

| V <sub>ILMZB</sub>                  | MZB Input Low Voltage        | VA=5V                                                                   |                |       | 0.8 | V     |

|                                     |                              | VA=3V                                                                   |                |       | 0.8 | V     |

| M                                   | MZD have tillink Valtage     | VA=5V                                                                   | 2.1            |       |     | V     |

| $V_{IHMZB}$                         | MZB Input High Voltage       | VA=3V                                                                   | 2.1            |       |     | V     |

| C <sub>IN</sub>                     | Input Capacitance            |                                                                         |                | 4     |     | pF    |

|                                     | UT CHARACTERISTICS           |                                                                         |                |       |     |       |

| V <sub>OL</sub>                     | Output Low Voltage           | Isink=200 μA; VDDIO>3V                                                  |                |       | 400 | mV    |

|                                     |                              | lsink=2mA;VDDIO>3V                                                      |                |       | 400 |       |

|                                     |                              | Isink=200 μA; VDDIO=1.8V                                                |                |       | 400 |       |

|                                     |                              | Isink=2mA;VDDIO=1.8V                                                    |                |       | 400 | 1     |

| $V_{OH}$                            | Output High Voltage          | lsink=200 μA; VDDIO>3V                                                  | VDDIO -<br>0.2 |       |     | V     |

|                                     |                              | Isink=2mA;VDDIO>3V                                                      | VDDIO -<br>0.2 |       |     | ]     |

|                                     |                              | Isink=200 μA; VDDIO=1.8V                                                | VDDIO -<br>0.2 |       |     |       |

|                                     |                              | Isink=2mA;VDDIO=1.8V                                                    | 1.15           |       |     | 1     |

| I <sub>OZH</sub> , I <sub>OZL</sub> | TRI-STATE Leakage            |                                                                         |                | <1n   | ±1µ | А     |

|                                     | Current                      |                                                                         |                |       |     |       |

| Symbol            | Parameter                          | Conditions                                                      | Min | Тур  | Max  | Units |

|-------------------|------------------------------------|-----------------------------------------------------------------|-----|------|------|-------|

| C <sub>OUT</sub>  | TRI-STATE Output                   |                                                                 |     | 4    |      | pF    |

|                   | Capacitance                        |                                                                 |     |      |      |       |

| WER REQUI         | REMENTS                            |                                                                 |     |      |      |       |

| V <sub>A</sub>    | Analog Supply Voltage<br>Range     |                                                                 | 2.7 |      | 5.25 | V     |

| VDDIO             | Digital Supply Voltage<br>Range    |                                                                 | 1.7 |      | VA   | V     |

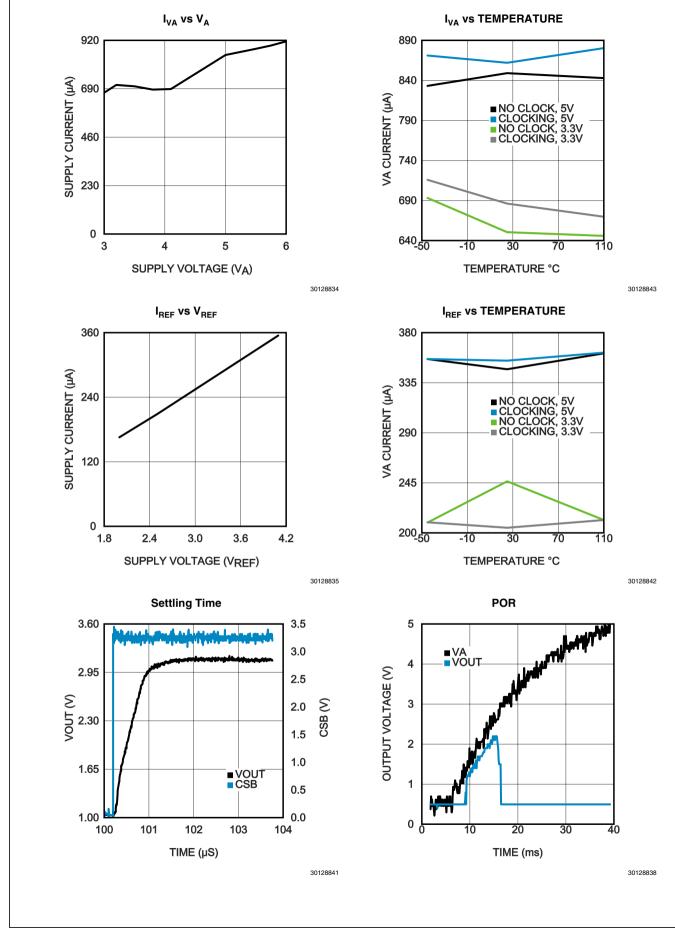

| I <sub>VA</sub>   | VA Supply Current                  | No load. SCLK Idle. All digital inputs at GND or VDDIO. VA=5V   |     | 0.75 | 1    | mA    |

|                   |                                    | No load. SCLK Idle. All digital inputs at GND or VDDIO. VA=3.3V |     | 0.62 | 1    | mA    |

| I <sub>REF</sub>  | Reference Current                  |                                                                 |     |      | 350  |       |

| I <sub>PDVA</sub> | VA Power Down Supply<br>Current    | All digital inputs at GND or VDDIO                              |     | 0.5  | 3    |       |

| I <sub>PDVO</sub> | VDDIO Power Down<br>Supply Current | All digital inputs at GND or VDDIO                              |     |      | 1    | μA    |

| I <sub>PDVR</sub> | VREF Power Down Supply<br>Current  |                                                                 |     |      | 1    | ]     |

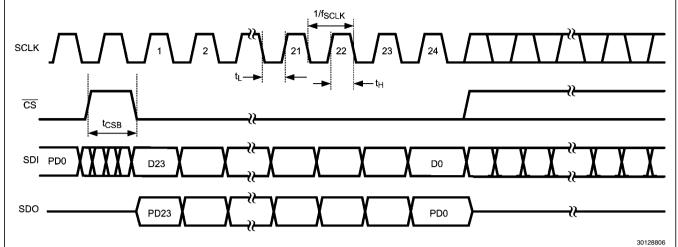

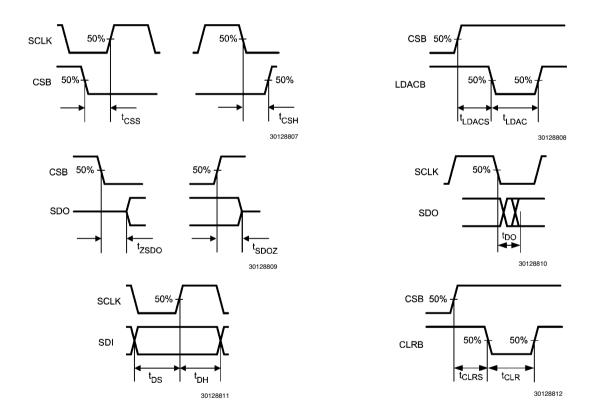

# **Digital Interface Timing Characteristics**

These specifications apply for  $V_A = 2.7V$  to 5.25V, VDDIO = 1.7V to  $V_A$ , CL = 200 pF. **Boldface limits apply for T\_A = -40^{\circ}C to 105°C**. All other limits apply to  $T_A = 25^{\circ}C$ , unless otherwise specified.

| Symbol             | DI Parameter Conditions                           |                                               | Min | Тур | Max | Units |

|--------------------|---------------------------------------------------|-----------------------------------------------|-----|-----|-----|-------|

| f <sub>SCLK</sub>  | SCLK Frequency                                    | VDDIO=1.7V to 2.7V                            | 0   |     | 10  | MHz   |

| SOLK Frequency     |                                                   | VDDIO=2.7V to 5.25V                           | 0   |     | 20  |       |

| t <sub>H</sub>     | SCLK High Time                                    |                                               | 15  | 25  |     |       |

| t <sub>L</sub>     | SCLK Low Time                                     |                                               | 20  | 25  |     | ]     |

| t <sub>CSB</sub>   | CCD Lligh Dulg a width                            | VDDIO=1.7V to 2.7V                            |     | 75  |     |       |

|                    | CSB High Pulse width                              | VDDIO=2.7V to 5.25V                           |     | 40  |     |       |

| t <sub>CSS</sub>   | CSB Set-up Time Prior to SCLK Rising edge         |                                               | 10  |     |     |       |

| t <sub>CSH</sub>   | CSB Hold Time after the 24th Falling Edge of SCLK |                                               |     | 0   |     |       |

| t <sub>zspo</sub>  | CSB Falling Edge to SDO                           | VDDIO=1.8V                                    |     | 40  |     | ]     |

|                    | Valid                                             | VDDIO=3V                                      |     | 10  |     |       |

|                    |                                                   | VDDIO=5V                                      |     | 6   |     |       |

| t <sub>SDOZ</sub>  | CSB Rising Edge to SDO                            | VDDIO=1.8V                                    |     | 75  |     |       |

|                    | HiZ                                               | VDDIO=3V                                      |     | 40  |     |       |

|                    |                                                   | VDDIO=5V                                      |     | 27  |     | ns    |

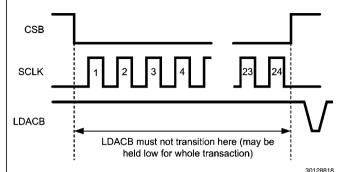

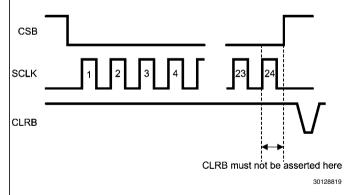

| t <sub>CLRS</sub>  | CSB Rising Edge to CLRB Falling Edge              | CLRB must not transition anytime CSB is low.  |     | 5   |     |       |

| t <sub>LDACS</sub> | CSB Rising Edge to LDACB Falling Edge             | LDACB must not transition anytime CSB is low. |     | 5   |     |       |

| t <sub>LDAC</sub>  | LDACB Low Time                                    |                                               | 10  | 2.5 |     |       |

| t <sub>CLR</sub>   | CLRB Low Time                                     |                                               | 10  | 2.5 |     |       |

| t <sub>DS</sub>    | SDI Data Set-up Time prior to SCLK Rising Edge    |                                               |     | 10  |     |       |

| t <sub>DH</sub>    | SDI Data Hold Time after<br>SCLK Rising Edge      |                                               |     | 0   |     |       |

| t <sub>DO</sub>    | SDO Output Data Valid                             | VDDIO=1.7                                     |     |     | 62  | ]     |

|                    |                                                   | VDDIO=3.3                                     |     |     | 25  |       |

|                    | 1                                                 | VDDIO=5                                       |     |     | 15  |       |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The recommended Operating Conditions at which the device is functional and the device should not be operated beyond such conditions.

Note 2: The Electrical characteristics tables list guaranteed specifications under the listed Recommended Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

**Note 3:** When the input voltage  $(V_1)$  at any pin exceeds the power supplies  $(V_1 < \text{GND or } V_1 > \text{VDD})$  the current at that pin must be limited to 5mA and  $V_1$  has to be within the Absolute Maximum Rating for that pin. The 20mA package input current rating limits the number of pins that can safely exceed the power supplies with current flow to four.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$  and  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ .

Note 5: Typical values represent most likely parametric norms at specific conditions (Example VA; specific temperature) and at the recommended Operating Conditions at the time of product characterizations and are not guaranteed.

Note 6: Specification is guaranteed by characterization and is not tested in production.

Note 7: Specification is guaranteed by design and is not tested in production.

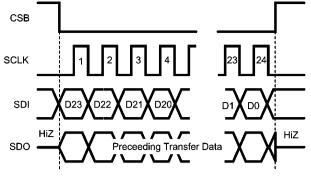

# **Timing Diagrams**

FIGURE 1. DAC161S055 Input/Output Waveforms

FIGURE 2. Timing Parameter Specifics

## **Transfer Characteristics**

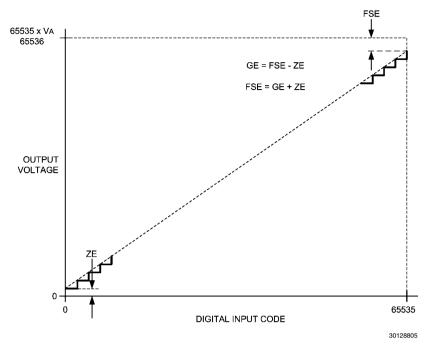

FIGURE 3. Input/Output Transfer Characteristic

## **Specification Definitions**

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB, which is  $V_{\text{RFF}}$  / 65536.

**DIGITAL FEEDTHROUGH** is a measure of the energy injected into the analog output of the DAC from the digital inputs when the DAC outputs are not updated. It is measured with a full-scale code change on the data bus.

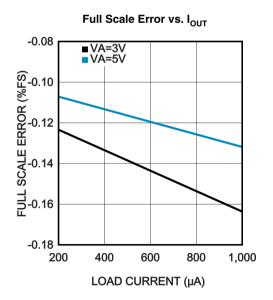

**FULL-SCALE ERROR** is the difference between the actual output voltage with a full scale code (FFFh) loaded into the DAC and the value of V<sub>RFF</sub> x 65535 / 65536.

**GAIN ERROR** is the deviation from the ideal slope of the transfer function. It can be calculated from Zero and Full-Scale Errors as GE = FSE - ZE, where GE is Gain error, FSE is Full-Scale Error and ZE is Zero Error.

**GLITCH IMPULSE** is the energy injected into the analog output when the input code to the DAC register changes. It is specified as the area of the glitch in nanovolt-seconds.

**INTEGRAL NON\_LINEARITY (INL)** is a measure of the deviation of each individual code from a straight line through the input to output transfer function. The deviation of any given code from this straight line is measured from the center of that code value. The end point method is used. INL for this product is specified over a limited range, per the Electrical Tables.

**LEAST SIGNIFICANT BIT (MSB)** is the bit that has the smallest value or weight of all bits in a word. This value is LSB =  $V_{REF}$  /  $2^n$  where  $V_{REF}$  is the reference voltage for this product, and "n" is the DAC resolution in bits, which is 16 for the DAC161S055.

**MAXIMUM LOAD CAPACITANCE** is the maximum capacitance that can be driven by the DAC with output stability maintained, although some ringing may be present.

**MONOTONICITY** is the condition of being monotonic, where the DAC output never decreases when the input code increases.

MOST SIGNIFICANT BIT (MSB) is the bit that has the largest value or weight of all bits in a word. Its value is 1/2 of V<sub>REF</sub>-

**OFFSET ERROR** is the difference between zero voltage and a where a straight line fit to the actual transfer function intersects the vaxis.

SETTLING TIME is the time for the output to settle to within 1 LSB of the final value after the input code is updated.

**WAKE-UP TIME** is the time for the output to recover after the device is commanded to the active mode from any of the power down modes.

ZERO CODE ERROR is the output error, or voltage, present at the DAC output after a code of 0000h has been entered.

# **Typical Performance Characteristics**

www.ti.com 10

30128825

30128823

TEMPERATURE (°C)

## **5V Glitch Response**

30128839

# 1.0 Functional Description

#### 1.1 DAC ARCHITECTURE OVERVIEW

The DAC161S055 uses a resistor array to convert the input code to an analog signal, which in turn is buffered by the rail-to-rail output amplifier. The resistor array is factory trimmed to achieve 16-bit accuracy.

An SPI interface shifts the input codes into the device. The acquired input code is stored in the PREREG register. After the input code is transferred to the DACREG register it affects the state of the resistor array and the output level of the DAC. The transfer can be initiated by the type of write command used, by a software LDAC command or by the state of the LDACB pin.

The user can control the power up state of the output using the MZB pin and the power down state of the output using the CONFIG register. Additionally, there are external pins and CONFIG register bits that also control clearing the DAC.

NOTE: Although the DAC161S055 is a single channel device, the instruction set is for multichannel DACs. The user must address channel 0 (A2,A1,A0={000}).

#### **1.2 OUTPUT AMPLIFIER**

The output buffer amplifier is a rail to rail type which buffers the signal produced by the resistor array and drives the external load. All amplifiers, including rail to rail amplifiers, exhibit a loss of linearity as the output nears the power rails (in this case GND and  $V_A$ ). Thus the linearity of the part is specified over less than the full output range. The user can program the CONFIG register to power down the amplifier and either place it in the high impedance state (HiZ), or have the output terminated by an internal 10 k $\Omega$  pull-down resistor.

#### 1.3 REFERENCE

An external reference source is required to produce an output. The reference input is not internally buffered and presents a resistive load to the external source. Loading presented by the VREF pin varies by about 12.5% depending on the input code. Thus a low impedance reference should be used for best results.

#### 1.4 SERIAL INTERFACE

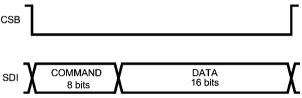

The 4-wire interface is compatible with SPI, QSPI and MI-CROWIRE, as well as most DSPs. See the *Timing Diagrams* for timing information about the read and write sequences. The serial interface is the four signals CSB, SCLK, SDI and SDO.

A bus transaction is initiated by the falling edge of the CSB. Once CSB is low, the input data is sampled at the SDI pin by the rising edge of the SCLK. The output data is put out on the SDO pin on the falling edge of SCLK. At least 24 SCLK cycles are required for a valid transfer to occur. If CSB is raised before 24th rising edge of the SCLK, the transfer is aborted. If the CSB is held low after the 24th falling edge of the SCLK, the data will continue to flow through the FIFO and out the SDO pin. Once CSB transitions high, the internal controller will decode the most recent 24 bits that were received before the rising edge of CSB. The DAC will then change state depending on the instruction sent and the state of the LDACB pin.

3012881

The acquired data is shifted into an internal 24 bit shift register (MSB first) which is configured as a 24 bit deep FIFO. As the data is being shifted into the FIFO via the SDI pin, the prior contents of the register are being shifted out through the SDO output. While CSB is high, SDO is in a high-Z state. At the falling edge of CSB, SDO presents the MSB of the data present in the shift register. SDO is updated on every subsequent falling edge of SCLK (note — the first SDO transition will happen on the first falling edge AFTER the first rising edge of SCLK when CSB is low).

The 24 bits of data contained in the FIFO are interpreted as an 8 bit COMMAND word followed by 16 bits of DATA. The general format of the 24 bit data stream is shown below. The full Instruction Set is tabulated in Section 1.12 INSTRUCTION SET.

30128814

#### 1.4.1 SPI Write

SPI write operation is the simplest transaction available to the user. There is no handshaking between master and the slave (DAC161S055), and the master is the source of all signals required for communication: SCLK, CSB, SDI. The format of the data transfer is described in the section 1.4. The user instruction set is shown in Section 1.12 INSTRUCTION SET.

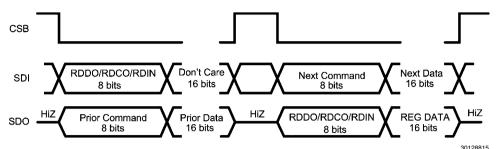

#### 1.4.2 SPI Read

The read operation requires all 4 wires of the SPI interface: SCLK, SCB, SDI, SDO. The simplest READ operation occurs automatically during any valid transaction on the SPI bus since SDO pin of DAC161S055 always shifts out the contents of the internal FIFO. Therefore the user can verify the data being shifted in to the FIFO by initiating another transaction and acquiring data at SDO. This allows for verification of the FIFO contents only.

The 3 internal registers (PREREG, DACREG, CONFIG) can be accessed by the user through the Register Read commands: RDDO, RDIN, RDCO respectively (see Section 1.12 INSTRUCTION SET). These operations require 2 SPI transaction to recover the register data. The first transaction shifts in the Register Read command; an 8 bit command byte followed by 16 bit "dummy" data. The Register Read command will cause the transfer of contents of the internal register into the FIFO. The second transaction will shift out the FIFO contents; an 8 bit command byte (which is a copy of previous

transaction) followed by the register data. The Register Read operation is shown in the figure below.

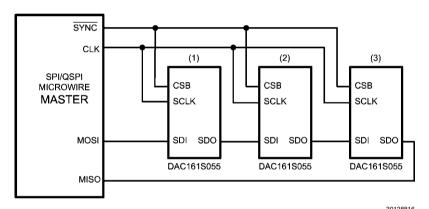

#### 1.4.2 SPI Daisy Chain

It is possible to control multiple DACs or other SPI devices with a single master equipped with one SPI interface. This is accomplished by connecting the DACs in a Daisy Chain. The scheme is depicted in the figure below. An arbitrary length of the chain and an arbitrary number of control bits for other devices in the chain is possible since individual DAC devices do not count the data bits shifted in. Instead, they wait to decode the contents of their respective shift registers until CSB is raised high.

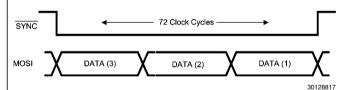

A typical bus cycle for this scheme is initiated by the falling CSB. After the 24 SCLK cycles new data starts to appear at the SDO pin of the first device in the chain, and starts shifting into the second device. After 72 SCLK cycles following the falling CSB edge, all three devices in this example will contain new data in their input shift registers. Raising CSB will begin the process of decoding data in each DAC. When in the Daisy Chain the full READ and WRITE capability of every device is maintained.

A sample of SPI data transfer appropriate for a 3 DAC Daisy Chain is shown in the figure below.

#### 1.5 POWER-UP DEFAULT OUTPUT

It is possible to power up the DAC with the output either at GND or midscale. This functionality is achieved by connecting the MZB pin either to GND or to VA (note, the MZB pin is referenced to VA, not VDDIO). Usually this function is hardwired in the application, but can also be controlled by a GPIO pin of the  $\mu$ C. To power up with output at zero, tie the MZB pin low. To power up with output at midscale, tie MZB high. The MZB pin is level sensitive.

#### 1.6 CHANGING DAC OUTPUT

There are multiple different ways to affect the DAC output. The CONFIG register can be changed so that a write to the PREREG is seen instantly at the output. The LDAC function or LDACB pin updates the output instantly. Finally, the type of write command (WRUP, WRAL, WR) can affect if the output updates instantly or not.

#### 1.6.1 Write-Through and Write-Block Modes

Using the SWB bit of the CONFIG register, the user can set the part in **WRITE-BLOCK** or **WRITE-THROUGH** mode.

If the DAC channel is configured in the WRITE-BLOCK mode (SWB=0, default), the DAC input DATA is held in the PRE-REG until the controller forces the transfer of DATA from PREREG to DACREG register. Only DATA in DACREG register is converted to the equivalent analog output. The transfer from PREREG into DACREG can be forced by both software and hardware LDAC commands. The Data Writing commands WRUP and WRAL update both PREREG and DACREG at the same time regardless of the channel mode. WRITE-BLOCK mode is used in multi device or multi channel applications. A user can preload all DAC channels with desired data, in multiple SPI transactions, and then issue a single software LDAC command (or toggle the LDACB pin) to simultaneously update all analog outputs.

If the DAC channel is configured in **WRITE-THROUGH** mode (SWB=1) the controller updates both PREREG and DACREG registers simultaneously. Therefore in WRITE-THROUGH mode the channel output is updated as soon as the SPI transfer is completed i.e. upon the rising edge of CSB.

#### 1.6.2 LDAC Function

The LDACB (Load DAC) pin provides a easy way to synchronize several DACs and update the output without any SPI latency. If the LDACB is asserted low, the content of the PRE-

REG register is instantaneously moved into the DACREG register. The LDACB pin is level sensitive. If the LDACB pin is held low continuously, the DAC output will update as soon as the CSB pin goes high.

The DAC Configuration command LDAC (see Section 1.12 INSTRUCTION SET below) will also update the DAC output as soon as it is received. The effect of hardware LDACB or software LDAC is the same i.e. data is transferred from the PREREG to DACREG and output of the DAC is updated.

#### 1.6.3 Write Commands

There are three write commands available in the DAC command set. Issuing a WR command causes the DAC to update either the PREREG or the DACREG depending on the setting of the SWB bit (see Section 1.6.1 Write-Through and Write-Block Modes). Issuing a WRUP command causes the specified channels output (for multiple channel parts) to update immediately, regardless of the SWB bit setting. Issuing a WRAL command causes all channels (for multiple channel parts) to update immediately with the same data, regardless of the SWB bit setting.

#### **1.8 CLEAR FUNCTION**

The CLRB pin provides a easy way to reset the DAC161S055 output. If the CLRB pin goes low, VOUT instantaneously slews to the value indicated by the MZB pin, either zero or midscale. The CLRB pin is level sensitive.

Clear function can also be accessed via the software instruction CLR, see Section 1.12 INSTRUCTION SET below. The effect of hardware CLRB or software CLR is the same.

#### 1.9 POWER ON RESET

An on-chip power on reset circuit (POR) ensures that the DAC always powers on in the same state. The registers will be loaded with the defaults shown in Section 1.12 INSTRUCTION SET. The output state will be controlled by the state of the MZB pin.

#### 1.10 POWER DOWN

Power down is achieved by writing the PD instruction and setting the appropriate bit to a logic '1'. In the PD command, it is possible to specify if the output is left in a high impedance (HIZ) state or if it is pulled to GND through a 10K resistor. During power down, the output amplifier is disabled and the resistor ladder is disconnected from Vref. The SPI interface remains active. To exit power down, write the PD command again, setting the appropriate bit to a logic '0'. Note that the SPI interface and the registers are all active during power down.

#### 1.11 INTERNAL REGISTERS

There are 3 registers that are accessible to the user. The data registers (PREREG and DACREG) are both readable and writable from the command set. The CONFIG register is only

readable from the command set. Bits in the CONFIG register are set by the commands detailed in Section 1.12 INSTRUCTION SET.

|       |                      | PRE                                                                                                     | REG: DAC                                                                                                                                                                                           | Preload D                                                                                                                                                                                                                                                           | ata Regist                                                                                                                                                                                                                                                                                                                           | er(16Bits)                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                |

|-------|----------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W   | R/W                  | R/W                                                                                                     | R/W                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                            |

| PRD15 | PRD14                | PRD13                                                                                                   | PRD12                                                                                                                                                                                              | PRD11                                                                                                                                                                                                                                                               | PRD10                                                                                                                                                                                                                                                                                                                                | PRD9                                                                                                                                                                                                                                                                                                                                                                                                  | PRD8                                                                                                                                                                                                                                                                                                                                                                           |

| Bit15 | Bit14                | Bit13                                                                                                   | Bit12                                                                                                                                                                                              | Bit11                                                                                                                                                                                                                                                               | Bit10                                                                                                                                                                                                                                                                                                                                | Bit9                                                                                                                                                                                                                                                                                                                                                                                                  | Bit8                                                                                                                                                                                                                                                                                                                                                                           |

|       |                      |                                                                                                         |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                |

| R/w   | R/W                  | R/W                                                                                                     | R/W                                                                                                                                                                                                | R/W                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                                                                                                            |

| PRD7  | PRD6                 | PRD5                                                                                                    | PRD4                                                                                                                                                                                               | PRD3                                                                                                                                                                                                                                                                | PRD2                                                                                                                                                                                                                                                                                                                                 | PRD1                                                                                                                                                                                                                                                                                                                                                                                                  | PRD0                                                                                                                                                                                                                                                                                                                                                                           |

| Bit7  | Bit6                 | Bit5                                                                                                    | Bit4                                                                                                                                                                                               | Bit3                                                                                                                                                                                                                                                                | Bit2                                                                                                                                                                                                                                                                                                                                 | Bit1                                                                                                                                                                                                                                                                                                                                                                                                  | Bit0                                                                                                                                                                                                                                                                                                                                                                           |

|       | PRD15 Bit15 R/w PRD7 | PRD15         PRD14           Bit15         Bit14           R/w         R/W           PRD7         PRD6 | R/W         R/W         R/W           PRD15         PRD14         PRD13           Bit15         Bit14         Bit13           R/w         R/W         R/W           PRD7         PRD6         PRD5 | R/W         R/W         R/W         R/W           PRD15         PRD14         PRD13         PRD12           Bit15         Bit14         Bit13         Bit12           R/w         R/W         R/W         R/W           PRD7         PRD6         PRD5         PRD4 | R/W         R/W         R/W         R/W         R/W           PRD15         PRD14         PRD13         PRD12         PRD11           Bit15         Bit14         Bit13         Bit12         Bit11           R/W         R/W         R/W         R/W         R/W           PRD7         PRD6         PRD5         PRD4         PRD3 | R/W         R/W         R/W         R/W         R/W         R/W           PRD15         PRD14         PRD13         PRD12         PRD11         PRD10           Bit15         Bit14         Bit13         Bit12         Bit11         Bit10           R/w         R/W         R/W         R/W         R/W         R/W           PRD7         PRD6         PRD5         PRD4         PRD3         PRD2 | PRD15         PRD14         PRD13         PRD12         PRD11         PRD10         PRD9           Bit15         Bit14         Bit13         Bit12         Bit11         Bit10         Bit9           R/w         R/W         R/W         R/W         R/W         R/W         R/W           PRD7         PRD6         PRD5         PRD4         PRD3         PRD2         PRD1 |

Bit15-0: 16 bit data word to be converted. Bit 15 has a weight of 1/2\*Vref. Bit 0 has a weight of Vref/2^16.

|     |       |       | DAC   | CREG: DAG | C Output D | ata Regist | er(16Bits) |      |

|-----|-------|-------|-------|-----------|------------|------------|------------|------|

|     | R/W   | R/W   | R/W   | R/W       | R/W        | R/W        | R/W        | R/W  |

| MSB | IND15 | IND14 | IND13 | IND12     | IND11      | IND10      | IND9       | IND8 |

|     | Bit15 | Bit14 | Bit13 | Bit12     | Bit11      | Bit10      | Bit9       | Bit8 |

|     |       |       |       |           |            |            |            |      |

|     | R/w   | R/W   | R/W   | R/W       | R/W        | R/W        | R/W        | R/W  |

| LSB | IND7  | IND6  | IND5  | IND4      | IND3       | IND2       | IND1       | IND0 |

|     | Bit7  | Bit6  | Bit5  | Bit4      | Bit3       | Bit2       | Bit1       | Bit0 |

| ĺ   |       |       |       |           |            |            |            |      |

Bit15-0: 16 bit data word to be converter. Bit 15 has a weight of 1/2\*Vref. Bit 0 has a weight of Vref/2^16.

|     |      |      | CONFIG: | <b>DAC Conf</b> | iguration F | Reporting | Register (8 | Bits)   |

|-----|------|------|---------|-----------------|-------------|-----------|-------------|---------|

|     | R    | R    | R       | R               | R           | R         | R           | R       |

| MSB | _    | _    | _       | _               | _           | SWB       | SEL_10K     | SEL_HIZ |

|     | Bit7 | Bit6 | Bit5    | Bit4            | Bit3        | Bit2      | Bit1        | Bit0    |

Bit7–3: Reserved. Read value is undefined and should be discarded.

Bit2: SWB: Set Write Block bit

0: Channel is in WRITE THROUGH mode.

1: Channel is in WRITE BLOCK mode.

Bit1: 0: Channel is either active or SEL\_HIZ is set.

1: Channel is powered down and output is terminated by a 10K resistor to GND.

Bit0: 0: Channel is either active or SEL\_10K is set.

1: Channel is powered down and output is in high impedance state.

#### 1.12 INSTRUCTION SET

The instruction set for the DAC161S055 is common to the family of single and multi channel devices (DAC16xS055). The DAC161S055 has only a single channel — Channel 0.

NOTE: DATA WRITING and REGISTER READING instructions encode the channel address as a binary triplet (A2,A1,A0) as the last three LSBs of the command byte. DAC CONFIGURATION instructions encode the channel selection by a bit set in the data bytes. For example, when executing the LDAC instruction a payload of {0100 0001} in the least significant byte of the instruction indicates channels 6 and 0 are targeted.

| MNEMONIC              |       | ٥ | Command Byte[7:0] | Jand | Byte         | [7:0] |     |    | DATA[15:8]    | DATA [7:0]                        | Description                                                                                                                                                                             | DEFAULT |

|-----------------------|-------|---|-------------------|------|--------------|-------|-----|----|---------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| DAC Configuration     | ation |   |                   |      |              |       |     |    |               |                                   |                                                                                                                                                                                         |         |

| NOP                   | 0     | 0 | 0                 | 0    | 0            | 0     | 0   | 0  | XXXX XXXX     | xxx xxxx                          | No Operation                                                                                                                                                                            |         |

| CLR                   | 0     | 0 | 0                 | 0    | 0            | 0     | 0   | -  | xxx xxxx      | xxxx xxxx                         | Clear internal registers, return to Power-Up<br>default state                                                                                                                           |         |

| LDAC                  | 0     | 0 | 0                 | -    | -            | 0     | 0   | 0  | XXXX XXXX     | CHANNEL[7:0]                      | Software LOAD DAC. A '1' causes data stored in the specified channel's PREREG to be transferred to DACREG and the output updated.                                                       |         |

| SWB                   | 0     | 0 | -                 | 0    | <del>-</del> | 0     | 0   | 0  | XXXX XXXX     | CHANNEL[7:0]                      | Set WRITE BLOCK or WRITE THROUGH for the 00FFh selected channels.  0: WRITE THROUGH 1: WRITE BLOCK                                                                                      | 00FFh   |

| Q                     | 0     | 0 | -                 | -    | 0            | 0     | 0   | 0  | CHANNEL[7:0]  | CHANNEL[7:0]                      | Sets SEL_10K or SEL_HIZ. Upper 8 bits PD Hi-Z; 0000h Lower 8-bits PD 10K; if both are 1's; PD -> 10K 1: Upper 8 bits: SEL_HIZ 1: Lower 8 bits: SEL_10K 1: Both upper and lower: SEL_10K | 40000   |

| Data Writing          |       |   | 1                 |      |              |       |     |    |               |                                   |                                                                                                                                                                                         |         |

| WR                    | 0     | 0 | 0                 | 0    | -            | A2    | A1  | A0 | DACDATA[15:8] | DACDATA[7:0]                      | Write to specified channel. WRITE BLOCK or WRITE TRHOUGH setting controls destination register (PREREG or DACREG).                                                                      |         |

| WRUP                  | 0     | 0 | 0                 | -    | 0            | A2    | F A | A0 | DACDATA[15:8] | DACDATA[7:0]                      | Update specified channel's DACREG and PREREG regardless of WRITE BLOCK or WRITE THROUGH setting.                                                                                        |         |

| WRAL                  | 0     | 0 | -                 | 0    | 0            | 0     | 0   | 0  | DACDATA[15:8] | DACDATA[7:0]                      | Update all channel's DACREG and PREREG regardless of WRITE BLOCK or WRITE THROUGH setting.                                                                                              |         |

| Register Reading      | ling  |   |                   |      |              |       |     |    |               |                                   |                                                                                                                                                                                         |         |

| <reserved></reserved> | _     | 0 | 0                 | 0    | 0            | ×     | ×   | ×  |               |                                   | <reserved></reserved>                                                                                                                                                                   |         |

| RDDO                  | 1     | 0 | 0                 | 0    | -            | A2    | A1  | A0 | DACDATA[15:8] | DACDATA[7:0]                      | Read PREREG register.                                                                                                                                                                   |         |

| RDCO                  | -     | 0 | 0                 | -    | 0            | A2    | A1  | AO | 0000 0000     | 0000<br>0,swb,sel_10k,sel_hi<br>2 | Read CONFIG register.                                                                                                                                                                   | 0004h   |

| RDIN                  | -     | 0 | 0                 | -    | -            | A2    | P4  | A0 | DACDATA[15:8] | DACDATA[7:0]                      | Read DACREG register.                                                                                                                                                                   |         |

# 2.0 Applications Information

#### 2.1 SAMPLE INSTRUCTION SEQUENCE

The following table shows an example instruction sequence to illustrate the usage of different modes of operation of the DAC. This sequence is for a one channel DAC.

| Step | Instruction | 8-bit Command | 16 bit Payload      | Comments                                                                                                                                       |

|------|-------------|---------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CLR         | 0000 0001     | 0000 0000 0000 0000 | Clear device - return to Power-Up Default State                                                                                                |

| 2    | WR          | 0000 1000     | 0100 0000 0000 0000 | Write ¼ FS into channel 0. Since device by default is in WRITE-BLOCK mode the data will be written into PREREG, and DAC output will not update |

| 3    | LDAC        | 0001 1000     | xxxx xxxx 0000 0001 | Issue LDAC command to channel 0. Data is transferred from PREREG into DACREG and DAC output updates to ¼ FS                                    |

| 4    | SWB         | 0010 1000     | xxxx xxxx 1111 1110 | Set channels 1 to 7 to WRITE-BLOCK mode, and channel 0 to WRITE-THROUGH mode                                                                   |

| 5    | WR          | 0000 1000     | 1111 1111 1111 1111 | DAC output updates immediately to FS since the channel is set to write through mode.                                                           |

| 6    | PD          | 0011 0000     | 0000 0001 0000 0000 | Power down the device, and set the channel 0  DAC output to the HIZ state                                                                      |

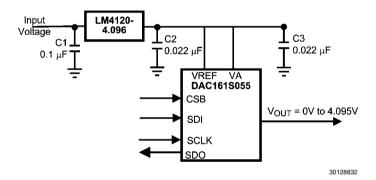

#### 2.2 USING REFERENCES AS POWER SUPPLIES

Although the DAC has a separate reference and analog power pin, it is still possible to use a reference to drive both. This arrangement will avoid a separate voltage regulator for  $V_A$

and will provide a more stable voltage source. The LM4140 has an initial accuracy of 0.1%, is capable of driving 8mA and comes in a 4.096V version. Bypassing both the input and the output will improve noise performance.

FIGURE 4. Using the LM4120 as a power supply

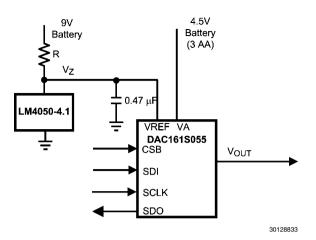

#### 2.3 A LOW NOISE EXAMPLE

A LM4050 powered off of a battery is a good choice for very low noise prototype circuits. The minimum value for R must be chosen so that the LM4050 does not draw more than its

15mA rating. Note the largest current through the LM4050 will occur when the DAC is shutdown. The maximum resistor value must allow the LM4050 to draw more than its minimum current for regulation plus the maximum  $V_{\mathsf{RFF}}$  current.

FIGURE 5. Using the LM4050 in a low noise circuit

#### 2.4 LAYOUT, GROUNDING AND BYPASSING

For best accuracy and minimum noise, the printed circuit board containing the DAC should have separate analog and digital areas. These areas are defined by the locations of the analog and digital power planes. Both power planes should be in the same board layer. There should be a single ground plane. Frequently a single ground plane design will utilize a fencing technique to prevent the mixing of analog and digital ground currents. Separate ground planes should only be used if the fencing technique proves inadequate. The separate ground planes must be connected in a single place, preferably near the DAC. Special care is required to guarantee that digital signals with fast edge rates do not pass over split ground planes. The fast digital signals must always have a continuous return path below their traces.

When possible, the DAC power supply should be bypassed with a  $10\mu F$  and a  $0.1\mu F$  capacitor placed as close as possible

to the device with the  $0.1\mu F$  closest to the supply pin. The  $10\mu F$  capacitor should be a tantalum type and the  $0.1\mu F$  capacitor should be a low ESL, low ESR type. Sometime, the loading requirements of the regulator driving the DAC do not allow such capacitance to be placed on the regulator output. In those cases, bypass should be as large as allowed by the regulator using a low ESL, low ESR capacitance. In the LM4120 example above, the supply is bypassed with  $0.022\mu F$  ceramic capacitors. The DAC should be fed with power that is only used for analog circuits.

Avoid crossing analog and digital signals and keep the clock and data lines on the component side of the board. The clock and data lines should have controlled impedances.

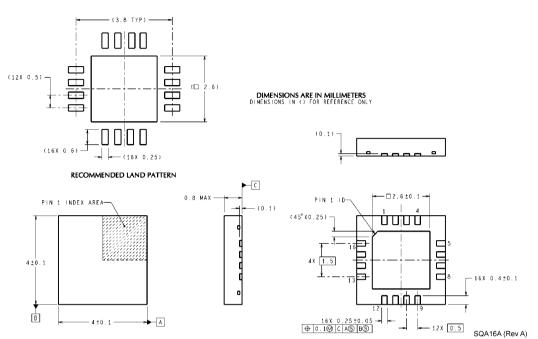

# Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead LLP NS Package Number SQA16A

| DAC161S055 Precision 16-Bit, Buffered Voltage-Output DAC | Notes |

|----------------------------------------------------------|-------|

| utbut                                                    |       |

| o-əbr                                                    |       |

| Volta                                                    |       |

| fered                                                    |       |

| t, Buf                                                   |       |

| 16-Bi                                                    |       |

| sion                                                     |       |

| Preci                                                    |       |

| <b>S055</b>                                              |       |

| C161                                                     |       |

| DA                                                       |       |

|                                                          |       |

|                                                          |       |

|                                                          |       |

|                                                          |       |

|                                                          |       |

|                                                          |       |

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

**Applications**