# RICOH

# **R5432V SERIES**

# 3 to 5 Cells Li-ion Battery Protector IC

NO.EA-263-1600711

# OUTLINE

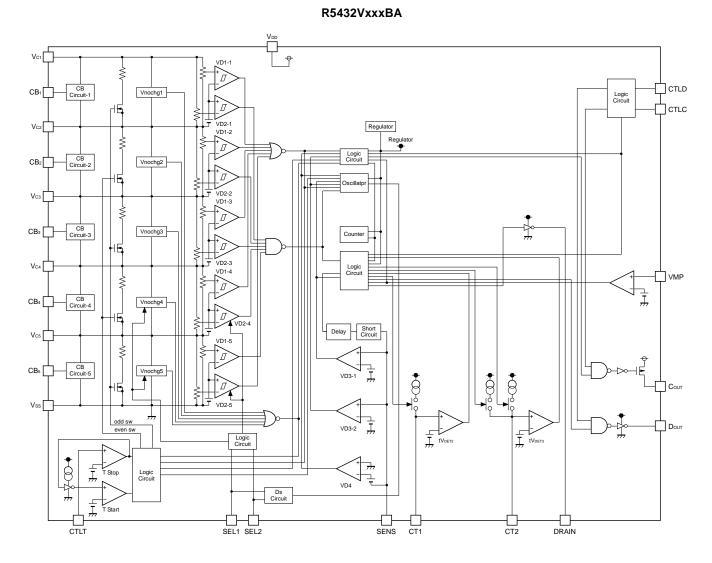

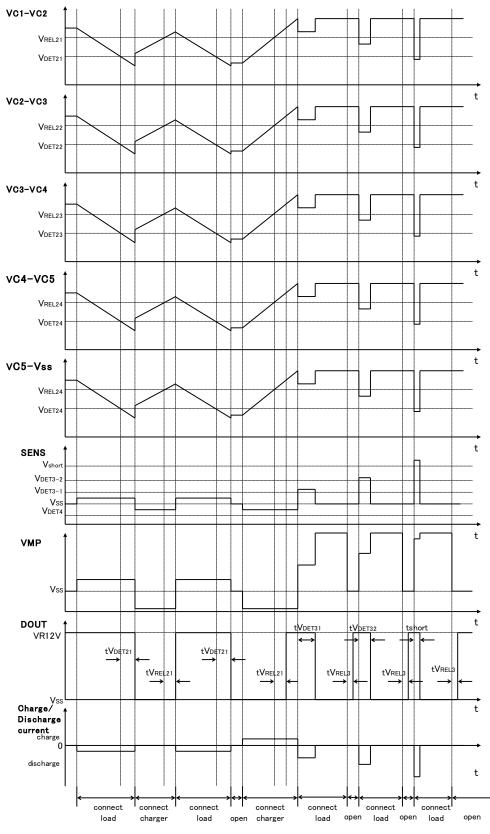

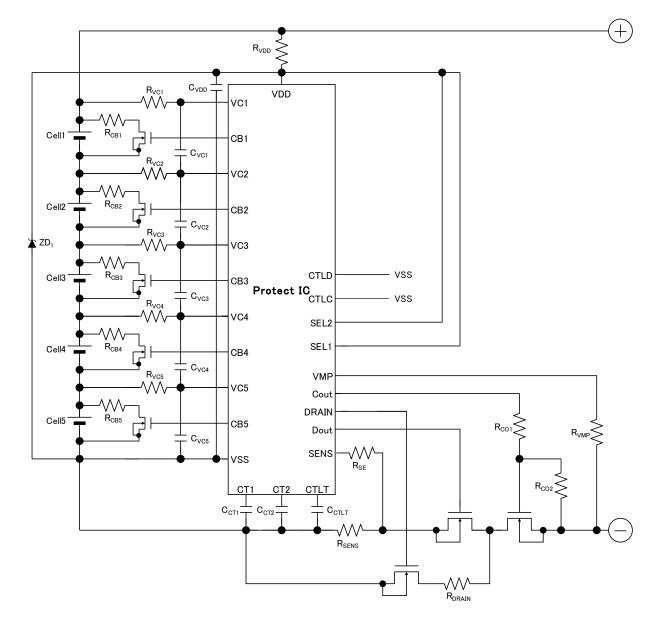

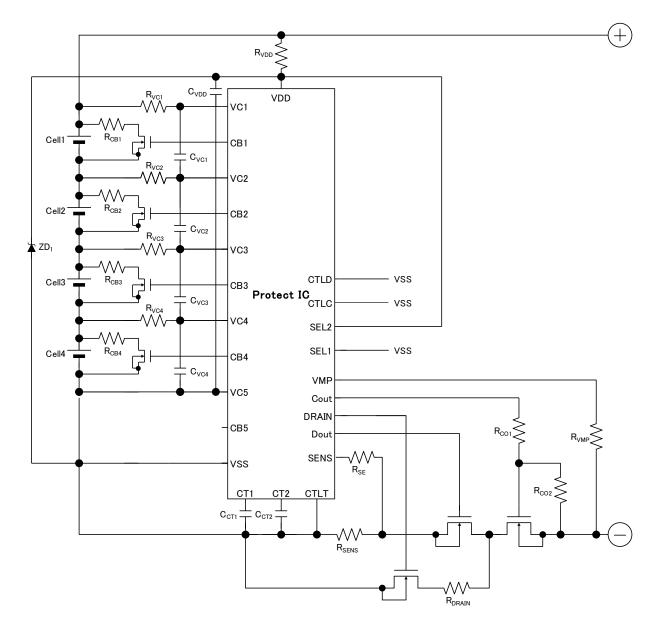

The R5432V is a high voltage CMOS-based protection IC for overcharge /discharge of rechargeable three-cell / four-cell / five-cell Lithium-ion / Lithium- polymer battery, further include a short circuit and the protection circuits against the excess discharge current and excess charge current.

Each of these ICs is composed of eighteen voltage detectors (fourteen for 3cell protection type, sixteen for 4cell protection type), a reference circuit, a delay circuit, a short detector circuit, an oscillator, a counter and a logic circuit.

The output of COUT is P-channel open-drain type, and DOUT is CMOS type.

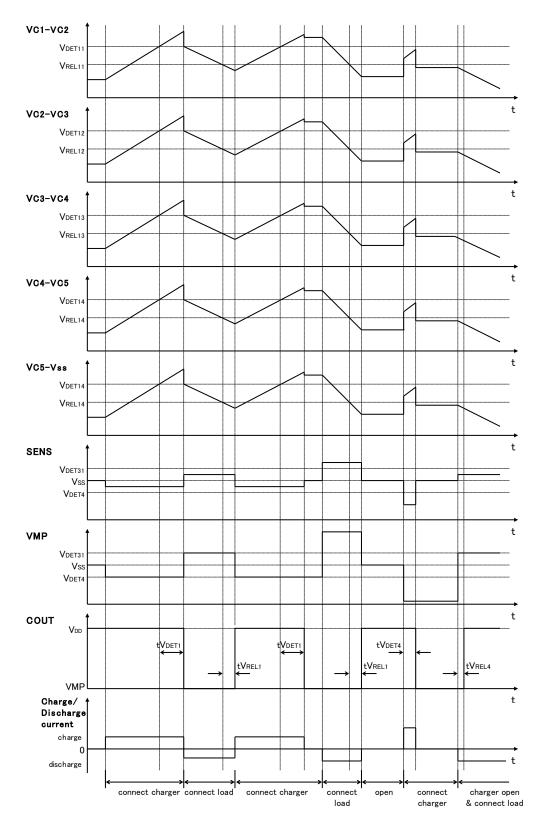

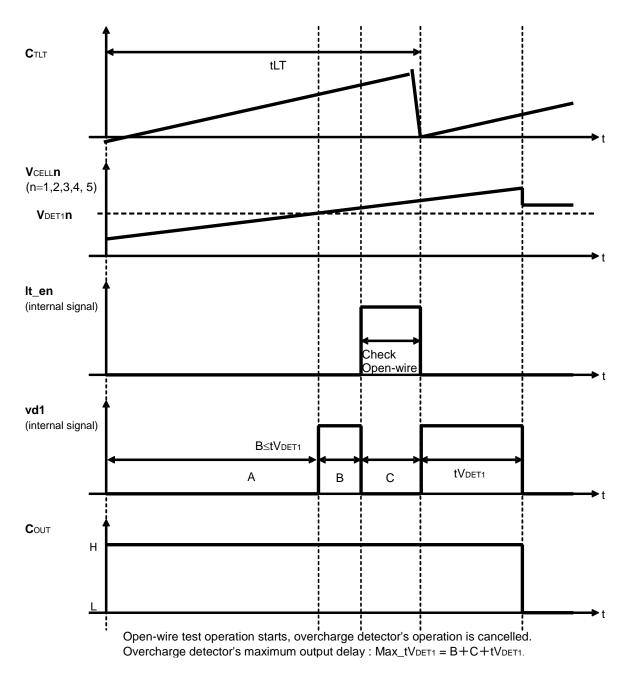

If the overcharge voltage or overcharge current is detected by the R5432V, after the preset output delay time, the output of COUT becomes Hi-Z.

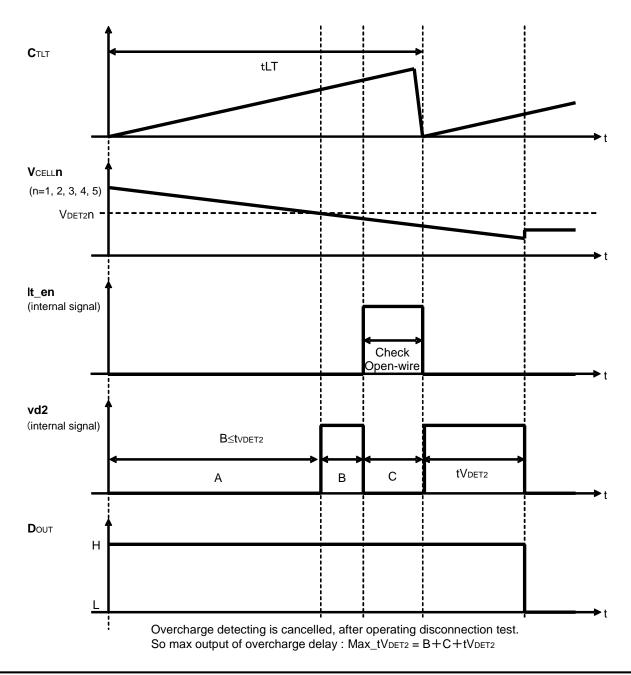

While the overdischarge voltage or current is detected, after the preset output delay time, the output of DOUT becomes "L". After detecting overcharge voltage, when the cell voltage returns lower than the overcharge released voltage, then overcharge is released and the output of COUT becomes "H". After detecting overcharge current, by disconnecting a charger and connecting a load, then overcharge current is released and the output of COUT becomes "H".

After detecting overdischarge voltage, when the cell voltage becomes the released voltage from overdischarge or more,

then overdischarge is released and the output of DOUT becomes "H". After detecting overdischarge current and short circuit, by disconnecting the load, the function of the output of DRAIN pin, the external NMOSFET turns on, and VMP pin voltage is pulled down by the resistance connected to GND and released overdischarge current or short and the output of DOUT becomes "H".

By forcing a certain voltage to SEL1 and SEL2 pins, the testing time of protection circuits can be short. Specifically, overcharge, discharge, over current delay time can be shortening into approximately 1/80.

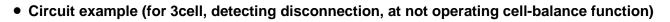

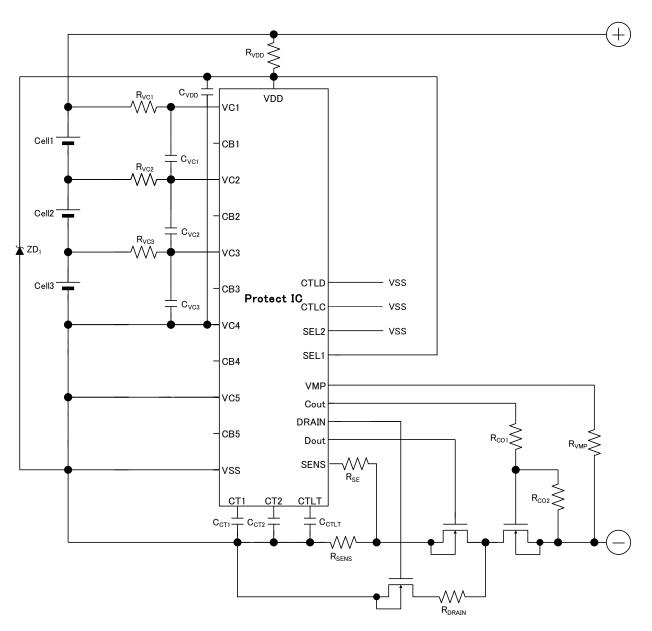

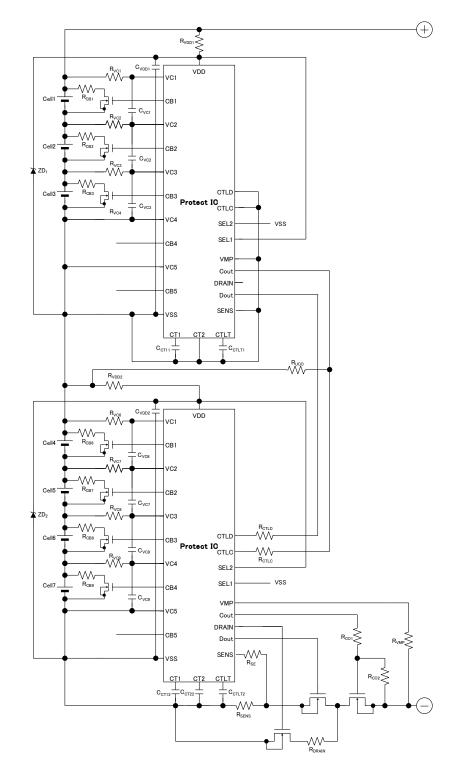

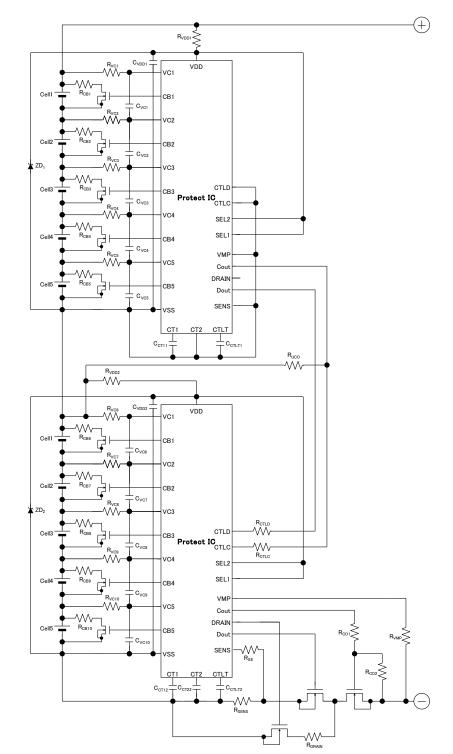

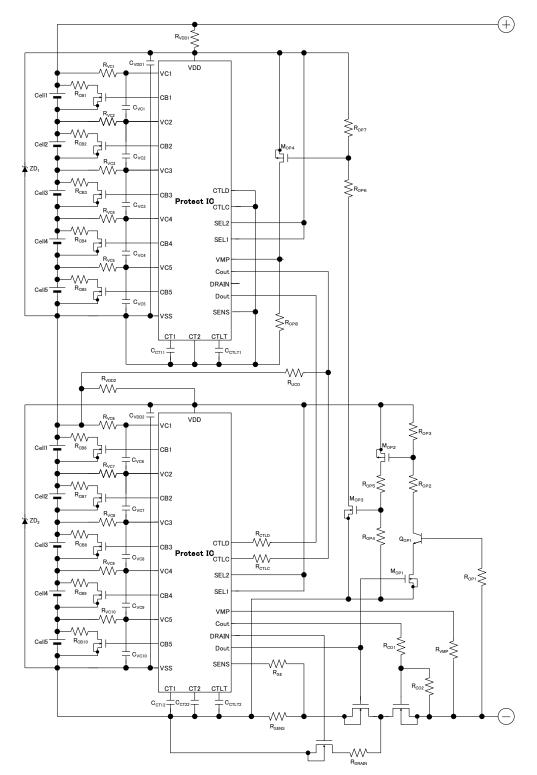

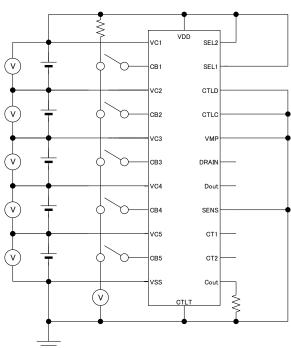

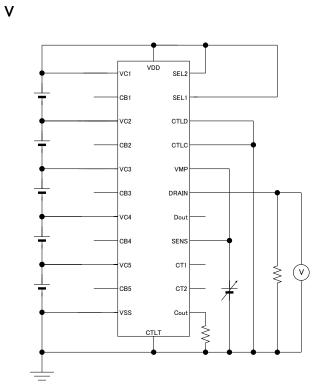

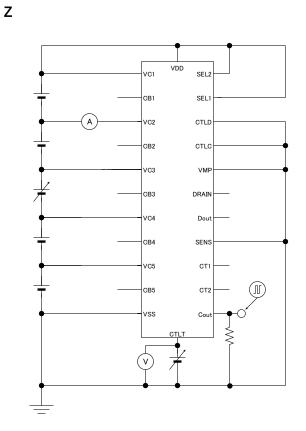

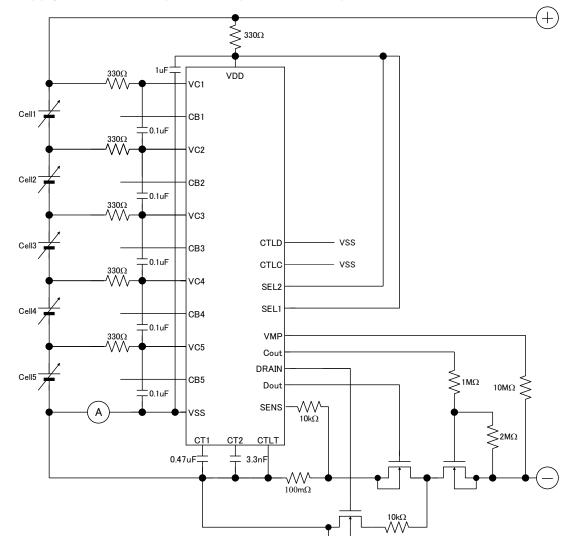

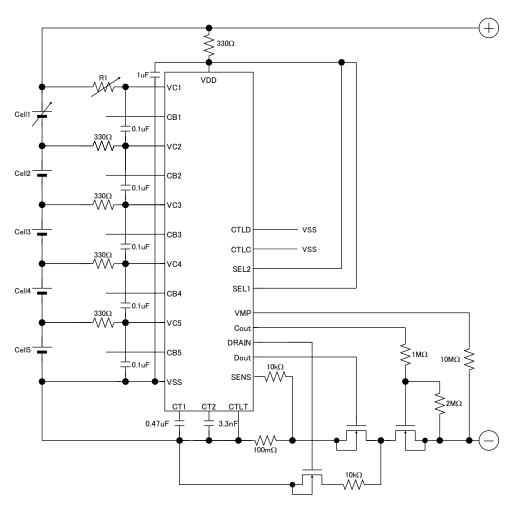

The R5432V can protect 6-cell or more by connecting 2 pieces of the R5432V in cascade. High side IC's COUT and DOUT must connect to CTLC and CTLD respectively of the low side IC. As a result, the signal of the high side of COUT and DOUT is transmit to the lower side IC, and control FETs for charge and discharge.

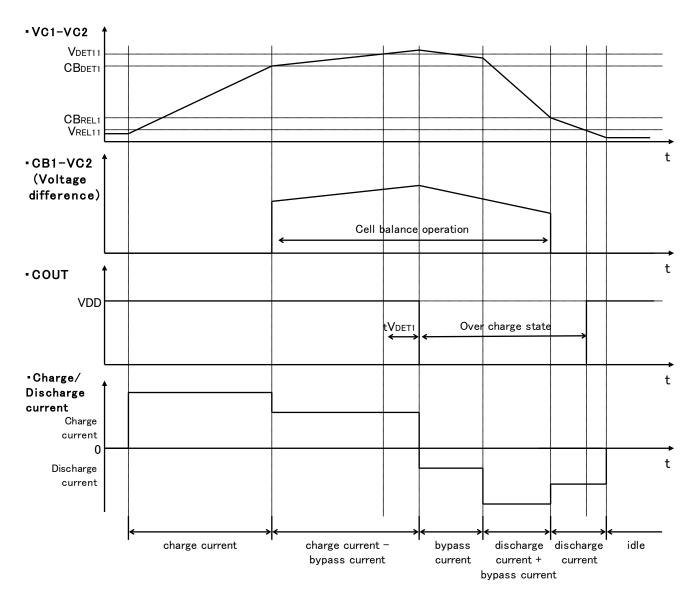

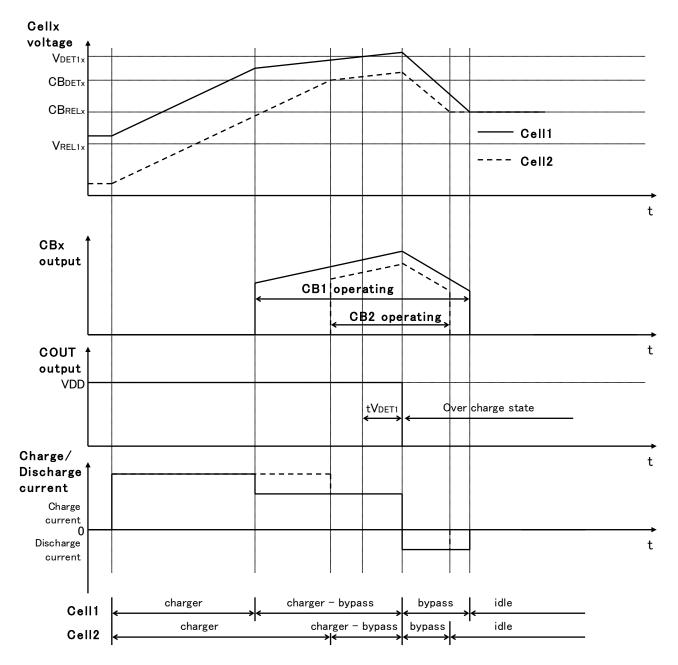

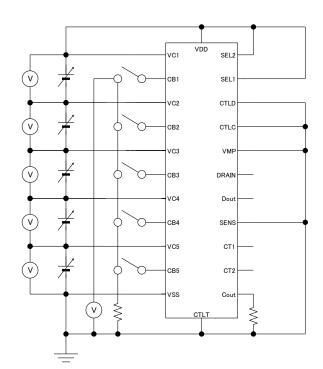

The R5432V has cell-balance function to solve the unbalance condition of serially connected cells. If cell voltage is beyond the cell balance detector threshold, by the output of the cell balance control pin, the external NMOSFET turns on, and a current path is made, and during charge, charge current is bypassed, otherwise, cell is discharged until the cell voltage becomes the released voltage from cell-balance operation.

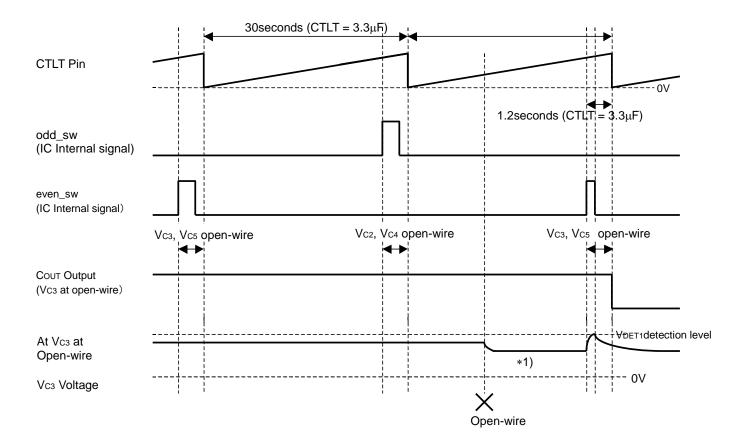

If the connection between a cell and a protection board is broken, the open-wire condition is detected by the R5432V, and the output of COUT becomes Hi-Z. After detecting the open-wire, when the cell and the protection board is connected again, the open-wire detector is released and the output of COUT becomes "H".

# FEATURES

| Absolute Maximum Rating                | 30V                                               |

|----------------------------------------|---------------------------------------------------|

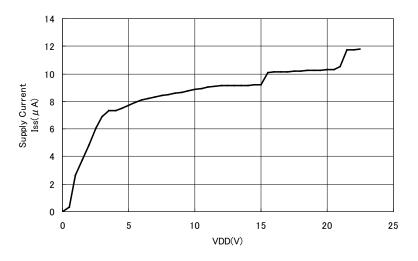

| Supply Current                         | Тур. 12.0μА                                       |

| Detector thresholds range and accuracy |                                                   |

| Overcharge detector threshold          |                                                   |

| Overdischarge detector threshold       |                                                   |

| Excess discharge current threshold 1   | 0.1V to 0.3V (10mVstep) (±20mV) for BA/BB/BC ver. |

|                                        | 0.1V to 0.2V (10mV step) (±20mV) for AD/BD ver.   |

| Excess discharge current threshold 2   | 0.45V/0.60V for BA ver.                           |

|                                        | 0.25V to 0.40V for BB/BC ver.                     |

|                                        | 0.25V/0.3V(Vdet3-1+0.1V or more) for AD/BD ver.   |

NO.EA-263-160711

| Short detector threshold                                               | 1.00V for BA ver.                                                 |

|------------------------------------------------------------------------|-------------------------------------------------------------------|

|                                                                        | 0.75V for BB/BC ver.                                              |

|                                                                        | Vdet3-2 x 1.67 for AD/BD ver.                                     |

| Excess charge current threshold                                        | 0.05V (±30mV), -0.1V (±30mV), -0.2V (±30mV), -0.4V (±40mV)        |

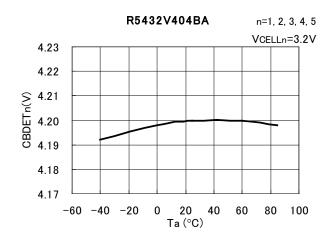

| Overcharge released voltage                                            | VDET1n-0.1V to 0.4V (50mV steps) (n=1, 2, 3, 4, 5)                |

| Overdischarge released voltage                                         |                                                                   |

|                                                                        | up to 3.4V                                                        |

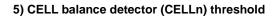

| Cell-balance detector threshold                                        |                                                                   |

| Cell-balance released voltage                                          | CBDETN-0.0V to 0.4V (50mV steps) (n=1, 2, 3, 4, 5)                |

| Output delay time                                                      |                                                                   |

| Overcharge detector Output Delay                                       | 1.0s                                                              |

| Overdischarge detector Output Delay                                    | Settable by Ext.Capacitance1                                      |

| <ul> <li>Excess discharge current detector Output Delay 1/2</li> </ul> | Settable by Ext.Capacitance2                                      |

| Excess charge current detector Output Delay                            | 8ms                                                               |

| Short detector Output Delay                                            | 300µs                                                             |

| Functions                                                              |                                                                   |

| OV-battery charger                                                     | acceptable/unacceptable options                                   |

| Cascade connection                                                     | Available. Refer to the typical application.                      |

| 3/4/5 cell protection                                                  | Selectable                                                        |

| Output Delay Time Shortening Function                                  | By forcing a certain voltage to SEL pin, overcharge,              |

|                                                                        | discharge voltage and current is reduced approximately 1/80.      |

|                                                                        | Overcharge delay time can be shorten into around 4ms for          |

|                                                                        | testing.                                                          |

| Cell-balance function                                                  | Available                                                         |

| Cell-unbalance condition                                               | If either of cells detects overcharge and either of cells detects |

| overdischarge, the output of COUT becomes "Hi-Z", the o                | putput of DOUT becomes "L".                                       |

| Overcharge/Overdischarge released condition                            |                                                                   |

| Output of COUT/DOUT                                                    | COUT: VDD source P-channel open drain output. Normal              |

|                                                                        | state "H"(VDD), Detected state "Hi-Z".                            |

|                                                                        | DOUT: 12V regulator source CMOS output. Normal state              |

|                                                                        | "H"(12V), Detected state "L".                                     |

| Open-wire detection                                                    |                                                                   |

|                                                                        | supervised.                                                       |

| Small Package                                                          | •                                                                 |

| 0                                                                      |                                                                   |

NO.EA-263-160711

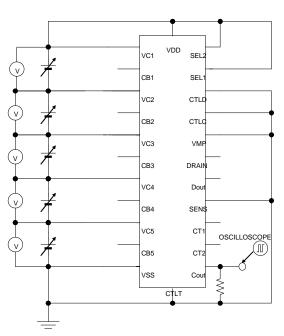

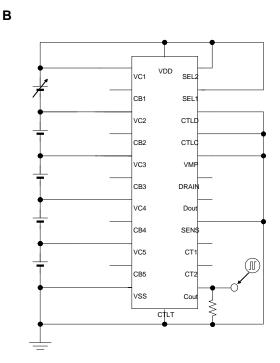

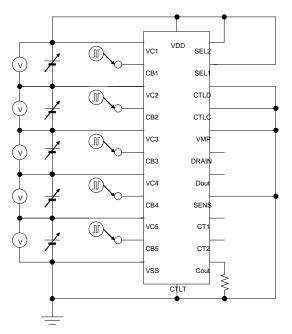

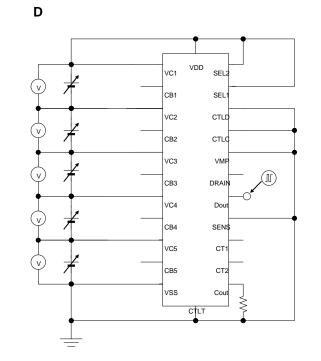

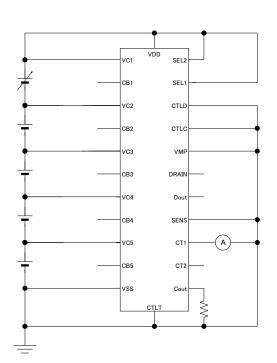

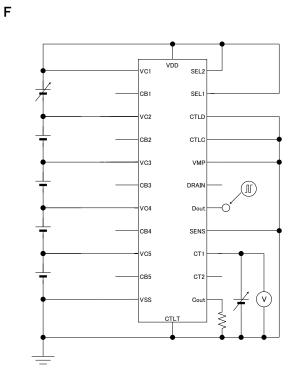

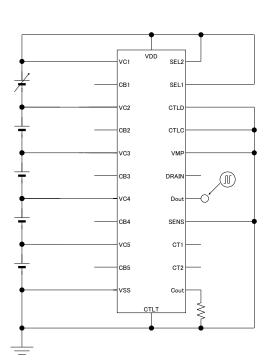

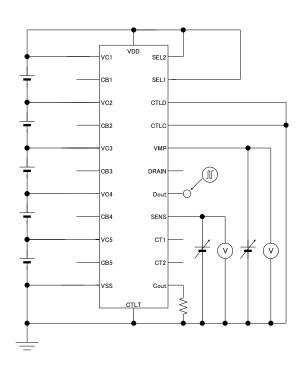

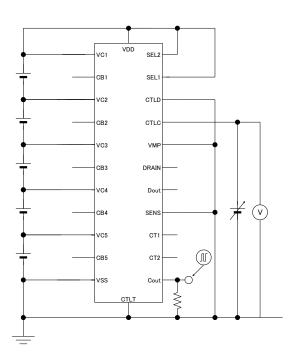

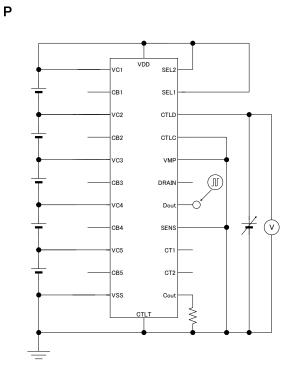

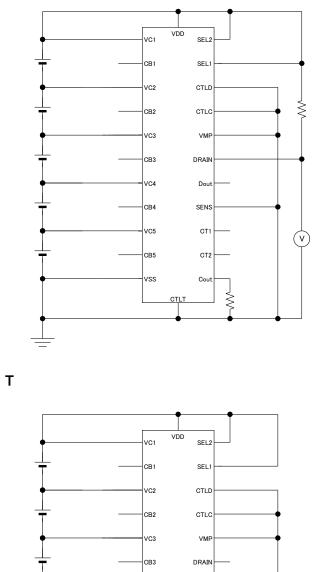

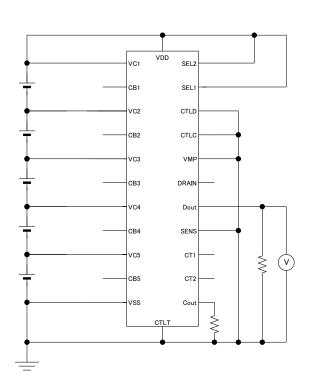

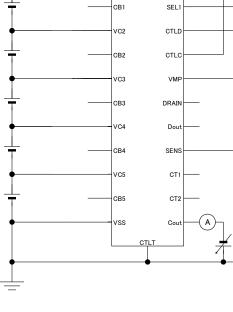

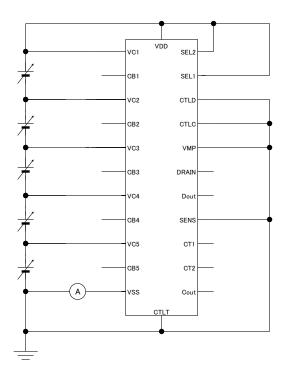

# **BLOCK DIAGRAMS**

NO.EA-263-160711

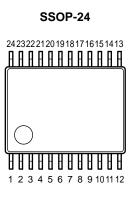

# **SELECTION GUIDE**

| FI                                                                          | oduct Name                                         |                                  | Packag                           | e Qi                                 | uantity p      | er Ree               | Pb Fre                                          | e                 | Halogen Free                  |                         |

|-----------------------------------------------------------------------------|----------------------------------------------------|----------------------------------|----------------------------------|--------------------------------------|----------------|----------------------|-------------------------------------------------|-------------------|-------------------------------|-------------------------|

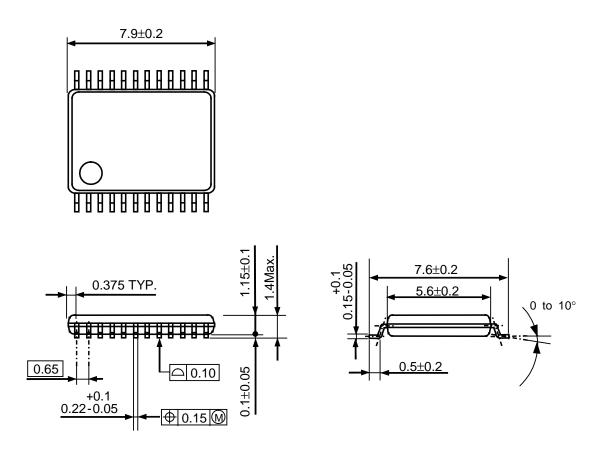

| 5432                                                                        | 2Vxxx\$*                                           |                                  | SSOP-24                          |                                      | 3000           | )                    | Yes                                             |                   |                               | Yes                     |

|                                                                             | overdischarge                                      | ige, Cell-<br>e released         | balance<br>d voltage             | threshold, C<br>e, overdischa        | ell-balan      | ce rele              | as overcharge<br>ased voltage,<br>overcharge cu | overdise          | charge thre                   | eshold,                 |

| \$                                                                          |                                                    |                                  | ,                                |                                      | horao          |                      | ordioaborgo                                     |                   | roborgo                       | Short                   |

|                                                                             | Overcharge<br>Delay time<br>(s)                    | Overdis<br>Delay<br>(m:          | time                             | Overdisc<br>Current Del<br>(ms       | ay time1       |                      | erdischarge<br>nt Delay time2<br>(ms)           | Current           | rcharge<br>Delay time<br>(ms) |                         |

| A                                                                           | 1.0                                                | 3.64×C                           | ст1 (nF)                         | 3.05×Cc                              | r2 (nF)        | tV                   | DET 31/ 100                                     | 8                 |                               | 300                     |

| E                                                                           | 3 1.0                                              | 3.88×C                           | ст1 (nF)                         | 3.26×Cc                              | r2 (nF)        | ť                    | Vdet31/ 6                                       |                   | 8                             | 300                     |

| *capacitor for CT1: C <sub>CT1</sub> , capacitor for CT2:C <sub>CT2</sub> . |                                                    |                                  |                                  |                                      |                |                      |                                                 |                   |                               |                         |

| *                                                                           | : Designation                                      | of Outpu                         | it delay o                       | option.                              |                |                      |                                                 |                   |                               |                         |

| *                                                                           | Övercha                                            | arge                             | Over                             | discharge                            | 0V bat         | -                    | Short detecto                                   |                   | en-wire                       | Cascade                 |

| *                                                                           |                                                    | arge                             | Over<br>Release                  | discharge<br>ed condition            |                | -                    | Short detecto<br>Threshold                      |                   | en-wire<br>ection             | Cascade connection      |

| *                                                                           | Övercha<br>Released co                             | arge<br>ondition                 | Over<br>Release                  | discharge                            |                | ge                   |                                                 | det               |                               |                         |

|                                                                             | Övercha<br>Released co<br>Auto Rel                 | arge<br>ondition<br>ease         | Over<br>Release<br>Auto          | discharge<br>ed condition            | Char           | ge<br>able           | Threshold                                       | det<br>Ava        | ection                        | connection              |

| A                                                                           | Övercha<br>Released co<br>A Auto Rel<br>B Auto Rel | arge<br>ondition<br>ease<br>ease | Overo<br>Release<br>Auto<br>Auto | discharge<br>ed condition<br>Release | Char<br>Accept | ge<br>able<br>ptable | Threshold<br>1.0V                               | det<br>Ava<br>Ava | ection<br>ailable             | connection<br>Available |

NO.EA-263-160711

#### 1) Product Code List

|             | VDET1n | VREL1n | VCBDn  | VCBRn  | VDET2n | VREL2n | VDET31 | VDET32 | VSHORT | VDET4  |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Code        | (V) *1 | (V)    | (V)    | (V)    | (V)    |

| R5432V402BA | 4.350  | 4.050  | 4.200  | 4.200  | 2.400  | 2.700  | 0.200  | 0.600  | 1.000  | -0.100 |

| R5432V403BA | 3.900  | 3.800  | 3.500  | 3.500  | 2.500  | 3.000  | 0.100  | 0.600  | 1.000  | -0.100 |

| R5432V404BA | 4.250  | 4.100  | 4.200  | 4.200  | 2.500  | 3.000  | 0.200  | 0.600  | 1.000  | -0.200 |

| R5432V405BA | 3.900  | 3.800  | 3.650  | 3.650  | 2.000  | 2.300  | 0.100  | 0.600  | 1.000  | -0.200 |

| R5432V406BA | 3.650  | 3.550  | 3.500  | 3.500  | 2.500  | 3.000  | 0.300  | 0.600  | 1.000  | -0.200 |

| R5432V407BA | 4.200  | 4.000  | 3.900  | 3.900  | 2.700  | 2.850  | 0.200  | 0.450  | 1.000  | -0.200 |

| R5432V408BA | 3.800  | 3.600  | 3.450  | 3.450  | 2.000  | 2.300  | 0.200  | 0.450  | 1.000  | -0.100 |

| R5432V409BA | 4.100  | 4.000  | 3.900  | 3.900  | 3.000  | 3.100  | 0.200  | 0.600  | 1.000  | -0.200 |

| R5432V410BC | 4.200  | 4.000  | 4.150  | 4.150  | 2.750  | 2.950  | 0.100  | 0.250  | 0.750  | -0.050 |

| R5432V412BA | 4.300  | 4.050  | 4.200  | 4.200  | 2.700  | 3.000  | 0.200  | 0.600  | 1.000  | -0.100 |

| R5432V413BA | 4.250  | 4.100  | 4.200  | 4.200  | 2.500  | 3.000  | 0.100  | 0.600  | 1.000  | -0.100 |

| R5432V416BA | 4.200  | 4.100  | 4.170  | 4.170  | 2.500  | 3.000  | 0.200  | 0.450  | 1.000  | -0.100 |

| R5432V417BC | 4.200  | 4.100  | 4.180  | 4.180  | 2.500  | 3.000  | 0.100  | 0.400  | 0.750  | -0.050 |

| R5432V418BC | 4.180  | 4.080  | 4.180  | 4.180  | 2.500  | 3.000  | 0.100  | 0.400  | 0.750  | -0.050 |

| R5432V419BD | 3.900  | 3.800  | 3.500  | 3.500  | 2.500  | 3.000  | 0.100  | 0.300  | 0.500  | -0.100 |

| R5432V420BD | 4.350  | 4.050  | 4.200  | 4.200  | 2.400  | 2.700  | 0.100  | 0.250  | 0.418  | -0.100 |

| R5432V501BA | 3.900  | 3.700  | 3.800  | 3.600  | 2.000  | 2.300  | 0.200  | 0.600  | 1.000  | -0.200 |

| R5432V502BA | 4.250  | 4.100  | 4.200  | 4.190  | 2.800  | 3.000  | 0.100  | 0.450  | 1.000  | -0.050 |

| R5432V503BB | 4.250  | 4.150  | 4.150  | 4.140  | 2.700  | 3.000  | 0.150  | 0.300  | 0.750  | -0.050 |

| R5432V504BD | 4.250  | 4.100  | 4.200  | 4.190  | 2.800  | 3.000  | 0.100  | 0.250  | 0.418  | -0.050 |

| R5432V505BD | 4.250  | 4.100  | 4.200  | 4.190  | 2.500  | 3.000  | 0.100  | 0.250  | 0.418  | -0.050 |

| R5432V506BD | 3.900  | 3.800  | 3.650  | 3.640  | 2.000  | 2.300  | 0.100  | 0.250  | 0.418  | -0.050 |

| R5432V507BD | 4.215  | 4.100  | 4.200  | 4.180  | 2.800  | 3.000  | 0.100  | 0.250  | 0.418  | -0.100 |

| R5432V508BA | 3.800  | 3.700  | 3.600  | 3.580  | 2.800  | 2.900  | 0.200  | 0.600  | 1.000  | -0.100 |

| R5432V509BD | 3.900  | 3.800  | 3.650  | 3.640  | 2.000  | 2.300  | 0.100  | 0.250  | 0.418  | -0.100 |

| R5432V510BD | 3.900  | 3.800  | 3.475  | 3.465  | 2.000  | 2.300  | 0.100  | 0.250  | 0.418  | -0.100 |

\*1:n=1,2,3,4,5

NO.EA-263-160711

# **PIN DESCRIPTIONS**

| Pin No | Symbol          | Pin Description                                                   |

|--------|-----------------|-------------------------------------------------------------------|

| 1      | CTLC            | Cout control pin                                                  |

| 2      | CTLD            | Dout control pin                                                  |

| 3      | Соит            | Output pin of overcharge detection, Pch OPEN DRAIN output         |

| 4      | VMP             | Pin for charger negative input                                    |

| 5      | DRAIN           | Release from Excess discharge-current threshold Pin               |

| 6      | Dout            | Output pin of overdischarge detection, CMOS output                |

| 7      | SENS            | Current sense pin                                                 |

| 8      | CTLT            | Disconnection detection movement interval setting capacitance pin |

| 9      | Vss             | Vss pin. Ground pin for the IC                                    |

| 10     | CT1             | tVDET2 setting capacitance connection pin                         |

| 11     | CT2             | tVDET3 setting capacitance connection pin                         |

| 12     | SEL1            | 3cell/4cell/5cell alternative pin1                                |

| 13     | SEL2            | 3cell/4cell/5cell alternative pin2                                |

| 14     | CB5             | CELL5 Cell balance Control pin                                    |

| 15     | Vc5             | Positive terminal pin for Cell5                                   |

| 16     | CB4             | CELL4 Cell balance Control pin                                    |

| 17     | Vc4             | Positive terminal pin for Cell4                                   |

| 18     | CB3             | CELL3 Cell balance Control pin                                    |

| 19     | V <sub>C3</sub> | Positive terminal pin for Cell3                                   |

| 20     | CB2             | CELL2 Cell balance Control pin                                    |

| 21     | Vc2             | Positive terminal pin for Cell2                                   |

| 22     | CB1             | CELL1 Cell balance Control pin                                    |

| 23     | Vc1             | Positive terminal pin for Cell1                                   |

| 24     | Vdd             | V <sub>DD</sub> pin                                               |

NO.EA-263-160711

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol         | Item                                                              | Rating                                                                                         | Unit |  |

|----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|--|

| Vdd            | Supply voltage                                                    | -0.3 to 30                                                                                     | V    |  |

| Input voltage  |                                                                   |                                                                                                |      |  |

| Vc1            | Positive input pin for Cell1                                      | Vc2-0.3 to Vc2+6.5                                                                             | V    |  |

| Vc2            | Positive input pin for Cell2                                      | Vc3-0.3 to Vc3+6.5                                                                             | V    |  |

| Vc3            | Positive input pin for Cell3                                      | Vc4-0.3 to Vc4+6.5                                                                             | V    |  |

| Vc4            | Positive input pin for Cell4                                      | Vc5-0.3 to Vc5+6.5                                                                             | V    |  |

| Vc5            | Positive input pin for Cell5                                      | -0.3 to 6.5                                                                                    | V    |  |

| VMP            | Charger negative terminal input pin                               | -0.3 to 30.0                                                                                   | V    |  |

| VSEL1          | 3Cell/4Cell/5Cell alternative pin1                                | -0.3 to V <sub>DD</sub> +0.3                                                                   | V    |  |

| VSEL2          | 3Cell/4Cell/5Cell alternative pin2                                | -0.3 to VDD+0.3                                                                                | V    |  |

| Vctlc          | Cout control pin                                                  | -0.3 to VDD+25                                                                                 | V    |  |

| VOILO          |                                                                   | -0.3 to Vpp+25<br>-0.3 to 48<br>-0.3 to Vpp+25<br>-0.3 to 48<br>-0.3 to Vpp+0.3<br>-0.3 to 3.5 | v    |  |

| Vctld          | Dout control pin                                                  |                                                                                                | V    |  |

|                |                                                                   |                                                                                                |      |  |

| VSENSE         | Current sense pin                                                 |                                                                                                | V    |  |

| Vct1           | Delay time setting pin1                                           | -0.3 to 3.5                                                                                    | V    |  |

| Vct2           | Delay time setting pin2                                           | -0.3 to 3.5                                                                                    | V    |  |

| VCTLT          | Disconnection detection movement interval setting capacitance pin | -0.3 to 3.5                                                                                    | V    |  |

| Output voltage |                                                                   |                                                                                                |      |  |

| Vcout          | Output pin of overcharge detection, CMOS output                   | VDD-30 to VDD+0.3                                                                              | V    |  |

| Vdout          | Output pin of overdischarge detection, CMOS output                | -0.3 to Vон2+0.3                                                                               | V    |  |

| Vdrain         | Release from Excess discharge-current threshold Pin               | -0.3 to Vонз+0.3                                                                               | V    |  |

| VCB1           | Cell balance Control pin for Cell1                                | Vc2-0.3 to Vc2+6.5                                                                             | V    |  |

| VCB2           | Cell balance Control pin for Cell2                                | Vc3-0.3 to Vc3+6.5                                                                             | V    |  |

| Vсвз           | Cell balance Control pin for Cell3                                | Vc4-0.3 to Vc4+6.5                                                                             | V    |  |

| VCB4           | Cell balance Control pin for Cell4                                | Vc5-0.3 to Vc5+6.5                                                                             | V    |  |

| VCB5           | Cell balance Control pin for Cell5                                | -0.3 to 6.5                                                                                    | V    |  |

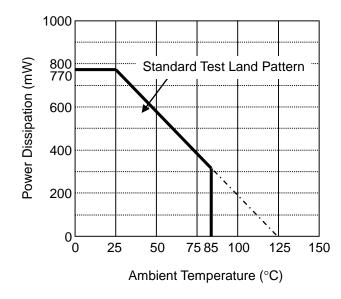

| PD             | Power dissipation <sup>(1)</sup>                                  | 770                                                                                            | mW   |  |

| Та             | Operating temperature range                                       | -40 to 85                                                                                      | °C   |  |

| Tstg           | Storage temperature range                                         | -55 to 125                                                                                     | °C   |  |

# ABSOLUTE MAXIMUM RATINGS

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause the permanent damages and may degrade the life time and safety for both device and system using the device in the field. The functional operations at or over these absolute maximum ratings are not assured.

NO.EA-263-160711

# ELECTRICAL CHARACTERISTICS

## • R5432VxxxBA

Unless otherwise specified, Ta= $25^{\circ}C$

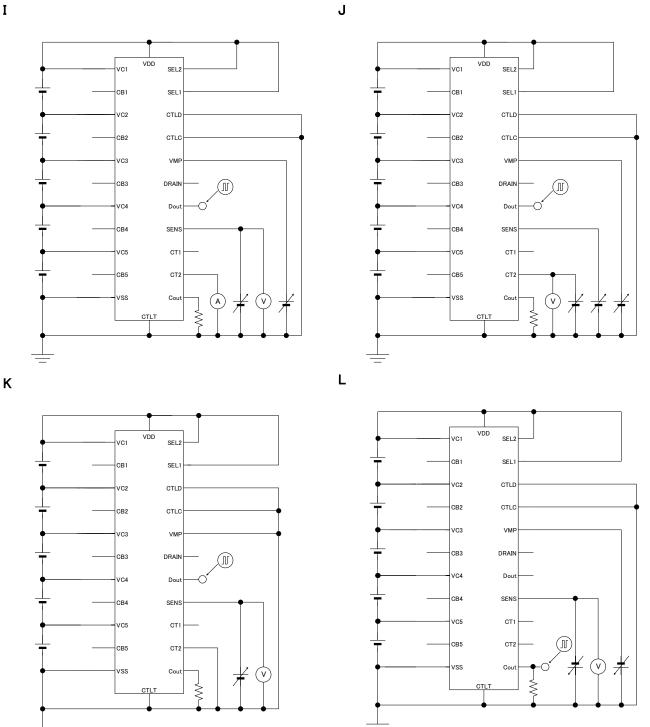

| Symbol             | Items                                                                 | Conditions                                                                                                                      | Min.             | Тур.            | Max.                                                 | Unit | Circuit |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------------------------------------------|------|---------|

| Vdd1               | Operating input voltage                                               | Vdd-Vss                                                                                                                         | 2                |                 | 25                                                   | V    | -       |

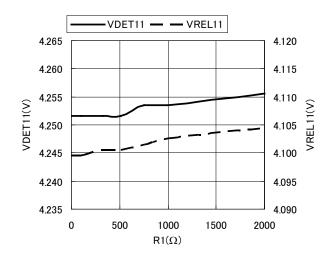

| Vdet1n             | CELLn Overcharge threshold<br>(n=1,2,3,4,5)                           | Detect rising edge of supply voltage                                                                                            | Vdet1n<br>-0.025 | Vdet1n          | Vdet1n<br>+0.025                                     | V    | А       |

| Vrel1n             | CELLn Overcharge released<br>Voltage (n=1,2,3,4,5)                    | Detect falling edge of supply voltage                                                                                           | VREL1N<br>-0.050 | Vrel1n          | V <sub>REL1</sub> n<br>+0.050                        | V    | А       |

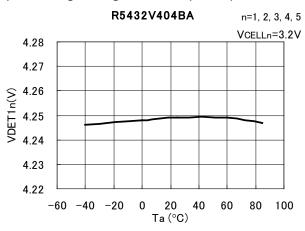

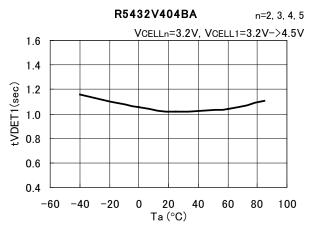

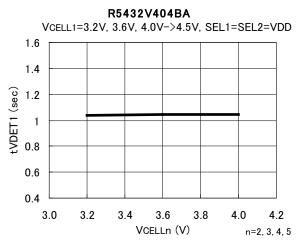

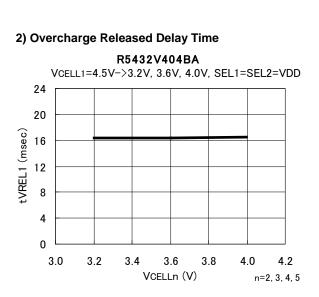

| tVdet1             | Output delay of overcharge                                            | VDD=VC1,VCELLN=3.5V (n=2,3,4,5),<br>VCELL1=3.5V→4.5V                                                                            | 0.7              | 1.0             | 1.3                                                  | s    | В       |

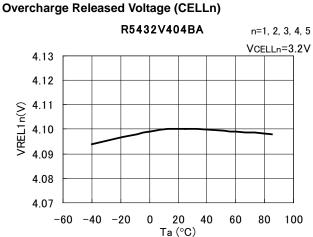

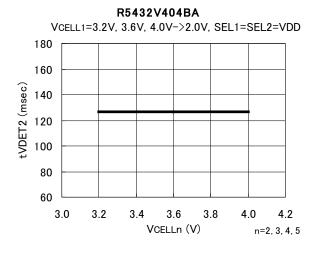

| tV <sub>REL1</sub> | Output delay of<br>release from overcharge                            | Vdd=Vc1, Vcelln=3.5V<br>(n=2,3,4,5), Vcell1=4.5V→3.5V                                                                           | 11               | 16              | 21                                                   | ms   | В       |

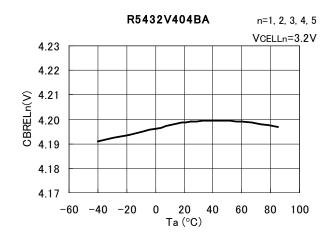

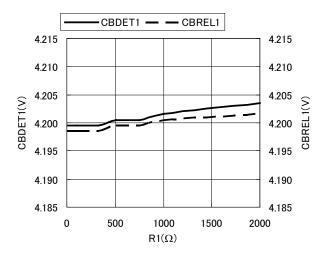

| VсвDn              | CELLn balance threshold (n=1,2,3,4,5)                                 | Detect rising edge of supply voltage                                                                                            | Vсвдл<br>-0.025  | Vcbdn           | Vсвол<br>+0.025                                      | V    | С       |

| Vcbrn              | CELLn balance<br>released threshold<br>(n=1,2,3,4,5)                  | Detect falling edge of supply voltage                                                                                           | Vcbrn<br>-0.050  | Vcbrn           | Lower of<br>VCBRN<br>+0.050<br>or<br>VCBDN<br>+0.025 | v    | с       |

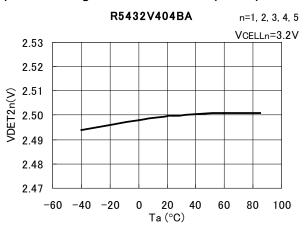

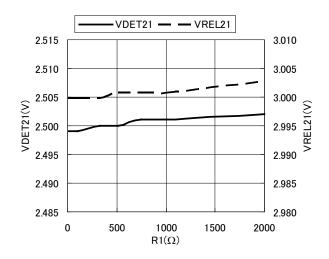

| Vdet2n             | CELLn Overdischarge<br>threshold (n=1,2,3,4,5)                        | Detect falling edge of supply voltage                                                                                           | Vdet2n<br>×0.975 | Vdet2n          | V <sub>DET2</sub> n<br>×1.025                        | V    | D       |

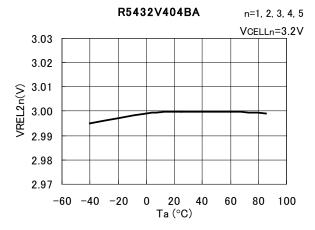

| Vrel2n             | CELLn Overdischarge released Voltage (n=1,2,3,4,5)                    | Detect rising edge of supply voltage                                                                                            | VREL2N<br>×0.975 | VREL2N          | V <sub>REL2</sub> n<br>×1.025                        | V    | D       |

| ICT1               | CT1 charge Current                                                    | VDD=VC1, VCELLN=3.5V<br>(n=2, 3, 4, 5), VCELL1=3.5V→1.5V                                                                        | 350              | 500             | 650                                                  | nA   | E       |

| VDCT1              | CT1 detector voltage                                                  | Vdd=Vc1, Vcelln=3.5V<br>(n=2, 3, 4, 5), Vcell1=1.5V                                                                             | 1.48             | 1.85            | 2.22                                                 | V    | F       |

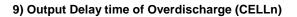

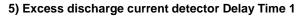

| tVdet2             | Output delay of overdischarge                                         | tVDET2=CCT1×VDCT1/ICT1<br>CCT1=33nF                                                                                             | 89               | 128             | 167                                                  | ms   | -       |

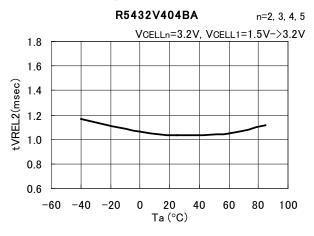

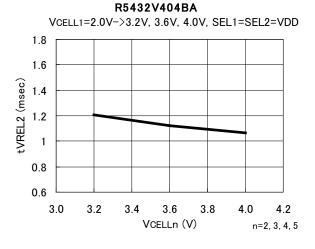

| tVREL2             | Output delay of release from overdischarge                            | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>V <sub>CELL1</sub> =1.5V→3.5V         | 0.7              | 1.2             | 1.7                                                  | ms   | G       |

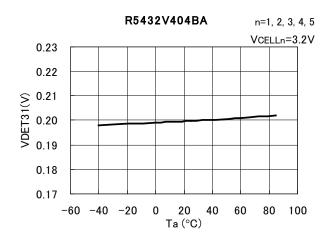

| Vdet31             | Excess discharge-current threshold1                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage  | Vdet31<br>-0.020 | Vdet31          | Vdet31<br>+0.020                                     | V    | н       |

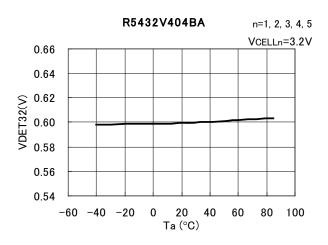

| Vdet32             | Excess discharge-current<br>Threshold2                                | VDD=VC1, VCELLN=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage                                         | 0.500            | 0.600           | 0.700                                                | V    | I       |

| Vrel3              | Output delay of<br>release from Excess<br>discharge-current threshold | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), SENSE=0V<br>Detect falling edge of supply voltage | Vdet31<br>×0.50  | Vdet31<br>×0.75 | Vdet31<br>×1.00                                      | V    | Н       |

| Іст231             | CT2 Charge Current1                                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5) SENSE=Vss→0.4V                                    | 350              | 500             | 650                                                  | nA   | I       |

| Іст232             | CT2 Charge Current2                                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5) SENSE=Vss→0.7V                                    | 2.0              | 3.0             | 4.0                                                  | μA   | I       |

| VDCT2              | CT2 Charge voltage                                                    | VDD=Vc1, Vcelln =3.5V (n=2,3,4,5)<br>SENSE=0.4V, VMP=4.0V                                                                       | 1.23             | 1.55            | 1.87                                                 | V    | J       |

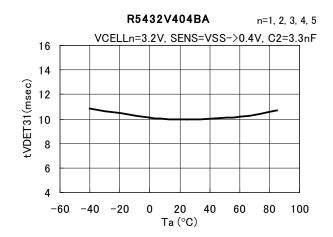

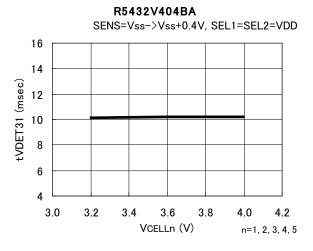

| tVdet31            | Output delay of Excess<br>discharge-current threshold1                | tvdet31=Cct2×Vdct2/lct231<br>Cct2=3.3nF                                                                                         | 7.3              | 10.8            | 14.7                                                 | ms   | -       |

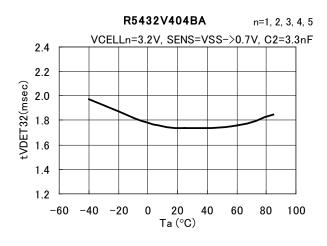

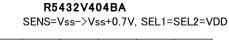

| tVdet32            | Output delay of Excess<br>discharge-current Threshold2                | tvdet32=Cct2×Vdct2/lct232<br>Cct2=3.3nF                                                                                         | 1.25             | 1.8             | 2.4                                                  | ms   | -       |

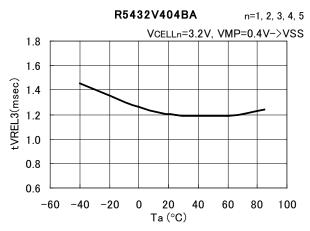

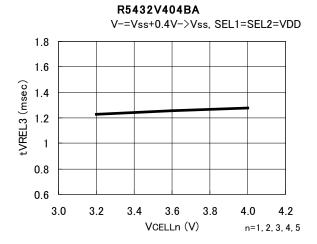

| tVrel3             | Output delay of release from<br>Excess discharge-current<br>Threshold | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5)<br>SENS=0.4V, VMP= 4.0V                            | 0.7              | 1.2             | 1.7                                                  | ms   | н       |

NO.EA-263-160711

| Symbol             | Items                                                              | Conditions                                                                                                                       | Min.            | Тур.        | Max.                        | Unit | Circuit |

|--------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|-----------------------------|------|---------|

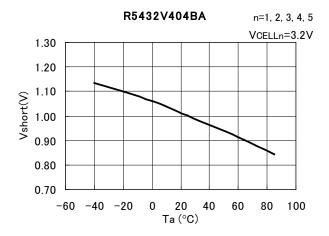

| Vshort             | Short protection voltage                                           | VDD=Vc1, VCELLn=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising of supply voltage                                               | 0.7             | 1.0         | 1.7                         | V    | к       |

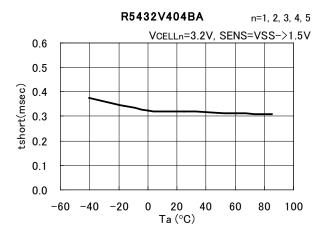

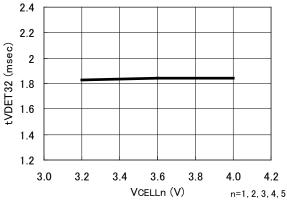

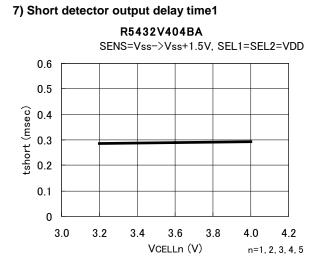

| tshort             | Output Delay of Short protection                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5) SENS=0.0V→2.0V,<br>VMP=4.0V                        | 180             | 300         | 550                         | μS   | к       |

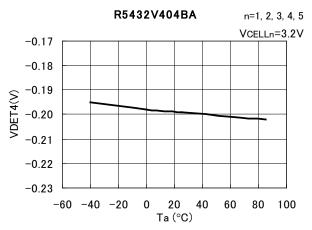

| Vdet4              | Excess charge-current threshold                                    | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=-1.0V<br>Detect falling edge of supply voltage | Vdet4<br>-0.030 | Vdet4       | Vdet4<br>+0.030             | V    | L       |

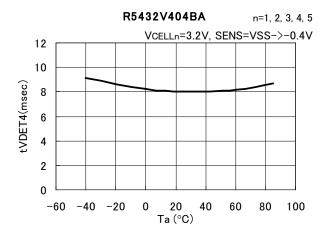

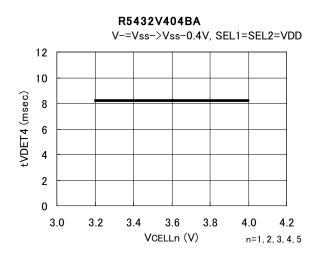

| tVdet4             | Output delay of Excess charge-current threshold                    | V <sub>DD</sub> =V <sub>C1</sub> , VCELLn =3.5V<br>(n=1,2,3,4,5)<br>SENS=0.0V→-1.0V                                              | 5               | 8           | 11                          | ms   | L       |

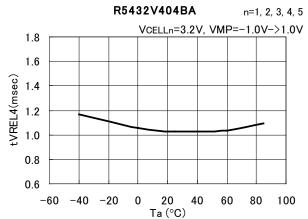

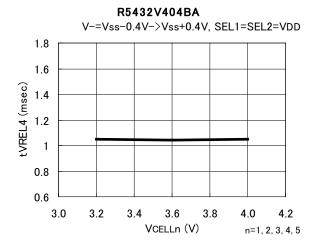

| tV <sub>rel4</sub> | Output delay of release from<br>Excess<br>charge-current threshold | V <sub>DD</sub> =Vc1, V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENS=Vss,VMP=-1.0V→1.0V                                      | 0.7             | 1.2         | 1.7                         | ms   | L       |

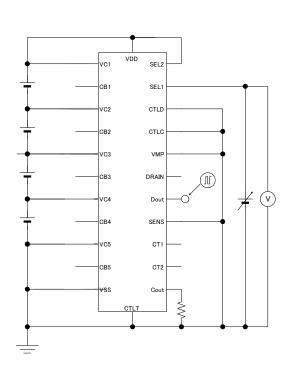

| VIH1               | SEL1 pin "H" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>-0.3     |             | Vdd<br>+0.3                 | V    | М       |

| VIM1               | SEL1 pin "M" input voltage                                         | VDD=Vc1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | 4.0             |             | V <sub>DD</sub> /2<br>-0.5V | V    | М       |

| VIL1               | SEL1 pin "L" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vss<br>-0.3     |             | Vss<br>+1.0                 | V    | М       |

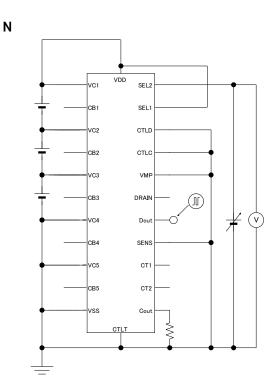

| VIH2               | SEL2 pin "H" input voltage                                         | VDD=Vc1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>-0.3     |             | Vdd<br>+0.3                 | V    | N       |

| Vim2               | SEL2 pin "M" input voltage                                         | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.2V<br>(n=1,2,3,4,5)                                                    | 4.0             |             | Vdd/2<br>-0.5V              | V    | N       |

| VIL2               | SEL2 pin "L" input voltage                                         | V <sub>DD</sub> =V <sub>C</sub> , VCELLn =3.2V<br>(n=1,2,3,4,5)                                                                  | Vss<br>-0.3     |             | Vss<br>+0.3                 | V    | N       |

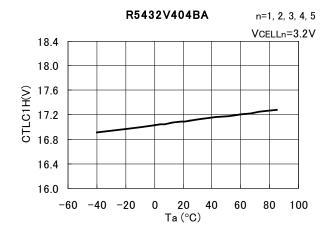

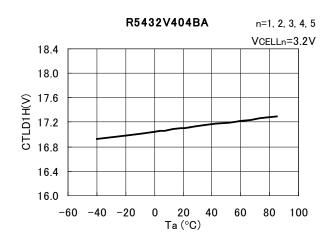

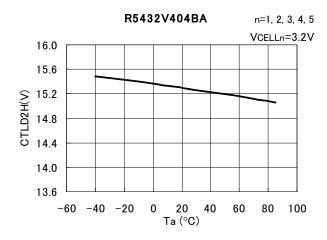

| Стьс1н             | C⊤∟c pin "H1" input voltage                                        | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>+2.0     |             |                             | V    | 0       |

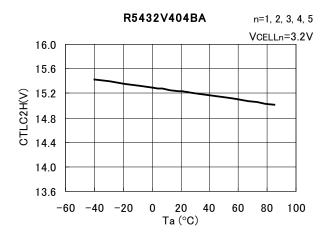

| Стьс2н             | C⊤∟c pin "H2" input voltage                                        | Vdd=Vc1, VCELLn =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>-0.3     |             | Vdd<br>+0.3                 | V    | 0       |

| CTLC1L             | C⊤∟c pin "L" input voltage                                         | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.2V<br>(n=1,2,3,4,5)                                                    | Vss<br>-0.3     |             | Vss<br>+0.3                 | V    | 0       |

| Ctld1h             | CTLD pin "H1" input voltage                                        | VDD=Vc1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>+2.0     |             |                             | V    | Р       |

| Ctld2h             | C⊤∟⊳ pin "H2" input voltage                                        | Vdd=Vc1, Vcelln =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vdd<br>-0.3     |             | V <sub>DD</sub><br>+0.3     | V    | Р       |

| Ctld1l             | C⊤∟⊳ pin "L" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                                           | Vss<br>-0.3     |             | Vss<br>+0.3                 | V    | Р       |

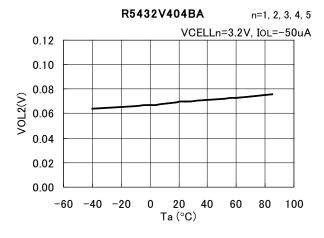

| Vol2               | Dout Nch ON voltage                                                | IOL=50µA, VDD=Vc1, CTLD=VDD<br>VCELLN =3.2V (n=1,2,3,4,5)                                                                        |                 | 0.1         | 0.5                         | V    | Q       |

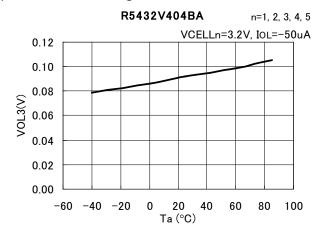

| Vol3               | DRAIN Nch ON voltage                                               | IOL=50μA, VDD=Vc1,<br>VCELLn =3.2V (n=1,2,3,4,5)                                                                                 |                 | 0.1         | 0.5                         | V    | R       |

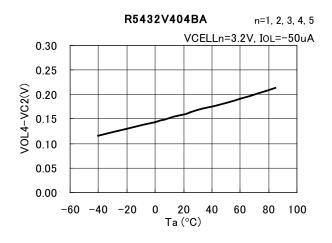

| Vol4               | CB1 Nch ON voltage                                                 | IOL=50µA, VDD=VC1,<br>VCELLN=3.2V (n=1,2,3,4,5)                                                                                  |                 | Vc2<br>+0.2 | Vc2<br>+0.5                 | V    | s       |

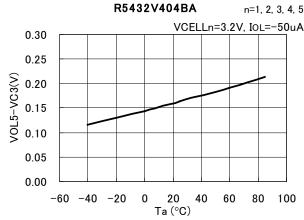

| Vol5               | CB2 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>Vcelln=3.2V (n=1,2,3,4,5)                                                                                  |                 | Vc₃<br>+0.2 | Vс₃<br>+0.5                 | V    | S       |

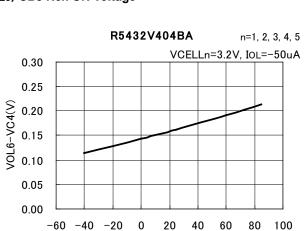

| Vol6               | CB3 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>VCELLn=3.2V (n=1,2,3,4,5)                                                                                  |                 | Vc4<br>+0.2 | Vc4<br>+0.5                 | V    | s       |

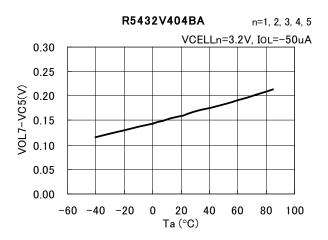

| Vol7               | CB4 Nch ON voltage                                                 | IOL=50µA, VDD=Vc1,<br>VCELLN=3.2V (n=1,2,3,4,5)                                                                                  |                 | Vc5<br>+0.2 | Vc5<br>+0.5                 | V    | s       |

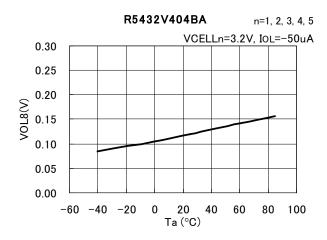

| Vol8               | CB5 Nch ON voltage                                                 | IOL=50µA, VDD=VC1,<br>VCELLn=3.2V (n=1,2,3,4,5)                                                                                  |                 | 0.2         | 0.5                         | V    | s       |

NO.EA-263-160711

| Symbol | Items                                    | Conditions                                                                                                              | Min.           | Тур.                    | Max. | Unit | Circuit |

|--------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------|------|------|---------|

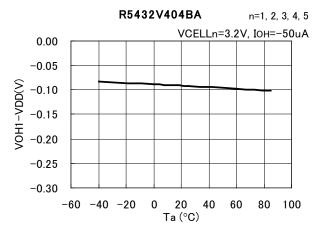

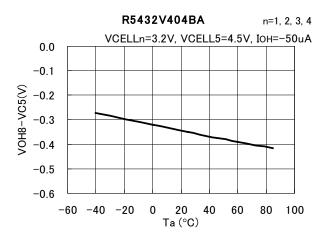

| Vон1   | Cout Pch ON voltage                      | IOH=-50μA, Vdd=Vc1,<br>VCELLn =3.2V (n=1,2,3,4,5)<br>Ctlc=Vss                                                           | Vdd<br>-0.5    | V <sub>DD</sub><br>-0.1 |      | V    | т       |

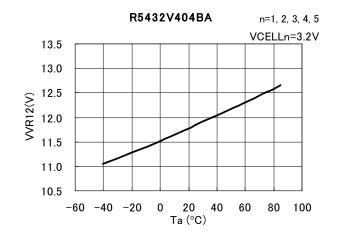

| Vvr12  | VR 12V output voltage (*1)               | IOH=-5μA, VDD=VC1, CTLD=VSS,<br>VCELL=3.2V (n=1, 2, 3, 4, 5)<br>Measured to draw the current<br>through Dout            | 10             | 12                      | 14   | v    | U       |

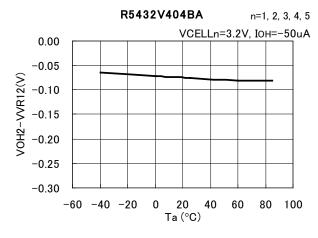

| Vон2   | Dout Pch ON voltage (*1)                 | IOH=-50μA, VDD=Vc1,<br>VCELLn =3.2V (n=1,2,3,4,5)<br>CTLD= Vss                                                          | Vvr12<br>-0.5V | Vvr12<br>-0.1V          |      | V    | U       |

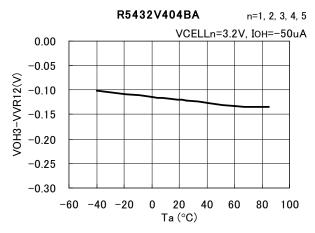

| Vонз   | DRAIN Pch ON voltage (*1)                | IOH=-50μA, VDD=VC1,<br>VCELLN =3.2V (n=1,2,3,4,5)<br>SENS =VMP =4.0V                                                    | Vvr12<br>-0.5V | Vvr12<br>-0.1V          |      | V    | V       |

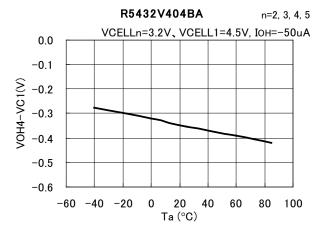

| Vон4   | CB1 Pch ON voltage                       | Іон=-50µА, Vdd=Vc1, Vc1=4.5V,<br>Vcelln=3.2V (n=2, 3, 4, 5)                                                             | Vc1<br>-0.5    | Vc1<br>-0.3             |      | V    | W       |

| Voh5   | CB2 Pch ON voltage                       | Іон=-50µА, Vdd=Vc1, Vc1=4.5V,<br>Vcelln=3.2V (n=1, 3, 4, 5)                                                             | Vc2<br>-0.5    | Vc2<br>-0.3             |      | V    | W       |

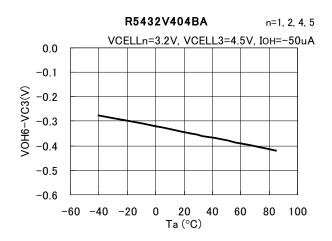

| Vон6   | CB3 Pch ON voltage                       | Іон=-50µA, Vdd=Vc1, Vc1=4.5V,<br>Vcelln=3.2V (n=1, 2, 4, 5)                                                             | Vсз<br>-0.5    | Vc₃<br>-0.3             |      | V    | W       |

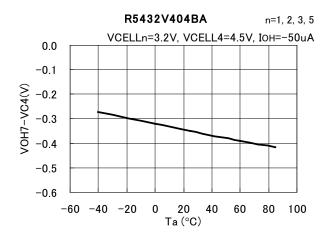

| Vон7   | CB4 Pch ON voltage                       | Іон=-50µА, Vdd=Vc1,<br>Vc1=4.5V, Vcelln=3.2V<br>(n=1, 2, 3, 5)                                                          | Vc4<br>-0.5    | Vc4<br>-0.3             |      | v    | W       |

| Vон8   | CB5 Pch ON voltage                       | Ioh=-50μA, Vdd=Vc1,<br>Vc1=4.5V, Vcelln=3.2V<br>(n=1, 2, 3, 4)                                                          | Vc₅<br>-0.5    | Vc₅<br>-0.3             |      | V    | W       |

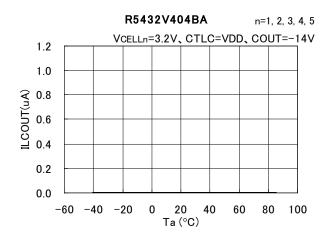

| ILCOUT | Cout pin off leak current                | VDD=VC1, VCELLN=3.2V<br>(n=1, 2, 3, 4, 5)<br>CTLC=VDD, COUT=-14V                                                        | -0.1           |                         |      | μA   | х       |

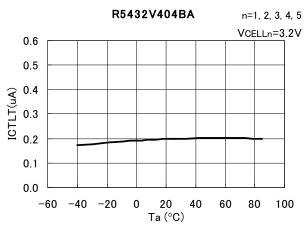

| Істіт  | C⊤∟⊤ Charge Current                      | VDD=VC1, VCELLN=3.2V<br>(n=1, 2, 3, 4, 5)                                                                               | 145            | 205                     | 264  | nA   | Y       |

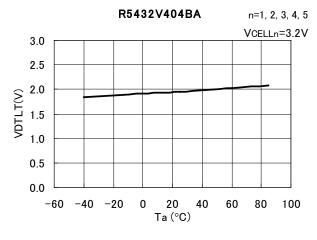

| Vdtlt  | CTLT detector threshold                  | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.2V<br>(n=1, 2, 4, 5)<br>V <sub>C3</sub> =V <sub>D1</sub> +0.2V | 1.58           | 2.00                    | 2.42 | V    | Z       |

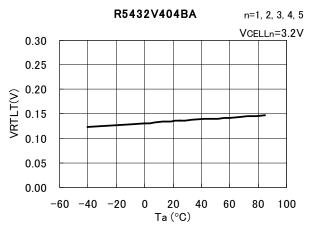

| Vrtlt  | CTLT released voltage                    | Vdd=Vc1, Vcelln=3.2V<br>(n=1, 2, 3, 4, 5)                                                                               | 0.07           | 0.13                    | 0.19 | V    | Z       |

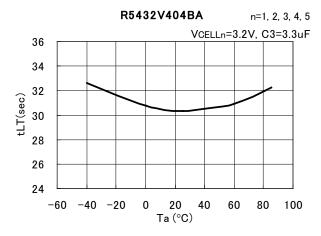

| tLT    | Disconnection detection<br>Test Interval | $\begin{array}{l} C_{CTLT}\times (V_{DTLT}-V_{RTLT})/I_{CTLT}\\ C_{CTLT}=3.3 \mu F \end{array}$                         | 21             | 30                      | 39   | s    | -       |

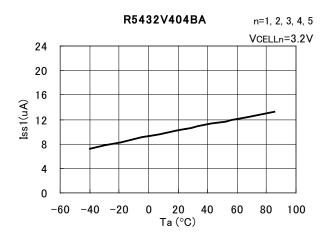

| Iss1   | Supply Currnt1                           | VDD=VC1,COUT=OPEN<br>VCELLN=VDET1N-0.4V<br>(n=1, 2, 3, 4, 5)                                                            |                | 12                      | 30   | μA   | а       |

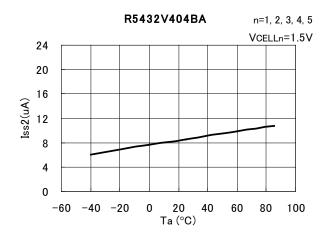

| lss2   | Supply Currnt2                           | VDD=Vc1,Cout=OPEN<br>Vcelln=1.5V<br>(n=1, 2, 3, 4, 5)                                                                   |                | 10                      | 25   | μA   | а       |

\* VCELLn=CELLn voltage n=1, 2, 3, 4, 5

(\*1) If VDD pin voltage becomes lower than the output of the regulator, the output voltage becomes almost equal to VDD.

#### **RECOMMENDED OPERATING CONDITIONS (ELECTRICAL CHARACTERISTICS)**

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if when they are used over such conditions by momentary electronic noise or surge. The semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

NO.EA-263-160711

# • R5432VxxxBB/BC

Unless otherwise specified, Ta=25°C

| Symbol         | Items                                                                 | Conditions                                                                                                                      | Min.                    | Тур.            | Max.                                                    | Unit | Circuit |

|----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|---------------------------------------------------------|------|---------|

| VDD1           | Operating input voltage                                               | VDD-Vss                                                                                                                         | 2                       | Typ.            | 25                                                      | V    | -       |

| VDET1 <b>N</b> | CELLn Overcharge threshold<br>(n=1,2,3,4,5)                           | Detect rising edge of supply voltage                                                                                            | VDET1N<br>-0.025        | Vdet1n          | VDET1N<br>+0.025                                        | V    | А       |

| Vrel1n         | CELLn Overcharge released<br>Voltage (n=1,2,3,4,5)                    | Detect falling edge of supply voltage                                                                                           | Vrel1n<br>-0.050        | Vrel1n          | V <sub>REL1</sub> n<br>+0.050                           | V    | А       |

| tVdet1         | Output delay of overcharge                                            | V <sub>DD</sub> =V <sub>C1</sub> ,V <sub>CELL</sub> n=3.5V<br>(n=2,3,4,5), V <sub>CELL</sub> 1=3.5V→4.5V                        | 0.7                     | 1.0             | 1.3                                                     | S    | В       |

| tVREL1         | Output delay of<br>release from overcharge                            | Vdd=Vc1, Vcelln=3.5V<br>(n=2,3,4,5), Vcell1=4.5V→3.5V                                                                           | 11                      | 16              | 21                                                      | ms   | В       |

| Vcbdn          | CELLn balance threshold<br>(n=1,2,3,4,5)                              | Detect rising edge of supply voltage                                                                                            | Vсво <b>n</b><br>-0.025 | Vсвdn           | Vсвол<br>+0.025                                         | V    | С       |

| Vcbrn          | CELLn balance<br>released threshold<br>(n=1,2,3,4,5)                  | Detect falling edge of supply<br>voltage                                                                                        | Vсвrn<br>-0.050         | Vcbrn           | Lower<br>of<br>VcBRN<br>+0.050<br>or<br>VcBDN<br>+0.025 | V    | С       |

| Vdet2n         | CELLn Overdischarge<br>threshold (n=1,2,3,4,5)                        | Detect falling edge of supply voltage                                                                                           | Vdet2n<br>×0.975        | Vdet2n          | Vdet2n<br>×1.025                                        | V    | D       |

| Vrel2n         | CELLn Overdischarge released Voltage (n=1,2,3,4,5)                    | Detect rising edge of supply voltage                                                                                            | Vrel2n<br>×0.975        | Vrel2n          | Vrel2n<br>×1.025                                        | V    | D       |

| ICT1           | CT1 charge Current                                                    | Vdd=Vc1, Vcelln=3.5V<br>(n=2, 3, 4, 5), Vcell1=3.5V→1.5V                                                                        | 350                     | 500             | 650                                                     | nA   | E       |

| VDCT1          | CT1 detector voltage                                                  | Vdd=Vc1, Vcelln=3.5V<br>(n=2, 3, 4, 5), Vcell1=1.5V                                                                             | 1.48                    | 1.85            | 2.22                                                    | V    | F       |

| tVdet2         | Output delay of overdischarge                                         | tVDET2=CCT1×VDCT1/ICT1<br>CCT1=33nF                                                                                             | 89                      | 128             | 167                                                     | ms   | -       |

| tVrel2         | Output delay of release from overdischarge                            | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>V <sub>CELL1</sub> =1.5V→3.5V         | 0.7                     | 1.2             | 1.7                                                     | ms   | G       |

| Vdet31         | Excess discharge-current threshold1                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage  | Vdet31<br>-0.020        | Vdet31          | Vdet31<br>+0.020                                        | V    | Н       |

| Vdet32         | Excess discharge-current<br>Threshold2                                | VDD=Vc1, VCELLN=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage                                         | Vdet32<br>-0.070        | Vdet32          | Vdet32<br>+0.070                                        | V    | I       |

| Vrel3          | Output delay of<br>release from Excess<br>discharge-current threshold | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), SENSE=0V<br>Detect falling edge of supply voltage | Vdet31<br>×0.50         | Vdet31<br>×0.75 | Vdet31<br>×1.00                                         | V    | Н       |

| Іст231         | CT2 Charge Current1                                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENSE=Vss→0.4V                                 | 350                     | 500             | 650                                                     | nA   | I       |

| Іст232         | CT2 Charge Current2                                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENSE=Vss→0.7V                                 | 2.0                     | 3.0             | 4.0                                                     | μA   | I       |

| VDCT2          | CT2 Charge voltage                                                    | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=2,3,4,5)<br>SENSE=0.4V, VMP=4.0V                             | 1.23                    | 1.55            | 1.87                                                    | V    | J       |

| tVdet31        | Output delay of Excess<br>discharge-current threshold1                | tvdet31=Cct2×Vdct2/Ict231<br>Cct2=3.3nF                                                                                         | 7.3                     | 10.8            | 14.7                                                    | ms   | -       |

| tVdet32        | Output delay of Excess<br>discharge-current Threshold2                | tvdet32=Cct2×Vdct2/Ict232<br>Cct2=3.3nF                                                                                         | 1.25                    | 1.80            | 2.40                                                    | ms   | -       |

| tVREL3         | Output delay of release from<br>Excess<br>discharge-current Threshold | V <sub>DD</sub> =V <sub>C1</sub> , VCELLn=3.5V<br>(n=1,2,3,4,5)<br>SENS=0.4V, VMP= 4.0V                                         | 0.7                     | 1.2             | 1.7                                                     | ms   | Н       |

NO.EA-263-160711

| Symbol             | Items                                                              | Conditions                                                                                               | Min.            | Тур.        | Max.                    | Unit | Circuit |

|--------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------|-------------|-------------------------|------|---------|

| Vshort             | Short protection voltage                                           | VDD=Vc1, VCELLn=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising of supply voltage                       | 0.7             | 1.0         | 1.7                     | V    | К       |

| tshort             | Output Delay of Short protection                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENS=0.0V→2.0V,VMP=4.0V | 180             | 300         | 550                     | μs   | к       |

| Vdet4              | Excess charge-current threshold                                    | VDD=VC1, VCELLN=3.5V<br>(n=1,2,3,4,5), VMP=-1.0V<br>Detect falling edge of supply voltage                | Vdet4<br>-0.030 | Vdet4       | Vdet4<br>+0.030         | V    | L       |

| tVdet4             | Output delay of Excess charge-current threshold                    | V <sub>DD</sub> =V <sub>C1</sub> , VCELLn =3.5V<br>(n=1,2,3,4,5)<br>SENS=0.0V→-1.0V                      | 5               | 8           | 11                      | ms   | L       |

| tV <sub>rel4</sub> | Output delay of release from<br>Excess charge-current<br>threshold | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENS=Vss,VMP=-1.0V→1.0V | 0.7             | 1.2         | 1.7                     | ms   | L       |

| VIH1               | SEL1 pin "H" input voltage                                         | Vdd=Vc1, Vcelln =3.2V<br>(n=1,2,3,4,5)                                                                   | Vdd<br>-0.3     |             | V <sub>DD</sub><br>+0.3 | V    | М       |

| VIM1               | SEL1 pin "M" input voltage                                         | VDD=Vc1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | 4.0             |             | Vdd/2<br>-0.5V          | V    | М       |

| VIL1               | SEL1 pin "L" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | Vss<br>-0.3     |             | Vss<br>+1.0             | V    | М       |

| VIH2               | SEL2 pin "H" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | Vdd<br>-0.3     |             | Vdd<br>+0.3             | V    | N       |

| VIM2               | SEL2 pin "M" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | 4.0             |             | Vdd/2<br>-0.5V          | V    | N       |

| VIL2               | SEL2 pin "L" input voltage                                         | V <sub>DD</sub> =V <sub>C</sub> , VCELLn =3.2V<br>(n=1,2,3,4,5)                                          | Vss<br>-0.3     |             | Vss<br>+0.3             | V    | Ν       |

| CTLC1H             | C⊤∟c pin "H1" input voltage                                        | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | VDD<br>+2.0     |             |                         | V    | 0       |

| Ctlc2h             | C⊤∟c pin "H2" input voltage                                        | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | Vdd<br>-0.3     |             | Vdd<br>+0.3             | V    | 0       |

| CTLC1L             | C⊤∟c pin "L" input voltage                                         | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.2V<br>(n=1,2,3,4,5)                            | Vss<br>-0.3     |             | Vss<br>+0.3             | V    | 0       |

| Ctld1h             | CTLD pin "H1" input voltage                                        | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | VDD<br>+2.0     |             |                         | V    | Р       |

| Ctld2h             | Стьр pin "H2" input voltage                                        | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | Vdd<br>-0.3     |             | V <sub>DD</sub><br>+0.3 | V    | Р       |

| Ctld1l             | Стьр pin "L" input voltage                                         | VDD=VC1, VCELLN =3.2V<br>(n=1,2,3,4,5)                                                                   | Vss<br>-0.3     |             | Vss<br>+0.3             | V    | Р       |

| Vol2               | Dout Nch ON voltage                                                | IOL=50µA, Vdd=Vc1, Ctld=Vdd<br>Vcelln =3.2V (n=1,2,3,4,5)                                                |                 | 0.1         | 0.5                     | V    | Q       |

| Vol3               | DRAIN Nch ON voltage                                               | IOL=50µA, Vdd=Vc1,<br>Vcelln =3.2V (n=1,2,3,4,5)                                                         |                 | 0.1         | 0.5                     | V    | R       |

| Vol4               | CB1 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>VCELLn=3.2V (n=1,2,3,4,5)                                                          |                 | Vc2<br>+0.2 | Vc2<br>+0.5             | V    | S       |

| Vol5               | CB2 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>VCelln=3.2V (n=1,2,3,4,5)                                                          |                 | Vсз<br>+0.2 | Vc₃<br>+0.5             | V    | S       |

| Vol6               | CB3 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>VCELLn=3.2V (n=1,2,3,4,5)                                                          |                 | Vc4<br>+0.2 | Vc4<br>+0.5             | V    | S       |

| Vol7               | CB4 Nch ON voltage                                                 | IOL=50µA, Vdd=Vc1,<br>Vcelln=3.2V (n=1,2,3,4,5)                                                          |                 | Vc₅<br>+0.2 | Vc₅<br>+0.5             | V    | S       |

| Vol8               | CB5 Nch ON voltage                                                 | IOL=50μA, Vdd=Vc1,<br>VCelln=3.2V (n=1,2,3,4,5)                                                          |                 | 0.2         | 0.5                     | V    | S       |

| Vон1               | Cout Pch ON voltage                                                | IOH=-50μA, Vdd=Vc1,<br>VCELLN =3.2V (n=1,2,3,4,5)<br>CTLC=Vss                                            | Vdd-0.5         | Vdd-0.1     |                         | V    | Т       |

NO.EA-263-160711

| Symbol  | Items                                                                       | Conditions                                                                                                   | Min.           | Тур.           | Max.  | Unit | Circuit |

|---------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|----------------|-------|------|---------|

| Vvr12   | VR 12V output voltage(*1)                                                   | IOH=-5µA, VDD=VC1, CTLD=Vss,<br>VCELL=3.2V (n=1, 2, 3, 4, 5)<br>Measured to draw the current<br>through Dout | 10             | 12             | 14    | v    | U       |

| Vон2    | Dout Pch ON voltage(*1)                                                     | IOH=-50µA, Vdd=Vc1,<br>VCELLN =3.2V (n=1,2,3,4,5)<br>CTLD= Vss                                               | Vvr12<br>-0.5V | Vvr12<br>-0.1V |       | V    | U       |

| Vонз    | DRAIN Pch ON voltage(*1)                                                    | IOH=-50µA, VDD=Vc1,<br>VCELLN =3.2V (n=1,2,3,4,5)<br>SENS =VMP =4.0V                                         | Vvr12<br>-0.5V | Vvr12<br>-0.1V |       | V    | V       |

| Vон4    | CB1 Pch ON voltage                                                          | Іон=-50µА, Vdd=Vc1,<br>Vc1=4.5V,<br>Vcelln=3.2V (n=2, 3, 4, 5)                                               | Vc1<br>-0.5    | Vc1<br>-0.3    |       | v    | W       |

| Voh5    | CB2 Pch ON voltage                                                          | IOH=-50μA, VDD=Vc1, Vc1=4.5V,<br>Vcelln=3.2V (n=1, 3, 4, 5)                                                  | Vc2<br>-0.5    | Vc2<br>-0.3    |       | V    | W       |

| Vон6    | CB3 Pch ON voltage                                                          | Іон=-50µА, Vdd=Vc1,<br>Vc1=4.5V,<br>Vcelln=3.2V (n=1, 2, 4, 5)                                               | Vc₃<br>-0.5    | Vсз<br>-0.3    |       | v    | W       |

| Vон7    | CB4 Pch ON voltage                                                          | Іон=-50µА, Vdd=Vc1,<br>Vc1=4.5V, Vcelln=3.2V<br>(n=1, 2, 3, 5)                                               | Vc4<br>-0.5    | Vc4<br>-0.3    |       | V    | W       |

| Vон8    | CB5 Pch ON voltage                                                          | Іон=-50µА, Vdd=Vc1,<br>Vc1=4.5V, Vcelln=3.2V<br>(n=1, 2, 3, 4)                                               | Vc₅<br>-0.5    | Vc₅<br>-0.3    |       | v    | w       |

| Ιιςουτ  | Cout pin off leak current                                                   | VDD=VC1, VCELLN=3.2V<br>(n=1, 2, 3, 4, 5)<br>CTLC=VDD, COUT=-14V                                             | -0.1           |                |       | μA   | х       |

| ICTLT   | C⊤∟⊤ Charge Current                                                         | VDD=Vc1, VCELLN=3.2V<br>(n=1, 2, 3, 4, 5)                                                                    | 145            | 205            | 264   | nA   | Y       |

| Vdtlt   | CTLT detector threshold                                                     | VDD=VC1, VCELLN=3.2V<br>(n=1, 2, 4, 5)<br>VC3=VD1+0.2V                                                       | 1.58           | 2.00           | 2.42  | v    | Z       |

| Vrtlt   | CTLT released voltage                                                       | VDD=VC1, VCELLN=3.2V<br>(n=1, 2, 3, 4, 5)                                                                    | 0.07           | 0.13           | 0.19  | V    | Z       |

| tLT     | Disconnection detection<br>Test Interval                                    | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                        | 21             | 30             | 39    | s    | -       |

| Vnochgn | CELLn charge inhibit<br>maximum voltage<br>(n=1,2,3,4,5)-for<br>R5432V4xxxB | VDD=VC1                                                                                                      |                |                | 1.100 | v    | A       |

| Iss1    | Supply Currnt1                                                              | VDD=VC1,COUT=OPEN<br>VCELLN=VDET1N-0.4V<br>(n=1, 2, 3, 4, 5)                                                 |                | 12             | 30    | μΑ   | а       |

| Iss2    | Supply Currnt2                                                              | Vdd=Vc1,Cout=OPEN<br>Vcelln=1.5V (n=1, 2, 3, 4, 5)                                                           |                | 10             | 25    | μΑ   | а       |

\* VCELLN=CELLn voltage n=1, 2, 3, 4, 5

(\*1) If VDD pin voltage becomes lower than the output of the regulator, the output voltage becomes almost equal to VDD.

NO.EA-263-160711

# • R5432VxxxBD

Unless otherwise specified, Ta=25°C

|         |                                                                       |                                                                                                                                 |                  |                 | moc opcom                                                                      |      |         |

|---------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------------------------------------------------------------------|------|---------|

| Symbol  | Items                                                                 | Conditions                                                                                                                      | Min.             | Тур.            | Max.                                                                           | Unit | Circuit |

| VDD1    | Operating input voltage                                               | Vdd-Vss                                                                                                                         | 2                |                 | 25                                                                             | V    | -       |

| Vdet1n  | CELLn Overcharge threshold<br>(n=1,2,3,4,5)                           | Detect rising edge of supply voltage                                                                                            | Vdet1n<br>-0.025 | Vdet1n          | Vdet1n<br>+0.025                                                               | V    | А       |

| Vrel1n  | CELLn Overcharge released<br>Voltage (n=1,2,3,4,5)                    | Detect falling edge of supply voltage                                                                                           | Vrel1n<br>-0.050 | Vrel1n          | V <sub>REL1</sub> n<br>+0.050                                                  | V    | А       |

| tVdet1  | Output delay of overcharge                                            | Vdd=Vc1,Vcelln=3.5V<br>(n=2,3,4,5), Vcell1=3.5V→4.5V                                                                            | 0.7              | 1.0             | 1.3                                                                            | s    | В       |

| tVREL1  | Output delay of<br>release from overcharge                            | Vdd=Vc1, Vcelln=3.5V<br>(n=2,3,4,5), Vcell1=4.5V→3.5V                                                                           | 11               | 16              | 21                                                                             | ms   | В       |

| Vcbdn   | CELLn balance threshold<br>(n=1,2,3,4,5)                              | Detect rising edge of supply voltage                                                                                            | Vсвdn<br>-0.025  | Vcbdn           | Vсвол<br>+0.025                                                                | V    | С       |

| Vcbrn   | CELLn balance<br>released threshold<br>(n=1,2,3,4,5)                  | Detect falling edge of supply voltage                                                                                           | Vcbrn<br>-0.050  | Vcbrn           | Lower of<br>V <sub>CBR</sub> n<br>+0.050<br>or<br>V <sub>CBD</sub> n<br>+0.025 | V    | с       |

| Vdet2n  | CELLn Overdischarge<br>threshold (n=1,2,3,4,5)                        | Detect falling edge of supply voltage                                                                                           | Vdet2n<br>×0.975 | Vdet2n          | Vdet2n<br>×1.025                                                               | V    | D       |

| VREL2N  | CELLn Overdischarge released Voltage<br>(n=1,2,3,4,5)                 | Detect rising edge of supply voltage                                                                                            | VREL2n<br>×0.975 | VREL2N          | V <sub>REL2</sub> n<br>×1.025                                                  | V    | D       |

| ICT1    | CT1 charge Current                                                    | Vdd=Vc1, Vcelln=3.5V<br>(n=2, 3, 4, 5), Vcell1=3.5V→1.5V                                                                        | 350              | 500             | 650                                                                            | nA   | E       |

| VDCT1   | CT1 detector voltage                                                  | Vdd=Vc1, Vcelln=3.5V<br>(n=2, 3, 4, 5), Vcell1=1.5V                                                                             | 1.48             | 1.85            | 2.22                                                                           | V    | F       |

| tVdet2  | Output delay of overdischarge                                         | tVdet2=Cct1×Vdct1/lct1<br>Cct1=33nF                                                                                             | 89               | 128             | 167                                                                            | ms   | -       |

| tVREL2  | Output delay of release from overdischarge                            | VDD=Vc1, Vcelln=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Vcell1=1.5V→3.5V                                                             | 0.7              | 1.2             | 1.7                                                                            | ms   | G       |

| Vdet31  | Excess discharge-current threshold1                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage  | Vdet31<br>-0.020 | Vdet31          | Vdet31<br>+0.020                                                               | V    | Н       |

| Vdet32  | Excess discharge-current<br>Threshold2                                | VDD=Vc1, VcELLn=3.5V<br>(n=1,2,3,4,5), VMP=4.0V<br>Detect rising edge of supply voltage                                         | Vdet32<br>-0.055 | Vdet32          | Vdet32<br>+0.055                                                               | V    | I       |

| Vrel3   | Output delay of<br>release from Excess<br>discharge-current threshold | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n=3.5V<br>(n=1,2,3,4,5), SENSE=0V<br>Detect falling edge of supply voltage | Vdet31<br>×0.50  | Vdet31<br>×0.75 | Vdet31<br>×1.00                                                                | V    | Н       |

| Іст231  | CT2 Charge Current1                                                   | V <sub>DD</sub> =V <sub>C1</sub> , V <sub>CELL</sub> n =3.5V<br>(n=1,2,3,4,5)<br>SENSE=Vss→0.4V                                 | 350              | 500             | 650                                                                            | nA   | I       |

| Іст232  | CT2 Charge Current2                                                   | V <sub>DD</sub> =Vc1, VceLLn =3.5V<br>(n=1,2,3,4,5)<br>SENSE=Vss→0.7V                                                           | 2.0              | 3.0             | 4.0                                                                            | μA   | I       |

| VDCT2   | CT2 Charge voltage                                                    | VDD=Vc1, Vcelln =3.5V<br>(n=2,3,4,5)<br>SENSE=0.4V, VMP=4.0V                                                                    | 1.23             | 1.55            | 1.87                                                                           | V    | J       |

| tVdet31 | Output delay of Excess<br>discharge-current threshold1                | tvdet31=Cct2×Vdct2/Ict231<br>Cct2=3.3nF                                                                                         | 7.3              | 10.8            | 14.7                                                                           | ms   | -       |

| tVdet32 | Output delay of Excess<br>discharge-current Threshold2                | tvdet32=Cct2×Vdct2/Ict232<br>Cct2=3.3nF                                                                                         | 1.25             | 1.80            | 2.40                                                                           | ms   | -       |