# MMH0026 MMH0026C

## Specifications and Applications Information

## **DUAL MOS CLOCK DRIVER**

...designed for high-speed driving of highly capacitive loads in a MOS system.

- Fast Transition Times -- 20 ns with 1000 pF Load

- High Output Swing 20 Volts

- High Output Current Drive ± 1.5 Amperes

- High Repetition Rate 5.0 to 10 MHz Depending on Load

- MTTL and MDTL Compatible Inputs

- Low Power Consumption when in MOS "0" State 2.0 mW

- +5.0-Volt Operation for N-Channel MOS Compatibility

## DUAL MOS CLOCK DRIVER

SILICON MONOLITHIC INTEGRATED CIRCUIT

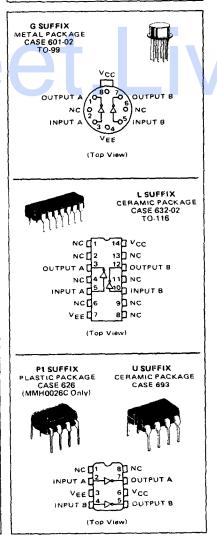

## MAXIMUM RATINGS (TA = +25°C unless otherwise noted.)

| Rating                              | Symbol           |                       | Value       |             | Unit     |

|-------------------------------------|------------------|-----------------------|-------------|-------------|----------|

| Differential Supply Voltage         | VCC-VEE          |                       | +22         |             | Vdc      |

| Input Current                       | l <sub>1</sub>   |                       | +100        |             | mA       |

| Input Voltage                       | Vį               | V <sub>EE</sub> + 5.5 |             |             | Vdc      |

| Peak Output Current                 | Opk              | ±1.5                  |             | A           |          |

| Junction Temperature                | Tj               | +175                  | +175        | +150        | <u> </u> |

| Operating Ambient Temperature Range | TA               | G                     | U,L         | P1          | °С       |

| MMH0026                             |                  | -55 to +125           | -55 to +125 |             |          |

| MMH0026C                            | 1                | 0 to +70              | 0 to +70    | 0 to +70    |          |

| Storage Temperature Range           | T <sub>stg</sub> | -65 to +150           | -65 to +150 | -65 to +150 | °C       |

# ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>-V<sub>EE</sub> = 10 V to 20 V, C<sub>L</sub> = 1000 pF, T<sub>A</sub> = -55 to +125°C for MMH0026 and 0 to +70°C for MMH0026C for min and max values; T<sub>A</sub> = +25°C for all typical values unless otherwise noted.)

| Cheracteristic                                                                                                                                                 | Symbol | Min                                    | Тур                         | Max                          | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------|-----------------------------|------------------------------|------|

| Logic "1" Level Input Voltage<br>VO ≅ VEE + 1.0 Vdc                                                                                                            | VIH    | VEE + 2.0                              | VEE + 1.5                   | -                            | Vdc  |

| Logic "1" Level Input Current V1 -VEE = 2.4 Vdc, V0 = VEE + 1.0 Vdc                                                                                            | ЧН     |                                        | 10                          | 15                           | mA   |

| Logic "0" Level Input Voltage VO = VCC -1.0 Vdc                                                                                                                | VIL    | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | VEE + 0.6                   | V <sub>EE</sub> + 0.4        | Vdc  |

| Logic "0" Level Input Current V1 -VEE = 0 Vdc, V0 = VCC -1.0 Vdc                                                                                               | l I L  |                                        | -0.005                      | -10                          | μА   |

| Logic ''0'' Level Output Voltage  V <sub>CC</sub> = +5.0 Vdc, V <sub>EE</sub> = -12 Vdc, V <sub>1</sub> = -11.6 Vdc  V <sub>1</sub> -V <sub>EE</sub> = 0.4 Vdc | Voн    | 4.0<br>V <sub>CC</sub> -1.0            | 4.3<br>V <sub>CC</sub> -0.7 | -<br>-                       | Vdc  |

| Logic ''1' Level Output Voltage  V <sub>CC</sub> = +5.0 Vdc, V <sub>EE</sub> = -12 Vdc, V <sub>I</sub> = -9.6 Vdc  V <sub>I</sub> -V <sub>EE</sub> = 2.4 Vdc   | VOL    |                                        | -11.5<br>VEE + 0.5          | -11<br>V <sub>EE</sub> + 1.0 | Vdc  |

| "On" Supply Current  VCC-VEE = 20 Vdc, V <sub>1</sub> -VEE = 2.4 Vdc                                                                                           | ICCL   | -                                      | 30                          | 40                           | mA   |

| "Off" Supply Current MMH0026C<br>VCC-VEE = 20 Vdc, VI -VEE = 0 V MMH0026                                                                                       | 1ссн   |                                        | 10 ~                        | 100<br>500                   | μА   |

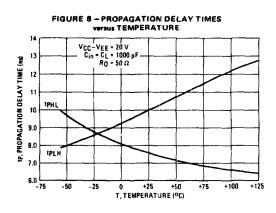

## SWITCHING CHARACTERISTICS (V<sub>CC</sub>-V<sub>EE</sub> = 10 V to 20 V, C<sub>L</sub> = 1000 pF, T<sub>A</sub> = 25°C)

| Propagation Time                          |            |                  | 1          | 1   |          | T   |

|-------------------------------------------|------------|------------------|------------|-----|----------|-----|

| High to Low                               | (Figure 2) | l tPHL           | 5.0        | 7.5 | 12       | ns  |

|                                           | (Figure 3) |                  | 1 ~        | 11  | <u> </u> | l.  |

| Low to High                               | (Figure 2) | tPLH             | 5.0        | 12  | 15       | 1   |

|                                           | (Figure 3) |                  | -          | 13  | { -      | [   |

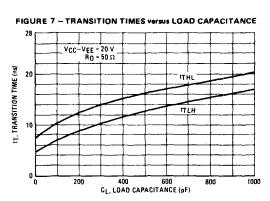

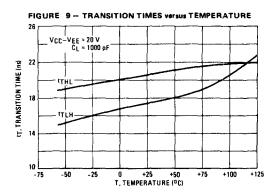

| Transition Time (High to Low)             |            | tтнь             |            | 1   | 1        | ns  |

| VCC-VEE = 20 Vdc, Ct = 250 pF             | (Figure 2) |                  | ] -        | 12  | 1 -      | 1   |

| VCC-VEE ≈ 20 Vdc, CL = 500 pF             | (Figure 2) |                  | <b>!</b> – | 15  | 18       | i i |

|                                           | (Figure 3) |                  | 1 -        | 30  | 40       | 1   |

| VCC-VEE = 20 Vdc, CL = 1000 pF            | (Figure 2) | j                | -          | 20  | 35       | 1   |

|                                           | (Figure 3) |                  | -          | 36  | 50       | ſ   |

| Transition Time (Low to High)             |            | <sup>†</sup> TLH |            | 1   |          | ns  |

| VCC-VEE = 20 Vdc, CL = 250 pF             | (Figure 2) |                  | } -        | 10  | _        | J   |

| VCC-VEE * 20 Vdc, C <sub>L</sub> = 500 pF | (Figure 2) | i                | _          | 12  | 16       | 1   |

|                                           | (Figure 3) |                  | 1 -        | 28  | 35       | 1   |

| VCC -VEE = 20 Vdc, CL = 1000 pF           | (Figure 2) | }                | <b>)</b> – | 17  | 25       | J   |

|                                           | (Figure 3) |                  | -          | 31  | 40       | 1   |

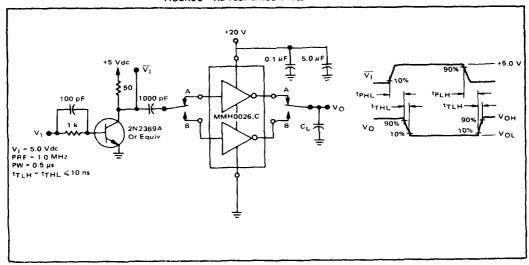

TEST CIRCUIT

FIGURE 2 - AC TEST CIRCUIT AND WAVEFORMS

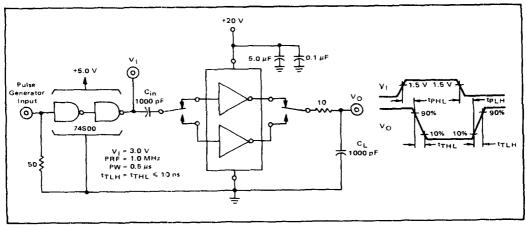

FIGURE 3 - AC TEST CIRCUIT AND WAVEFORMS

Circuit diagrams utilizing Motorola products are included as a means of illustrating typical semiconductor applications, consequently, complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and

is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

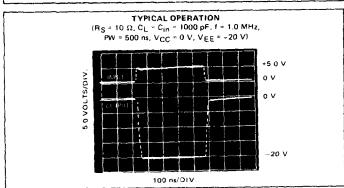

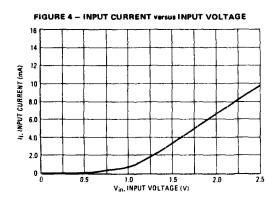

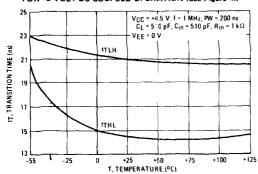

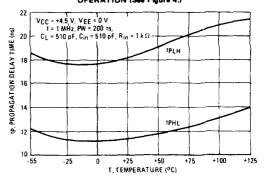

## TYPICAL CHARACTERISTICS

$(V_{CC} = +20 \text{ V}, V_{EE} = 0 \text{ V}, T_A = +25^{\circ}\text{C} \text{ unless otherwise noted.})$

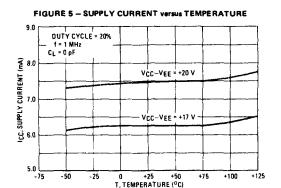

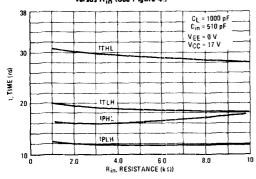

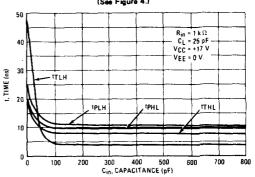

## TYPICAL CHARACTISTICS (continued)

$(V_{CC} = +20 \text{ V}, V_{EE} = 0 \text{ V}, T_A = +25^{\circ}\text{C} \text{ unless otherwise noted.})$

FIGURE 10 – TRANSITION TIME versus TEMPERATURE FOR +5 VOLT DC-COUPLED OPERATION (See Figure 4.)

FIGURE 11 — PROPAGATION DELAY TIME versus

TEMPERATURE FOR +5 VOLT DC-COUPLED

OPERATION (See Figure 4.)

FIGURE 12 – DC-COUPLED SWITCHING RESPONSE versus  $\mathbf{R}_{\text{in}}$  (See Figure 4.)

FIGURE 13 — DC-COUPLED SWITCHING versus Cin (See Figure 4.)

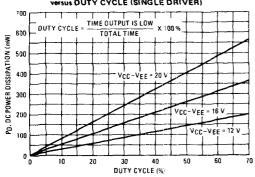

FIGURE 14 - MAXIMUM DC POWER DISSIPATION VORSUS DUTY CYCLE (SINGLE DRIVER)

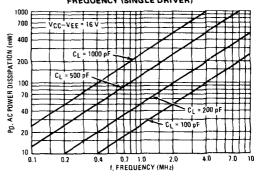

FIGURE 15 — AC POWER DISSIPATION versus FREQUENCY (SINGLE DRIVER)

#### APPLICATIONS INFORMATION

## **OPERATION OF THE MMH0026**

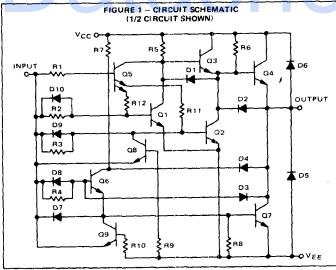

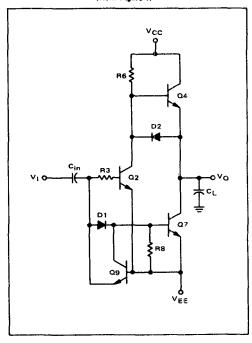

The simplified schematic diagram of MMH0026, shown in Figure 16, is useful in explaining the operation of the device. Figure 16 illustrates that as the input voltage level goes high, diode D1 provides an 0.7-volt "dead zone" thus ensuring that Q2 is turned "on" and Q4 is turned "off" before Q7 is turned "on". This prevents undesirable "current spiking" from the power supply, which would occur if Q7 and Q4 were allowed to be "on" simultaneously for an instant of time. Diode D2 prevents "zenering" of Q4 and provides an initial discharge path for the output capacitive load by way of Q2.

As the input voltage level goes low, the stored charge in  $\Omega 2$  is used advantageously to keep  $\Omega 2$  "on" and  $\Omega 4$  "off" until  $\Omega 7$  is "off". Again undesirable "current spiking" is prevented. Due to the external capacitor, the input side of  $C_{in}$  goes negative with respect to  $V_{EE}$  causing  $\Omega 9$  to conduct momentarily thus assuring rapid turn "off" of  $\Omega 7$ .

FIGURE 16 - SIMPLIFIED SCHEMATIC DIAGRAM

(Ref.: Figure 1)

The complete circuit, Figure 1, basically creates Darlington devices of transistors Q7, Q4 and Q2 in the simplified circuit of Figure 16. Note in Figure 1 that when the input goes negative with respect to VEE, cliodes D7 through D10 turn "on" assuring faster turn "off" of transistors Q1, Q2, Q6 and Q7. Resistor R6 insures that the output will charge to within one VBE voltage drop of the VCC supply.

#### SYSTEM CONSIDERATIONS

#### Overshoot:

In most system applications the output waveform of the MMH0026 will "overshoot" to some degree. However, "overshoot" can be eliminated or reduced by placing a damping resistor in series with the output. The amount of resistance required is given by:  $R_S=2\sqrt{L/C_L}$  where L is the inductance of the line and  $C_L$  is the load capacitance. In most cases a series of damping resistor in the range of 10-to-50 ohms will be sufficient. The damping resistor also affects the transition times of the outputs. The speed reduction is given by the formula:

$tTHL \approx tTLH = 2.2 RS CL (RS is the damping resistor).$

## Crosstalk:

The MMH0026 is sensitive to crosstalk when the output voltage level is high ( $V_Q \approx V_{CC}$ ). With the output in the high voltage level state, Q3 and Q4 are essentially turned "off". Therefore, negative-going crosstalk will pull the output down until Q4 turns "on" sufficiently to pull the output back towards  $V_{CC}$ . This problem can be minimized by placing a "bleeding" resistor from the output to ground. The "bleeding" resistor should be of sufficient size so that Q4 conducts only a few milliamperes. Thus, when noise is coupled, Q4 is already "on" and the line is quickly clamped by Q4. Also note that in Figure 1 D6 clamps the output one diode-voltage drop above  $V_{CC}$  for positive-going crosstalk.

## **Power Supply Decoupling:**

The decoupling of VCC and VEE is essential in most systems. Sufficient capacitive decoupling is required to supply the peak surge currents during switching. At least a  $0.1\text{-}\mu\text{F}$  to  $1.0\text{-}\mu\text{F}$  low inductive capacitor should be placed as close to each driver package as the layout will permit.

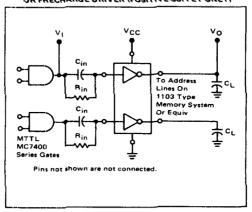

#### Input Driving:

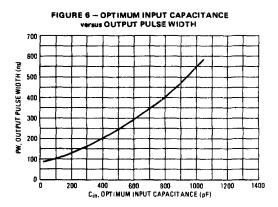

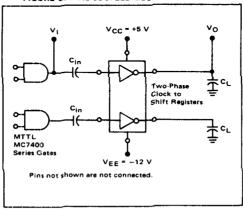

For those applications requiring split power supplies (VEE < GND), ac coupling, as illustrated in Figure 23, should be employed. Selection of the input capacitor size is determined by the desired output pulse width. Maximum performance is attained when the voltage at

the input of the MMH0026 discharges to just above the device's threshold voltage (about 1.5 V). Figure 6 shows optimum values for Cin versus the desired output pulse width. The value for Cin may be roughly predicted by:

$$C_{in} = (2 \times 10^{-3}) \text{ (PWO)}.$$

(1

For an output pulse width of 500 ns, the optimum value for  $C_{in}$  is:

$$C_{in} = (2 \times 10^{-3}) (500 \times 10^{-9}) = 1000 \text{ pF}.$$

If single supply operation is required (VEE = GND), then do coupling as illustrated in Figure 24 can be employed. For maximum switching performance, a speed-up capacitor should be employed with do coupling. Figures 12 and 13 show typical switching characteristics for various values of input resistance and capacitance.

#### POWER CONSIDERATIONS

Circuit performance and long-term circuit reliability are affected by die temperature. Normally, both are improved by keeping the integrated circuit junction temperatures low. Electrical power dissipated in the integrated circuit is the source of heat. This heat source increases the temperature of the die relative to some reference point, normally the ambient temperature. The temperature increase depends on the amount of power dissipated in the circuit and on the net thermal resistance between the heat source and the reference point. The basic formula for converting power dissipation into junction temperature is:

$$T_{J} = T_{A} + P_{D} (R_{\theta JC} + R_{\theta CA})$$

(2)

or

$$T_{J} = T_{A} + P_{D} (R_{\theta JA})$$

(3)

where

Ty = junction temperature

TA = ambient temperature

PD = power dissipation

section of this data sheet.

$R_{\theta,JC}$  = thermal resistance, junction to case

$R\theta CA$ = thermal resistance, case to ambient

$R_\theta J A =$  thermal resistance, junction to ambient. Power Dissipation for the MMH0026 MOS Clock Driver:

The power dissipation of the device (PD) is dependent on the following system requirements: frequency of operation, capacitive loading, output voltage swing, and duty cycle. This power dissipation, when substituted into equation (3), should not yield a junction temperature, TJ, greater than TJ(max) at the maximum encountered ambient temperature. TJ(max) is specified for three integrated circuit packages in the maximum ratings

TABLE 1 - THERMAL CHARACTERISTICS OF "G", "L", "P1", AND "U" PACKAGES

| PACKAGE TYPE<br>(Mounted in Socket) | $R_{	heta JA}$ ( | °C/W)<br>I Air | R <sub>θ</sub> JC ( <sup>O</sup> C/W)<br>Still Air |     |  |

|-------------------------------------|------------------|----------------|----------------------------------------------------|-----|--|

|                                     | MAX              | TYP            | MAX                                                | TYP |  |

| "G" (Metal Package)                 | 220              | 175            | 70                                                 | 40  |  |

| "L" (Ceramic Package)               | 150              | 100            | 50                                                 | 27  |  |

| "P1" (Plastic Package)              | 150              | 100            | 70                                                 | 40  |  |

| "U" (Ceramic Package)               | 150              | 100            | 50                                                 | 27  |  |

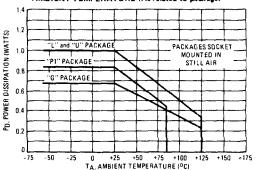

FIGURE 17 — MAXIMUM POWER DISSIPATION versus AMBIENT TEMPERATURE (As related to package)

With these maximum junction temperature values, the maximum permissible power dissipation at a given ambient temperature may be determined. This can be done with equations (2) or (3) and the maximum thermal resistance values given in Table 1 or alternately, by using the curves plotted in Figure 17. If, however, the power dissipation determined by a given system produces a calculated junction temperature in excess of the recommended maximum rating for a given package type, something must be done to reduce the junction temperature.

There are two methods of lowering the junction temperature without changing the system requirements. First, the ambient temperature may be reduced sufficiently to bring  $T_J$  to an acceptable value. Secondly, the  $R_\theta$ CA term can be reduced. Lowering the  $R_\theta$ CA term can be accomplished by increasing the surface area of the package with the addition of a heat sink or by blowing air across the package to promote improved heat dissipation.

The following examples illustrate the thermal considerations necessary to increase the power capability of the MMH0026.

Assume that the ceramic package is to be used at a maximum ambient temperature  $(T_A)$  of  $\pm 70^{\circ}$ C. From Table  $1:R_{\theta}JA(max)=150^{\circ}$ C/watt, and from the maximum rating section of the data sheet:  $T_J(max)=\pm 175^{\circ}$ C. Substituting the above values into equation (3) yields a maximum allowable power dissipation of 0:7 watts. Note that this same value may be read from Figure 17. Also note that this power dissipation value is for the device mounted in a socket.

Next, the maximum power consumed for a given system application must be determined. The power dissipation of the MOS clock driver is conveniently divided into dc and ac components. The dc power dissipation is given by:

$$P_{dc} = (V_{CC} - V_{EE}) \times (I_{CCL}) \times (Duty Cycle)$$

$$where I_{CCL} = 40 \text{ mA } (\frac{V_{CC} - V_{EE}}{20 \text{ V}}).$$

(4)

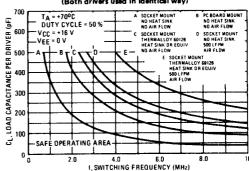

Note that Figure 14 is a plot of equation (4) for three values of (VCC-VEE). For this example, suppose that the MOS clock driver is to be operated with VCC = +16 V and VEE = GND and with a 50% duty cycle. From equation (4) or Figure 14, the dc power dissipation (per driver) may be found to be 256 mW. If both drivers within the package are used in an identical way, the total dc power is 512 mW. Since the maximum total allowable power dissipation is 700 mW, the maximum ac power that can be dissipated for this example becomes:

$$P_{ac} = 0.7 - 0.512 = 188 \, mW$$

The ac power for each driver is given by:

$$P_{ac} = (V_{CC} - V_{EE})^2 \times f \times C_L \qquad (5)$$

where  $f$  = frequency of operation

$$C_L = load \ capacitance \ (including \ all \ strays \ and \ wiring).$$

Figure 16 gives the maximum ac power dissipation versus switching frequency for various capacitive loads with  $V_{CC}$  = 16 V and  $V_{EE}$  = GND. Under the above conditions, and with the aid of Figure 15, the safe operating area beneath Curve A of Figure 18 can be generated.

Since both drivers have a maximum ac power dissipation of 188 mW, the maximum ac power per driver becomes 94 mW. A horizontal line intersecting all the capacitance load lines at the 94 mW level of Figure 15 will yield the maximum frequency of operation for each of the capacitive loads at the specified power level. By using the previous formulas and constants, a new safe operating area can be generated for any output voltage swing and duty cycle desired.

Note from Figure 18, that with highly capacitive loads, the maximum switching frequency is very low. The switching frequency can be increased by varying the following factors:

- (a) decrease TA

- (b) decrease the duty cycle

- (c) lower package thermal resistance (RθJA)

In most cases conditions (a) and (b) are fixed due to system requirements. This leaves only the thermal resistance  $R_{\theta}J_{A}$  that can be varied.

Note from equation (2) that the thermal resistance is comprised of two parts. One is the junction-to-case thermal resistance ( $R_{\theta, QQ}$ ) and the other is the case-to-ambient thermal resistance ( $R_{\theta, QQ}$ ). Since the factor  $R_{\theta, QQ}$  is a function of the die size and type of bonding employed, it cannot be varied. However, the  $R_{\theta, QQ}$  term can be changed as previously discussed, see Page 7.

FIGURE 18 – LOAD CAPACITANCE versus FREQUENCY

FOR "L" PACKAGE ONLY

(Both drivers used in identical way)

## Heat Sink Considerations:

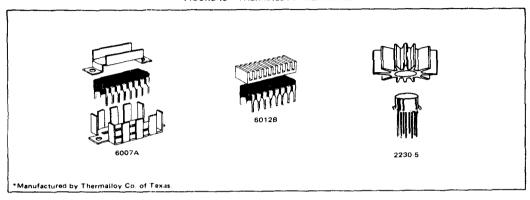

Heat sinks come in a wide variety of sizes and shapes that will accomodate almost any IC package made. Some of these heat sinks are illustrated in Figure 19. In the previous example, with the ceramic package, no heat sink and in a still air environment,  $R_{\theta}JA(max)was$  150°C/W.

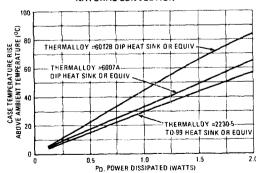

For the following example the Thermalloy 6012B type heat sink, or equivalent, is chosen. With this heat sink, the  $R_{\theta CA}$  for natural convection from Figure 20 is 44°C/W. From Table 1  $R_{\theta JC}(max)$  = 50°C/W for the ceramic

FIGURE 19 - THERMALLOY\* HEAT SINKS

package. Therefore, the new R $_{\theta}$ JA(max) with the 6012B heat sink added becomes:

$R_{\theta}JA(max) = 50^{\circ}C/W + 44^{\circ}C/W = 94^{\circ}C/W$ . Thus the addition of the heat sink has reduced  $R_{\theta}JA(max)$  from 150°C/W down to 94°C/W. With the heat sink, the maximum power dissipation by equation (3) at  $T_{A} = +70^{\circ}C$  is:

$$P_D = \frac{175^{\circ}C - 70^{\circ}C}{94^{\circ}C/W} = 1.11 \text{ watts.}$$

This gives approximately a 58% increase in maximum power dissipation. The safe operating area under Curve C of Figure 18 can now be generated as before with the aid of Figure 15 and equation (5).

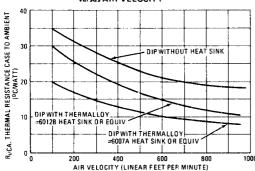

FIGURE 20 -- CASE TEMPERATURE RISE ABOVE AMBIENT versus POWER DISSIPATED USING NATURAL CONVECTION

#### Forced Air Considerations:

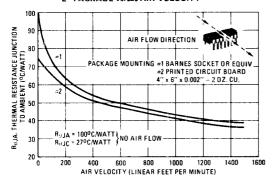

As illustrated in Figure 21, forced air can be employed to reduce the  $R_{\theta JA}$  term. Note, however, that this curve is expressed in terms of typical  $R_{\theta JA}$  rather than maximum  $R_{\theta JA}$  can be determined in the following manner:

From Table 1 the following information is known:

(a)

$$R_{\theta}JA(typ) = 100^{\circ} C/W$$

(b)  $R_{\theta}JC(typ) = 27^{\circ} C/W$

Since:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \tag{6}$$

Then:

$$R_{\theta}CA = R_{\theta}JA - R_{\theta}JC \tag{7}$$

Therefore, in still air

$R_{\theta}CA(typ) = 100^{\circ}C/W - 27^{\circ}C/W = 73^{\circ}C/W$ From Curve 1 of Figure 21 at 500 LFPM and equation (7).

$R_\theta CA(typ) \approx 53^{\circ}C/W - 27^{\circ}C/W = 26^{\circ}C/W.$  Thus  $R_\theta CA(typ)$  has changed from  $73^{\circ}C/W$  (still air) to  $26^{\circ}C/W$  (500 LFPM), which is a decrease in typical  $R_\theta CA$  by a ratio of 1:2.8. Since the typical value of  $R_\theta CA$  was reduced by a ratio of 1:2.8,  $R_\theta CA(max)$  of  $100^{\circ}C/W$  should also decrease by a ratio of 1:2.8.

This yields an R $\theta$ CA(max) at 500 LFPM of 36°C/W.

Therefore, from equation (6):

$R_\theta JA(max) = 50^{o}C/W + 36^{o}C/W = 86^{o}C/W.$  Therefore the maximum allowable power dissipation at 500 LFPM and  $T_A = +70^{o}C$  is from equation (3):

$$P_D = \frac{175^{\circ}C - 70^{\circ}C}{+86^{\circ}C/W} = 1.2 \text{ watts.}$$

FIGURE 21 — TYPICAL THERMAL RESISTANCE ( $R_{\theta}$  JA) OF "L" PACKAGE versus AIR VELOCITY

As with the previous examples, the dc power at 50% duty cycle is subtracted from the maximum allowable device dissipation (PD) to obtain a maximum  $P_{ac}$ . The safe operating area under Curve D of Figure 18 can now be generated from Figure 15 and equation (5).

#### Heat Sink and Forced Air Combined:

Some heat sink manufacturers provide data and curves of  $R_{\theta CA}$  for still air and forced air such as illustrated in Figure 22. For example the 6012B heat sink has an  $R_{\theta CA}$  = 17°C/W at 500 LFPM as noted in Figure 22. From equation (6):

Max  $R_{\theta,JA} = 50^{\circ}\text{C/W} + 17^{\circ}\text{C/W} = 67^{\circ}\text{C/W}$ From equation (3) at  $T_A = +70^{\circ}\text{C}$

$$P_D = \frac{175^{\circ}C - 70^{\circ}C}{67^{\circ}C/W}$$

1.57 watts.

FIGURE 22 – THERMAL RESISTANCE  $R_{\theta CA}$  versus AIR VELOCITY

As before this yields a safe operating area under Curve E in Figure 18.

Note from Table 1 and Figure 21 that if the 14-pin ceramic package is mounted directly to the PC board (2 oz. cu. underneath), that typical  $R_{\theta} \, \text{JA}$  is considerably less than for socket mount with still air and no heat sink. The following procedure can be employed to determine a safe operating area for this condition.

Given data from Table 1:

typical

$$R_{\theta JA} = 100^{\circ} C/W$$

typical  $R_{\theta JC} = 27^{\circ} C/W$

From Curve 2 of Figure 21,  $R_{\theta JA}(typ)$  is  $75^{\circ}C/W$  for a PC mount and no air flow. Then the typical  $R_{\theta CA}$  is  $75^{\circ}C/W-27^{\circ}C/W=48^{\circ}C/W$ . From Table 1 the typical value of  $R_{\theta CA}$  for socket mount is  $100^{\circ}C/W-27^{\circ}C/W=73^{\circ}C/W$ . This shows that the PC board mount results in a decrease in typical  $R_{\theta CA}$  by a ratio of 1:1.5 below the typical value of  $R_{\theta CA}$  in a socket mount. Therefore, the maximum value of socket mount  $R_{\theta CA}$  of  $100^{\circ}C/W$  should also decrease by a ratio of 1:1.5 when the device is mounted in a PC board. The maximum  $R_{\theta CA}$  becomes:

$$R_{\theta CA} = \frac{100^{\circ}C/W}{1.5} = 66^{\circ}C/W \text{ for PC board mount}$$

Therefore the maximum  $R_{\theta JA}$  for a PC mount is from equation (6).

$$R_{\theta}JA = 50^{\circ}C/W + 66^{\circ}C/W = 116^{\circ}C/W$$

.

With maximum  $R_{\theta,JA}$  known, the maximum power dissipation can be found and the safe operating area determined as before. See Curve B in Figure 18.

#### CONCLUSION

In most cases, heat sink manufacturer's publish only RACA socket mount data. Although RACA data for PC mounting is generally not available, this should present no problem. Note in Figure 21 that an air flow greater than 250 LFPM yields a socket mount Raid approximately 6% greater than for a PC mount. Therefore, the socket mount data can be used for a PC mount with a slightly greater safety factor. Also it should be noted that thermal resistance measurements can vary widely. These measurement variations are due to the dependency of RACA on the type environment and measurement techniques employed. For example, ROCA would be greater for an integrated circuit mounted on a PC board with little or no ground plane versus one with a substantial ground plane. Therefore, if the maximum calculated junction temperature is on the border line of being too high for a given system application, then thermal resistance measurements should be done on the system to be absolutely certain that the maximum junction temperature is not exceeded

## TYPICAL APPLICATIONS

FIGURE 23 - AC-COUPLED MOS CLOCK DRIVER

FIGURE 24 - DC-COUPLED RAM MEMORY ADDRESS

OR PRECHARGE DRIVER (POSITIVE-SUPPLY ONLY)