# International **TGR** Rectifier

# **Designer's Manual**

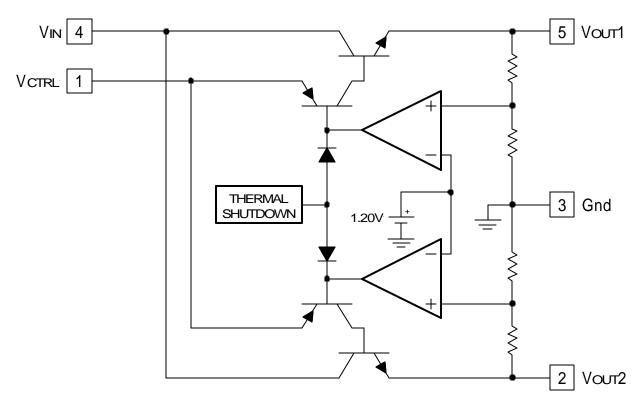

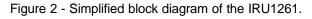

The information presented in this DC-DC Power Management IC Databook Designer's Manual is believed to be accurate and reliable. However, International Rectifier can assume no responsibility for its use nor any infringement of patents or other rights of third parties which may result from its use.

No license is granted by implication or other use under any patent or patent rights of International Rectifier. No patient liability shall be incurred for the circuits or devices described herein. International Rectifier does not recommend the use of its devices in life support applications wherein such use may directly threaten life or injury due to device failure or malfunction. Users of International Rectifier devices in life support applications assume all risks of such use and indemnify International Rectifier against all damages resulting from such use.

The data presented in this manual supersedes all previous specifications. In the interest of product improvement, International Rectifier reserves the right to change specifications without notice.

PUBLISHED BY INTERNATIONAL RECTIFIER, 233 KANSAS ST., EL SEGUNDO, CALI-FORNIA 90245

All rights reserved. Reproduction or use of editorial or pictorial content without express permission in writing is prohibited. Printed 10/2002

- **Section 1: General Information**

- **Section 2: Linear Regulators**

- Section 3: Dual Low Dropout Regulators

- Section 4: Switching Regulator Controllers

- **Section 5: Package Information**

- **Section 6: Contact Information**

## **Section 1: General Information**

| Introduction                    |

|---------------------------------|

| Part Identification             |

| Quality and Reliability Program |

| Cross Reference Guide           |

# Introduction The Power Conversion Process

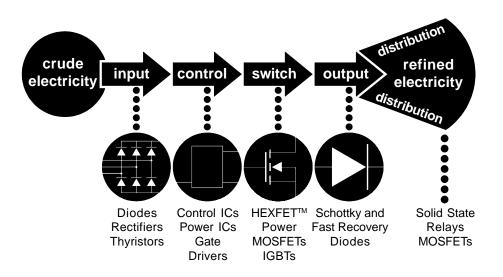

At International Rectifier, we've spent the last 55 years dedicated to improving the conversion of electricity from its crude form to its refined form. The Power Conversion Process takes crude energy in an inconvenient format and refines it to exactly what the load requires. International Rectifier is dedicated to this process. We picture it as a four-stage process, with an additional stage for distribution.

The information provided by International Rectifier in this publication is believed to be accurate and reliable. However, no responsibility is assumed by International Rectifier for its use, nor any infringements of patents or other rights of third parties resulting from its use. No license is granted by implication or other use under any patent or patent rights of International Rectifier. No patent liability shall be incurred for the circuits or devices described herein. International Rectifier reserves the right to change the circuitry and specifications at any time without prior notice.

#### Life Support Applications Policy

International Rectifier does not recommend the use of its devices in life support applications wherein such use may directly threaten life or injury due to device failure or malfunction. Users of International Rectifier devices in life support applications assume all risks of such use and indemnify International Rectifier against all damages resulting from such use.

Copyright 2002, International Rectifier Corporation, El Segundo, CA USA. All rights reserved. Reproduction or use without expressed permission in writing is prohibited.

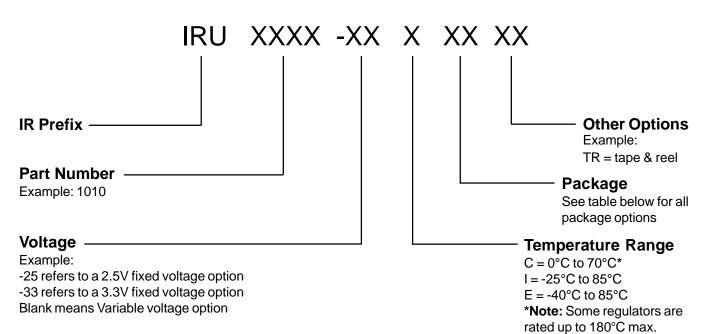

# **Part Identification**

### **Package Offering**

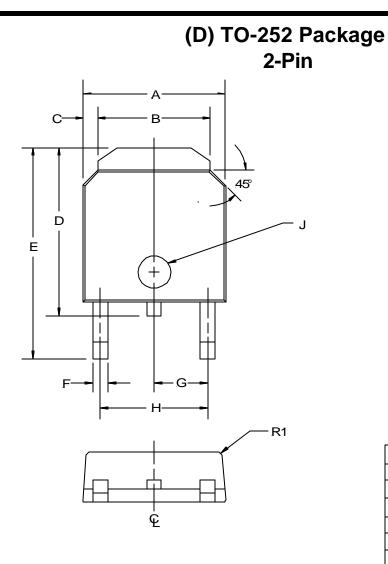

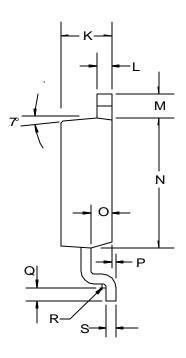

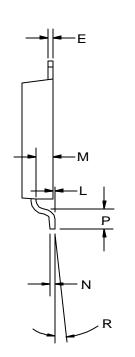

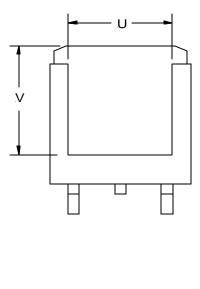

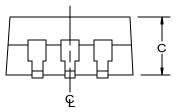

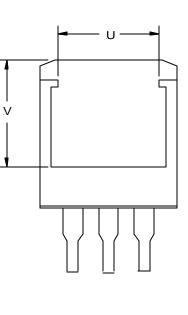

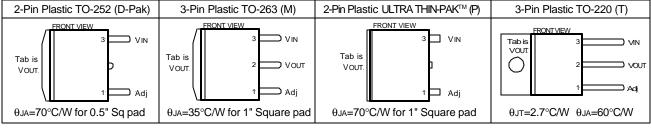

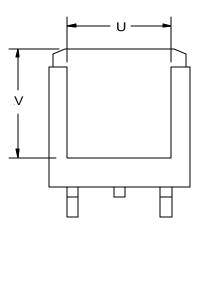

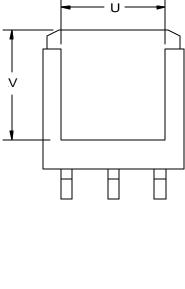

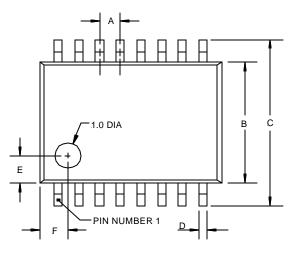

| PACKAGE<br>DESCRIPTION                        | PACKAGE<br>DESIG |

|-----------------------------------------------|------------------|

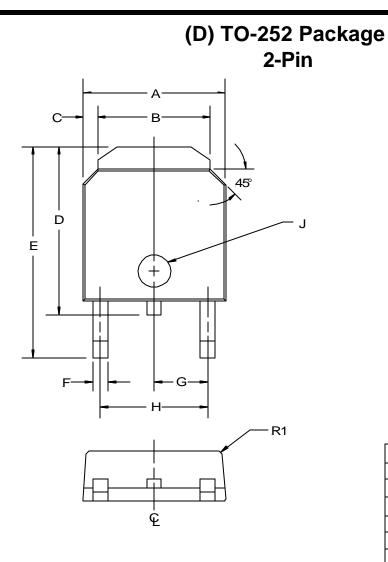

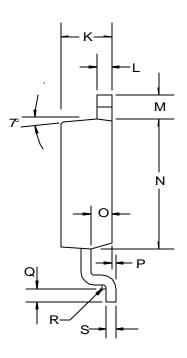

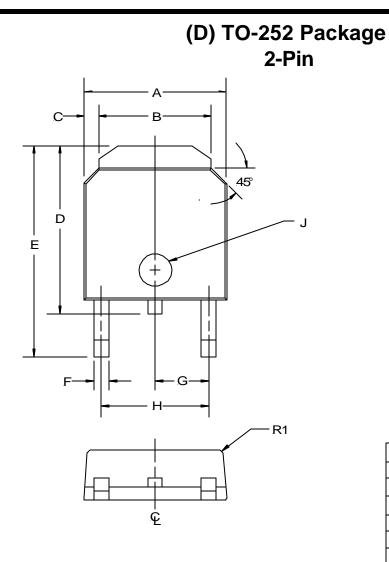

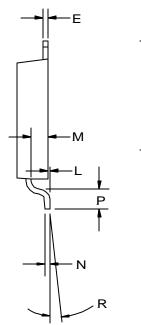

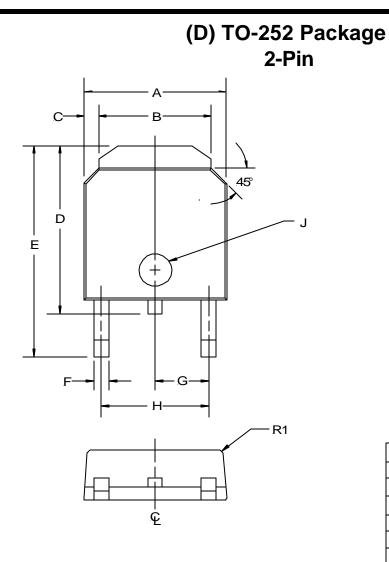

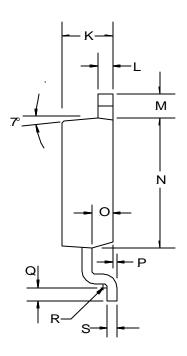

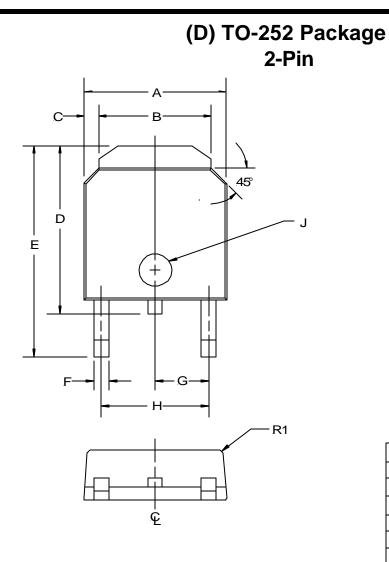

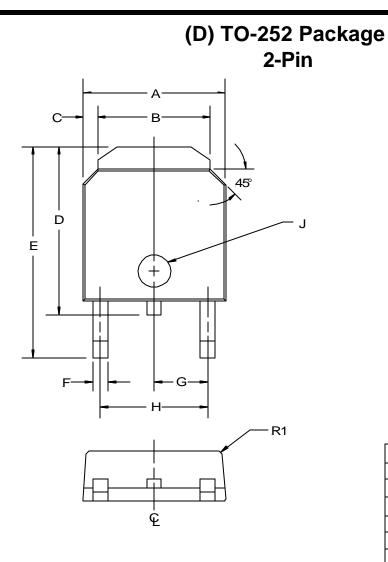

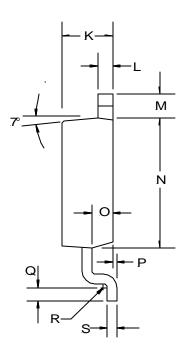

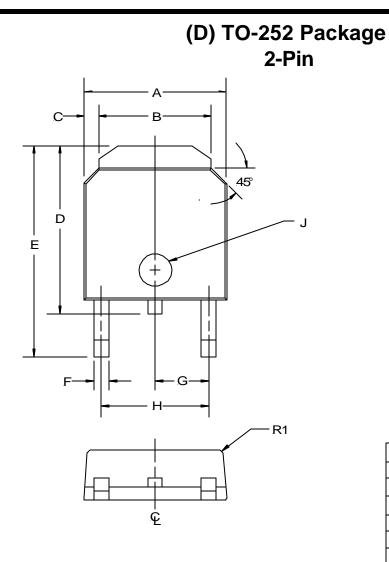

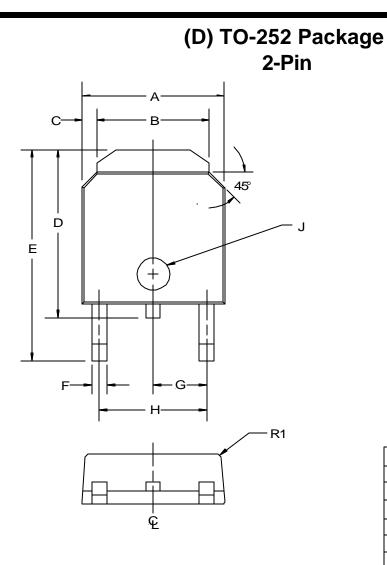

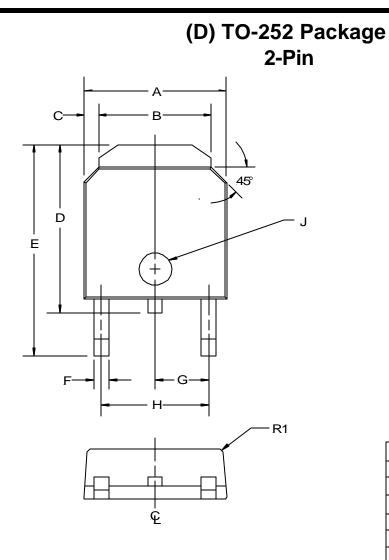

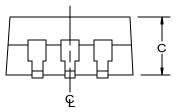

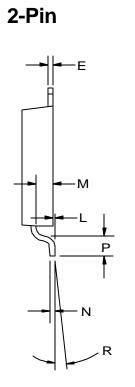

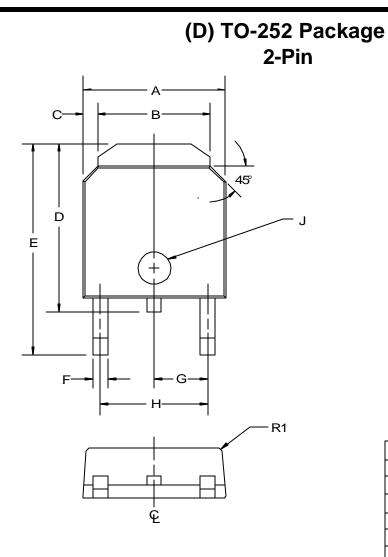

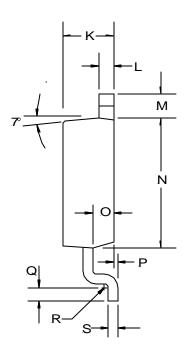

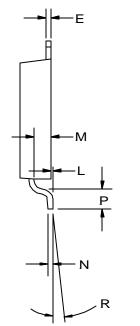

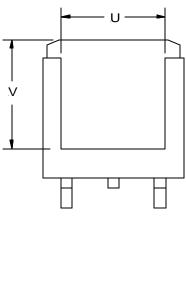

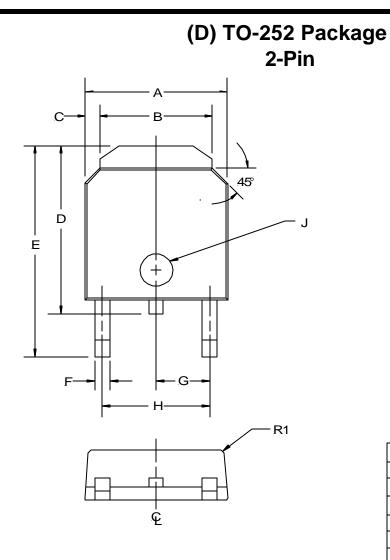

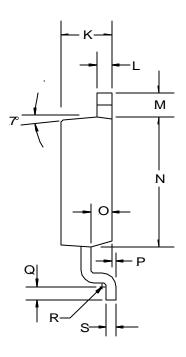

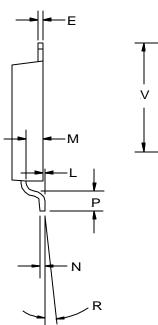

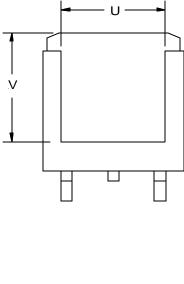

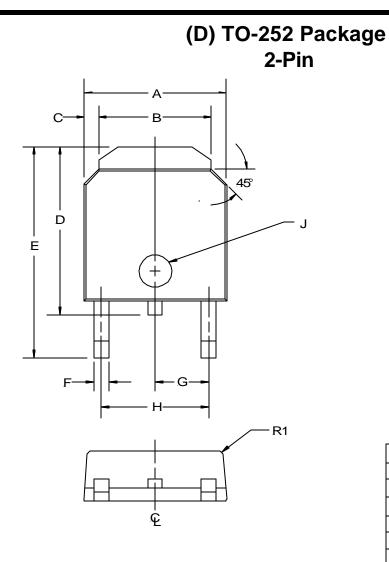

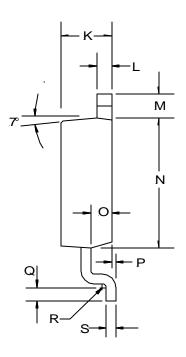

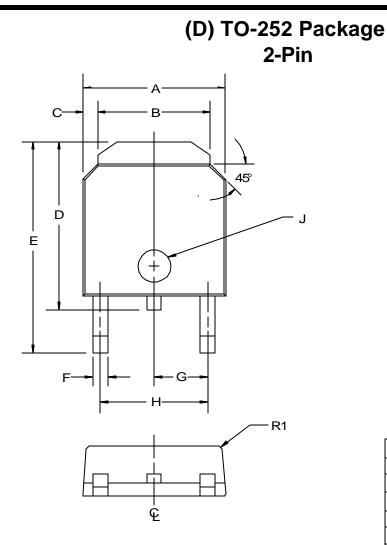

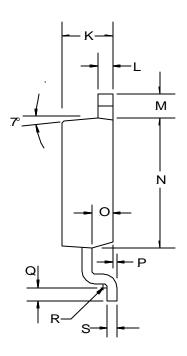

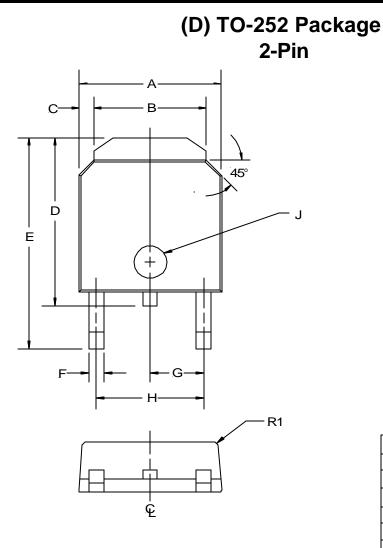

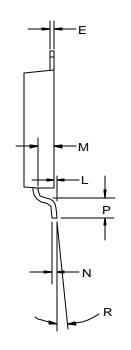

| TO-252 D-Pak 2-Pin                            | D                |

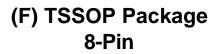

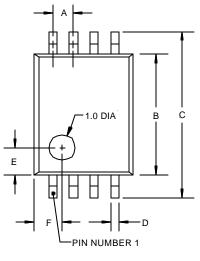

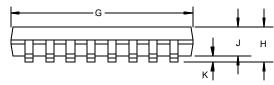

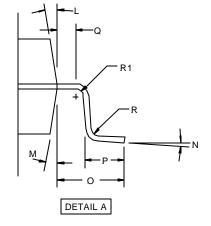

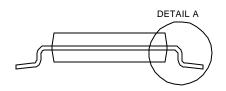

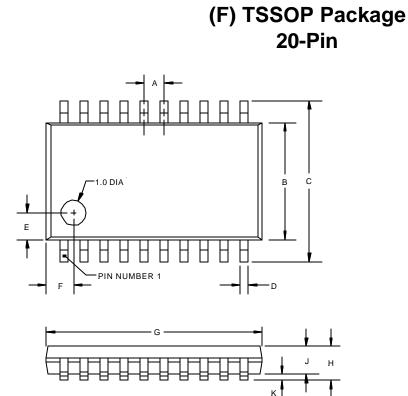

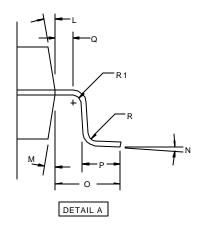

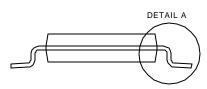

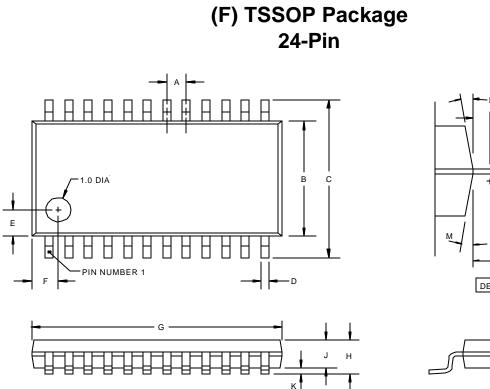

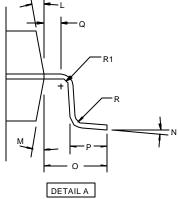

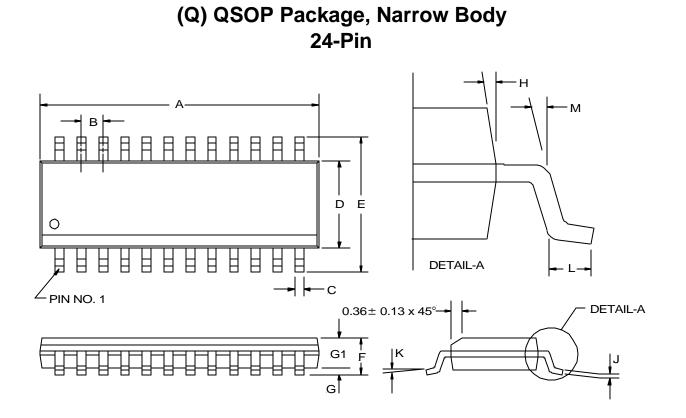

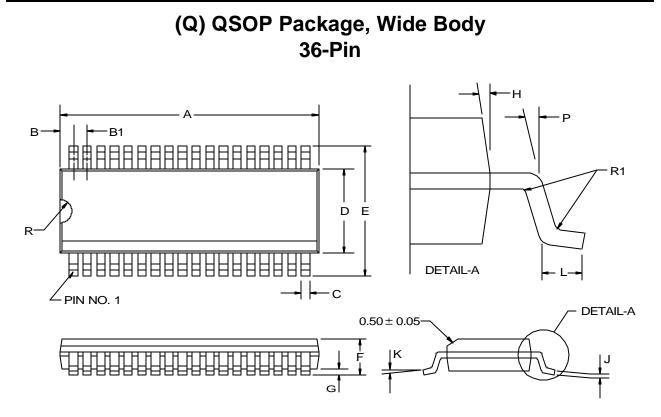

| TSSOP 8, 14, 16, 20 and 24-Pin                | F                |

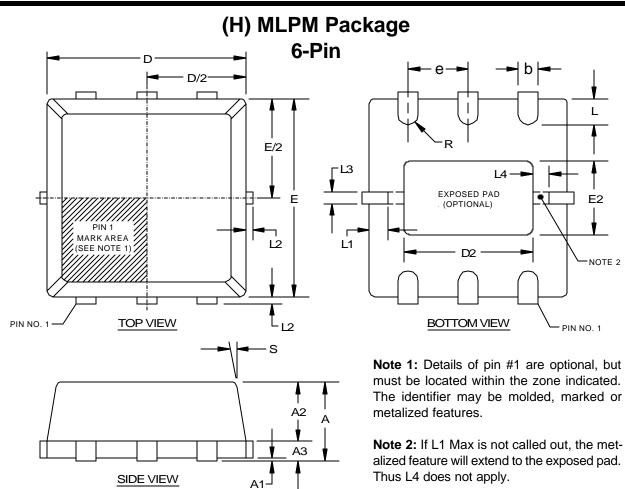

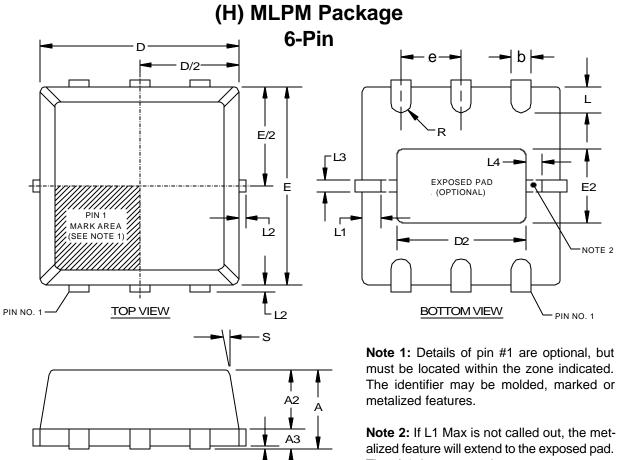

| MLPM 3x3 6-Pin                                | Н                |

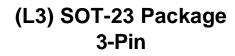

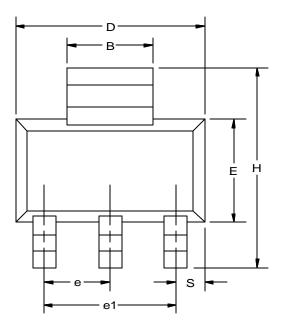

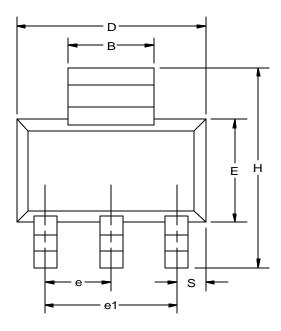

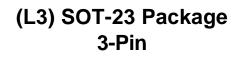

| SOT-23 3-Pin                                  | L3               |

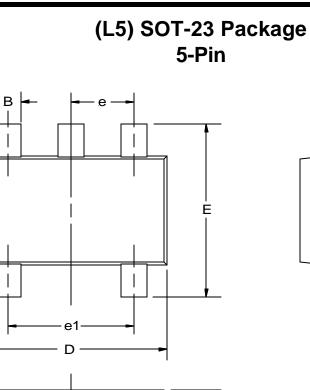

| SOT-23 5-Pin                                  | L5               |

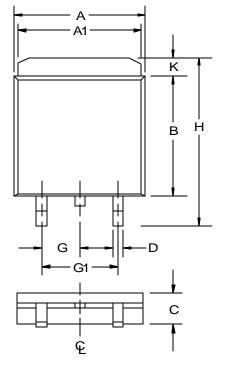

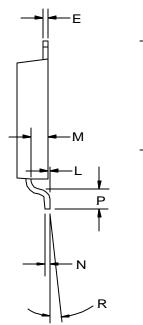

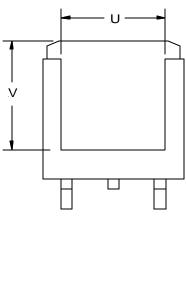

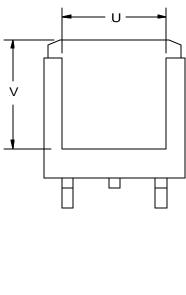

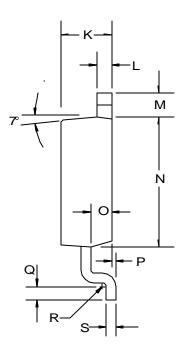

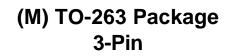

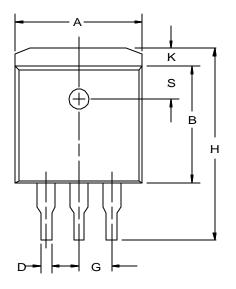

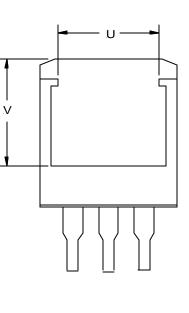

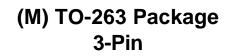

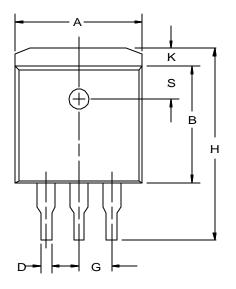

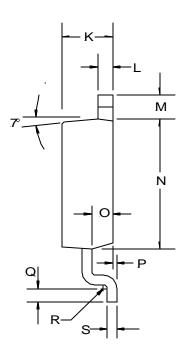

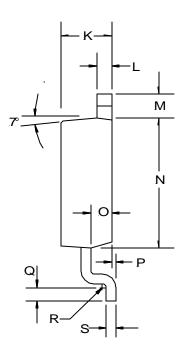

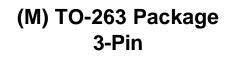

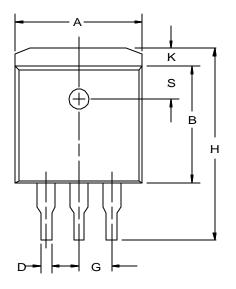

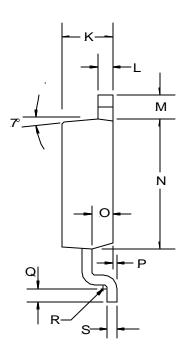

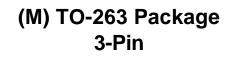

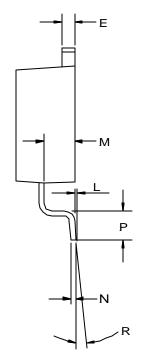

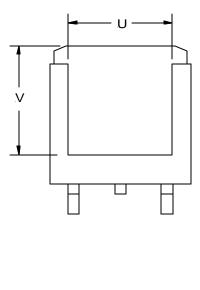

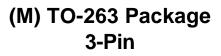

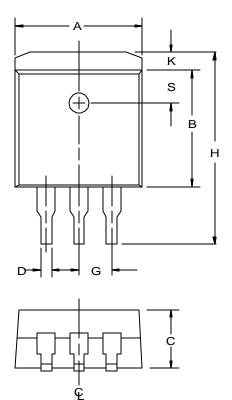

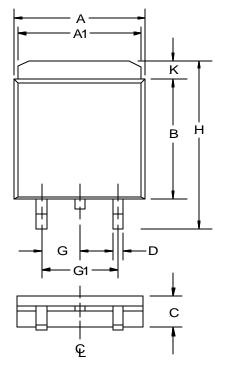

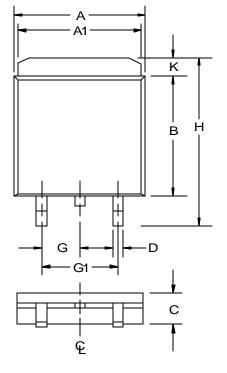

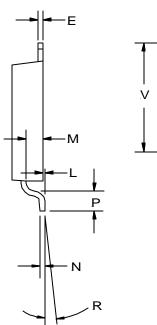

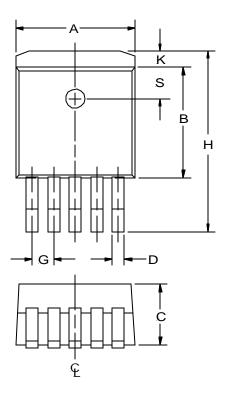

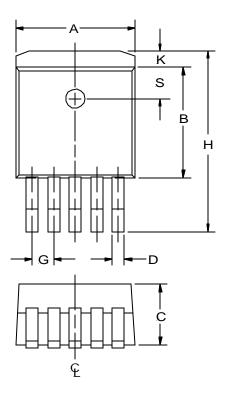

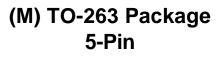

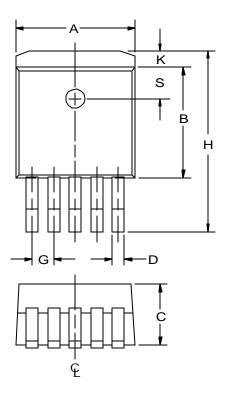

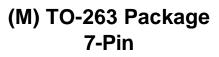

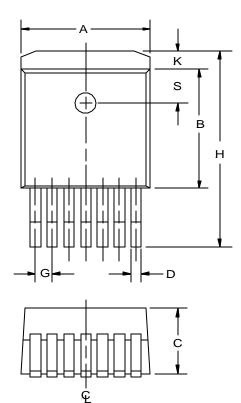

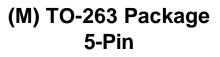

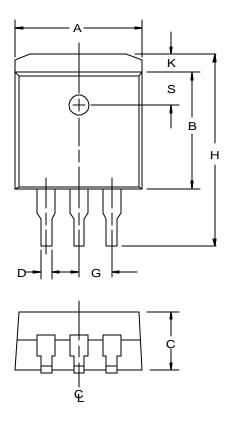

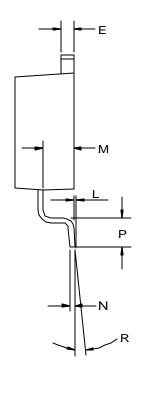

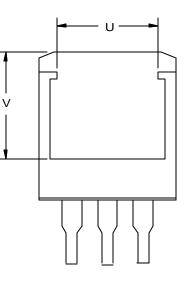

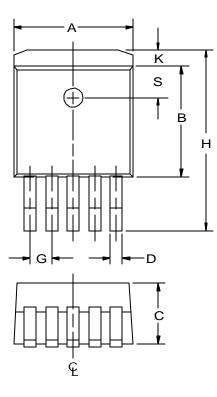

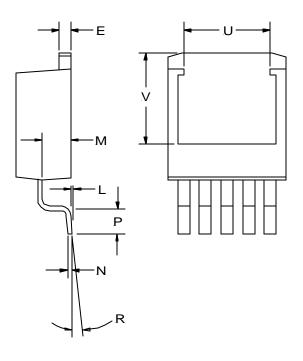

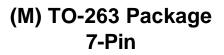

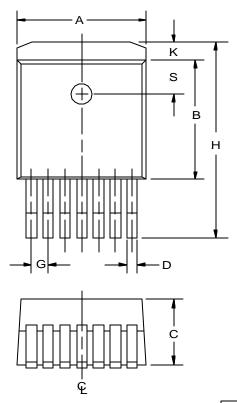

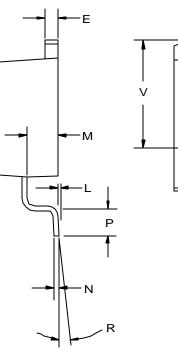

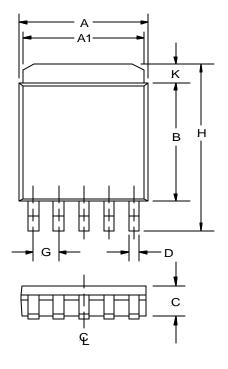

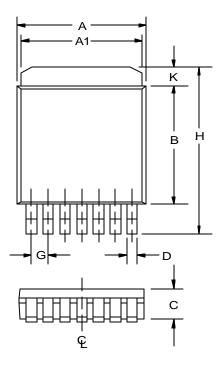

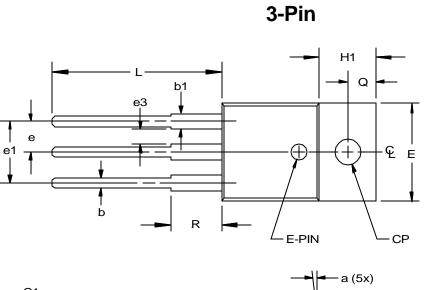

| TO-263 3, 5 and 7-Pin                         | М                |

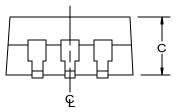

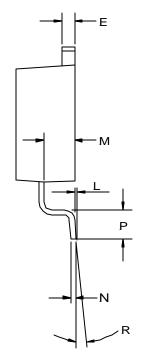

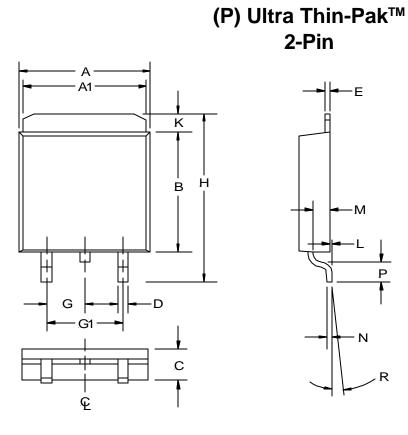

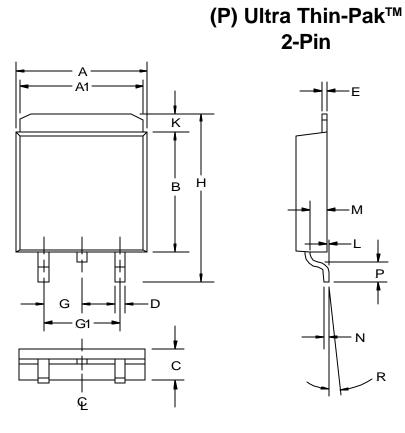

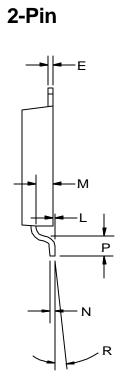

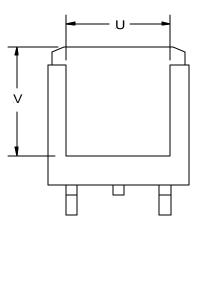

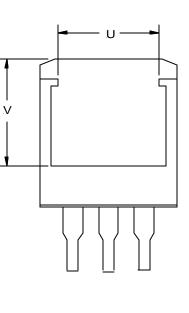

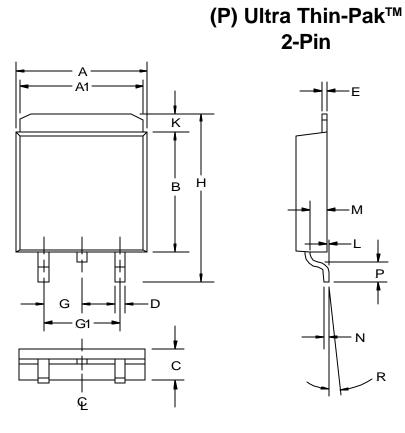

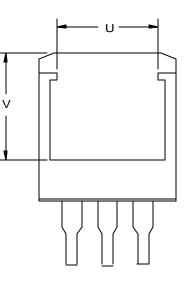

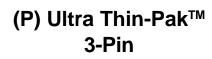

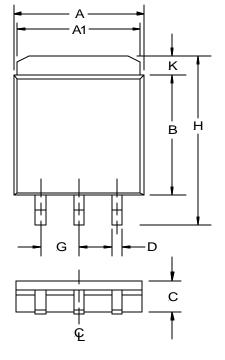

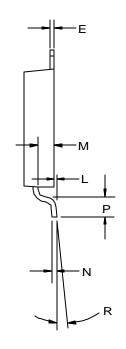

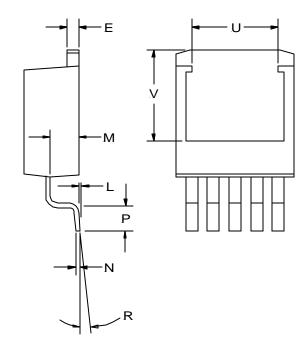

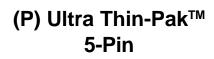

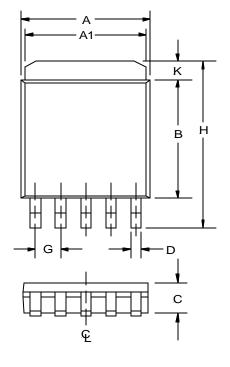

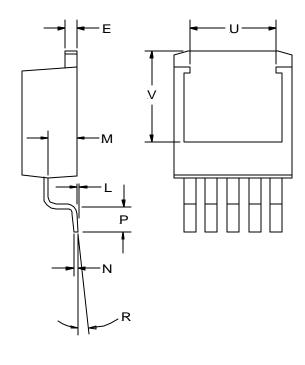

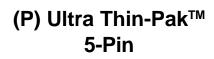

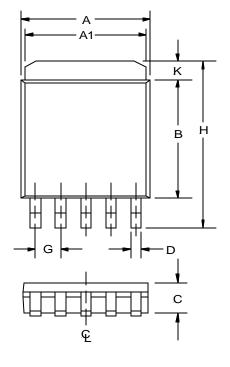

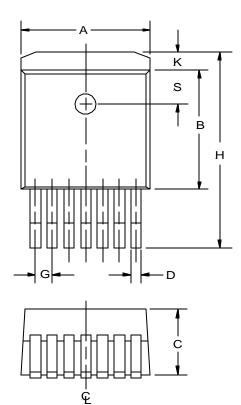

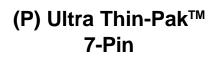

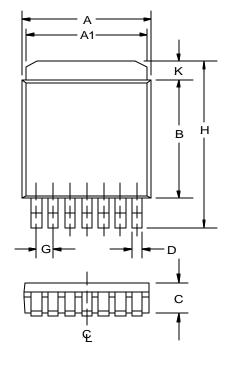

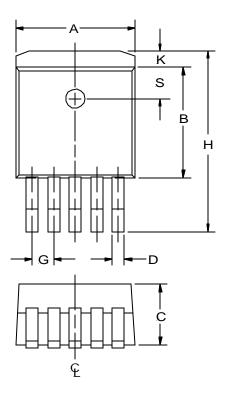

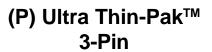

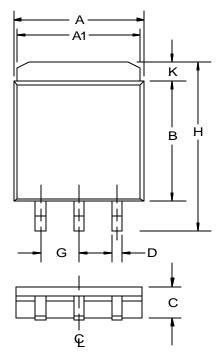

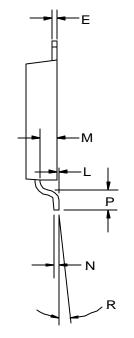

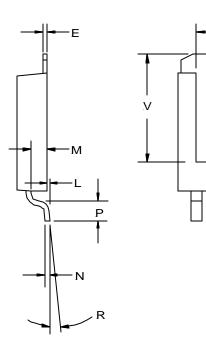

| Ultra Thin-Pak <sup>™</sup> 2, 3, 5 and 7-Pin | Р                |

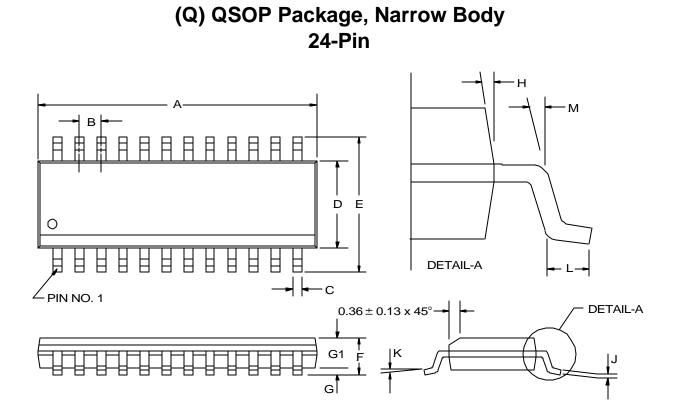

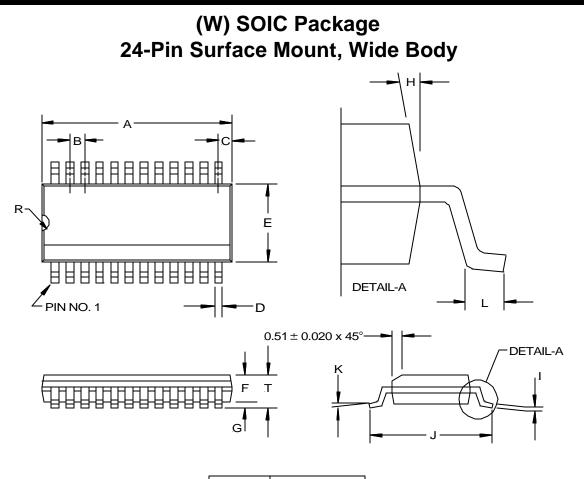

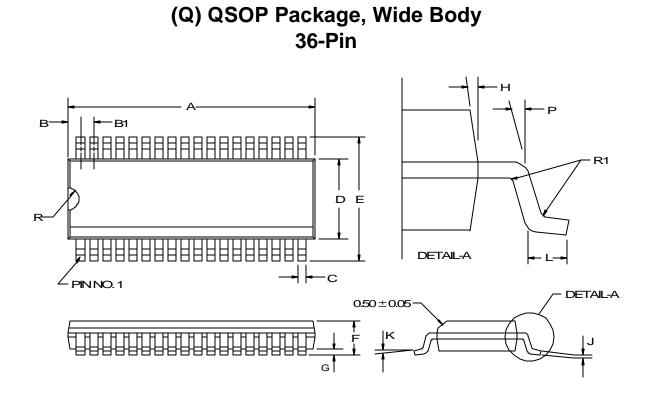

| QSOP Narrow Body 24-Pin                       | Q                |

| QSOP Wide Body 36-Pin                         | Q                |

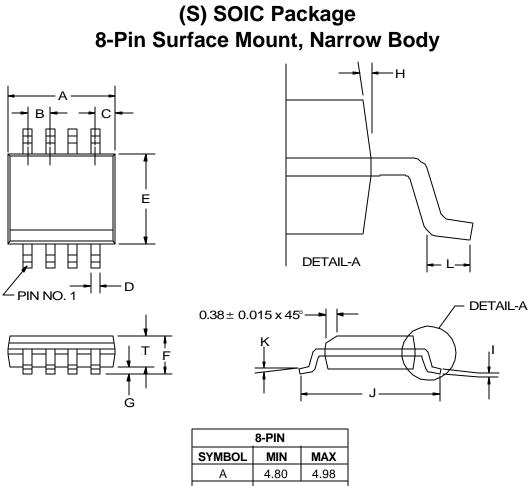

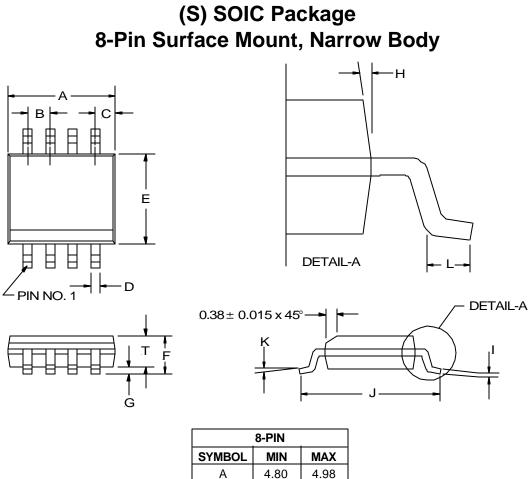

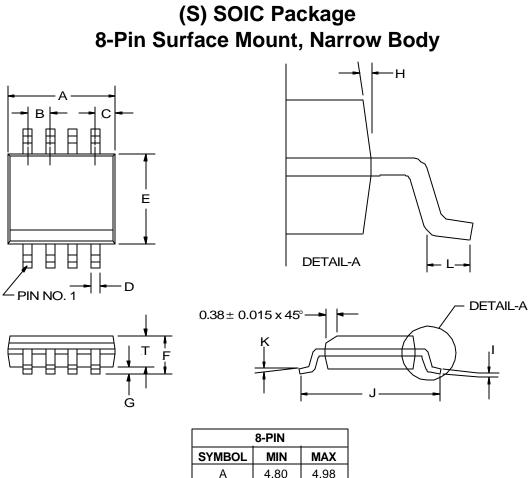

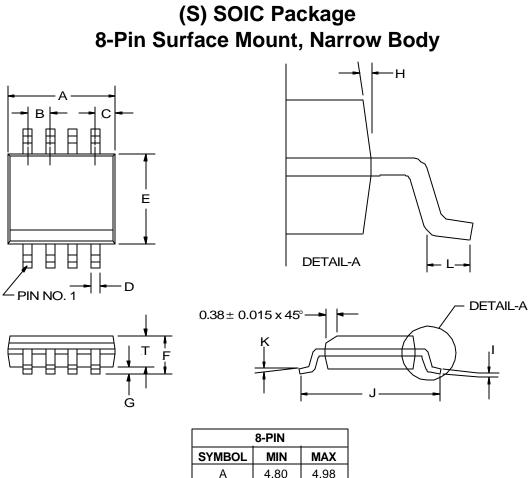

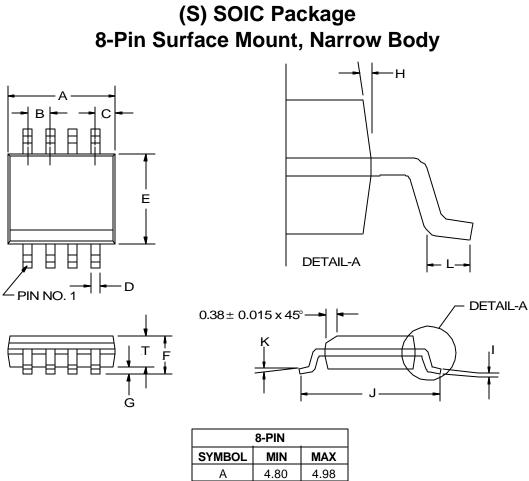

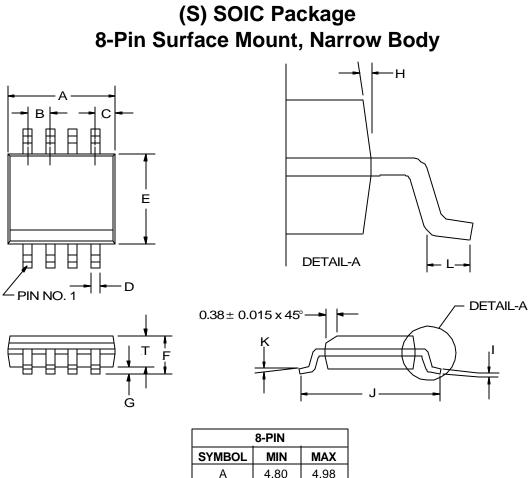

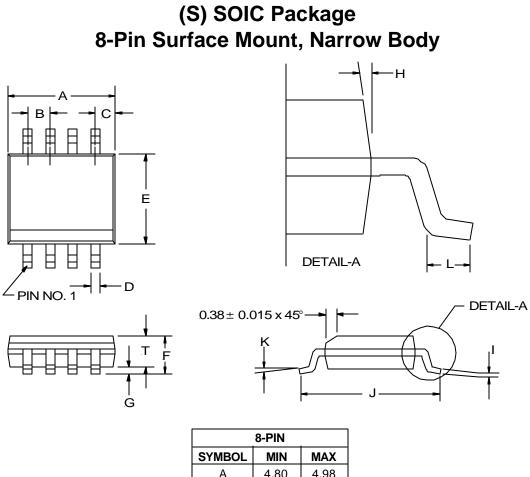

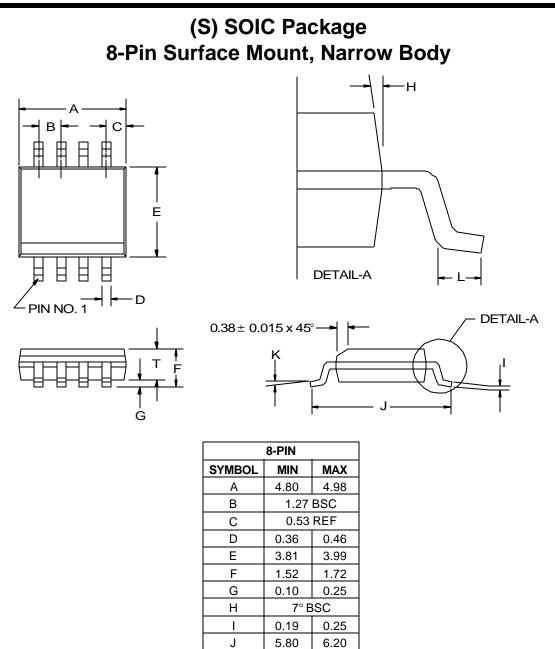

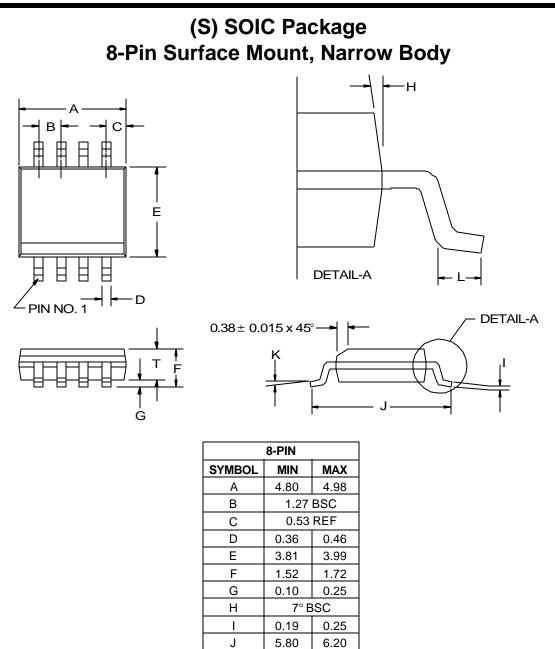

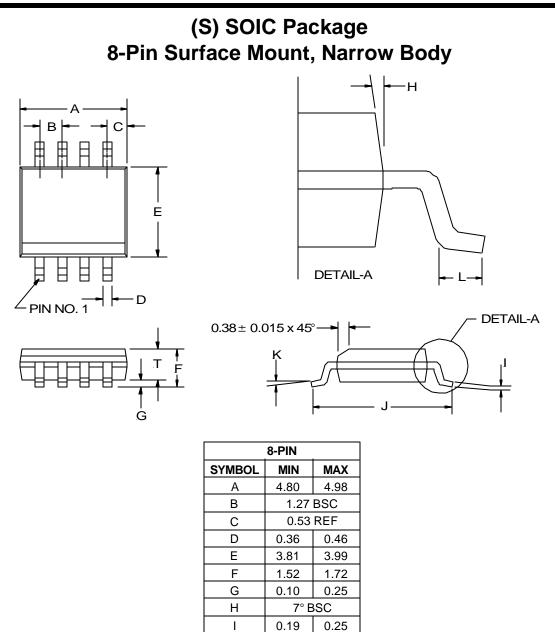

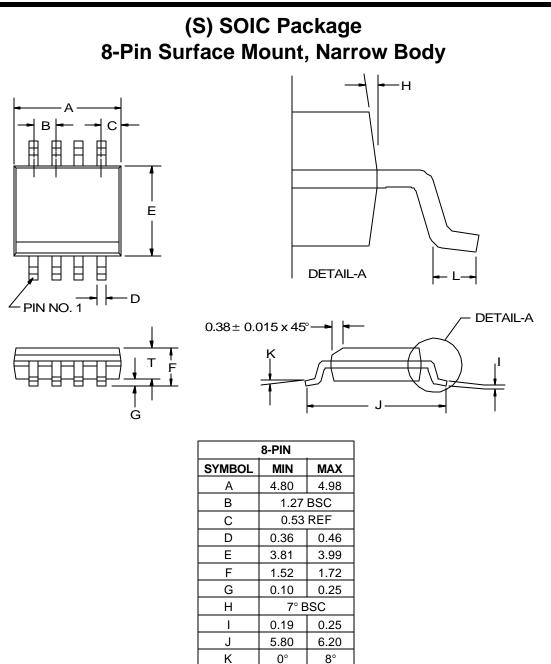

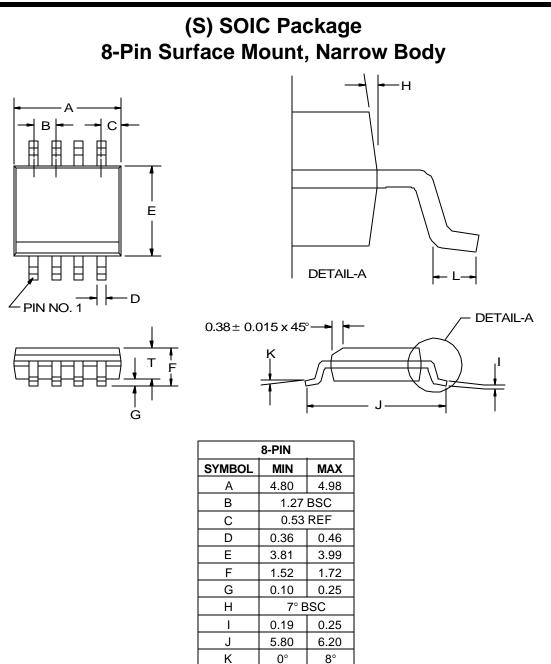

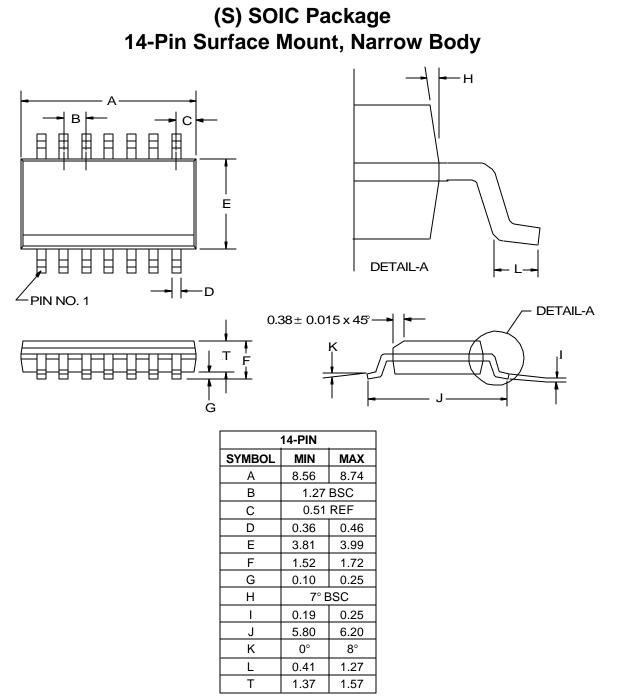

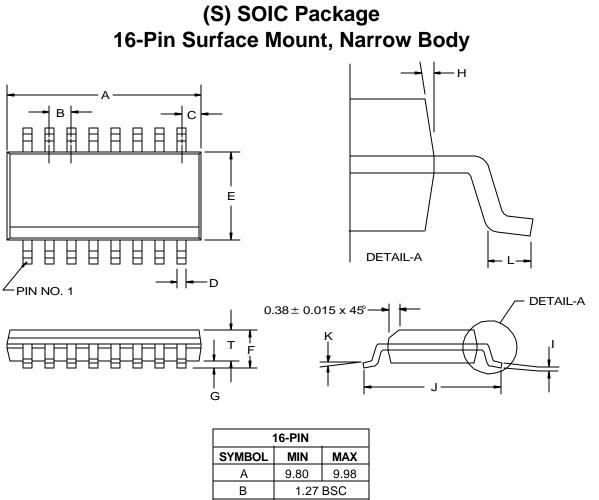

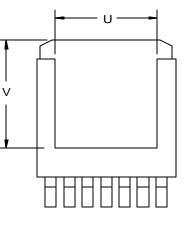

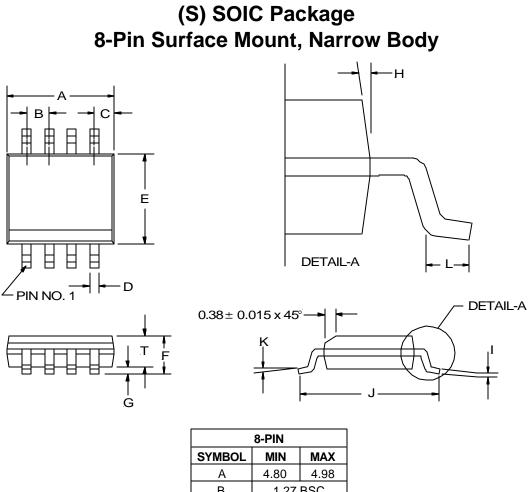

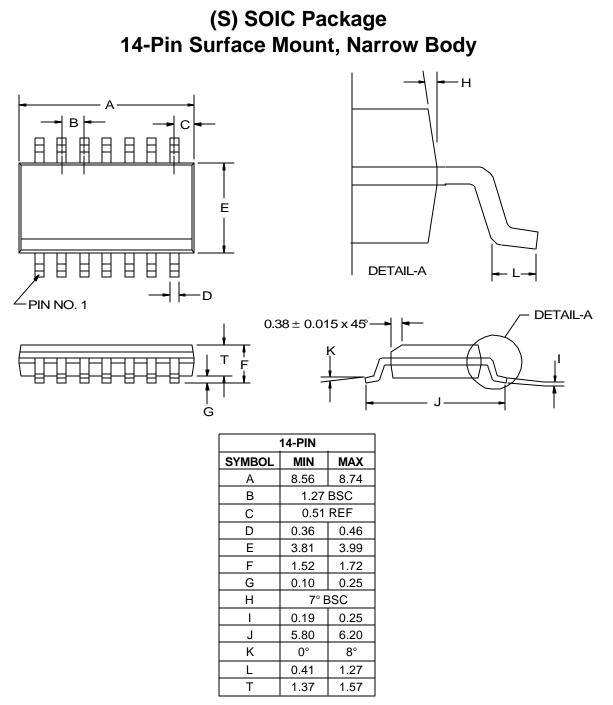

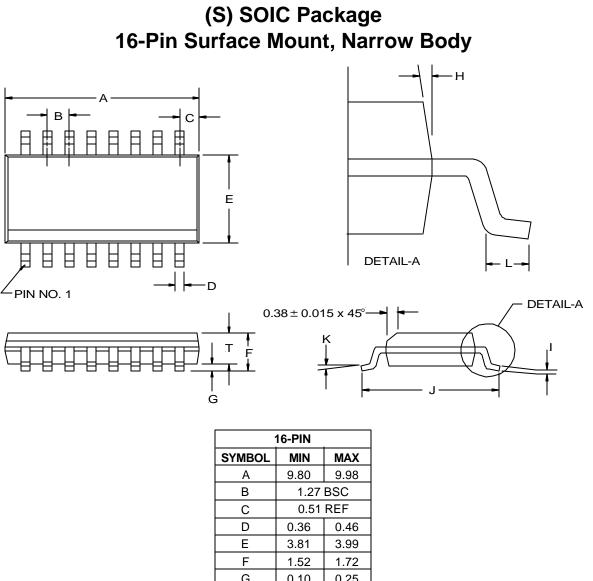

| SOIC Narrow Body 8, 14 and 16-Pin             | S                |

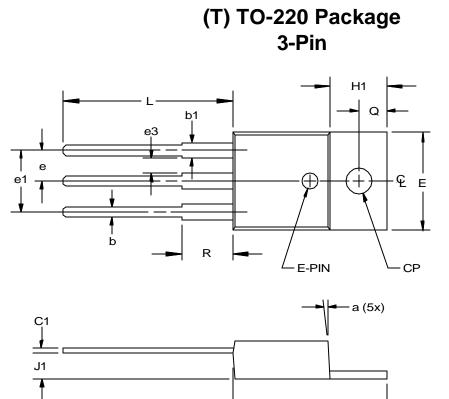

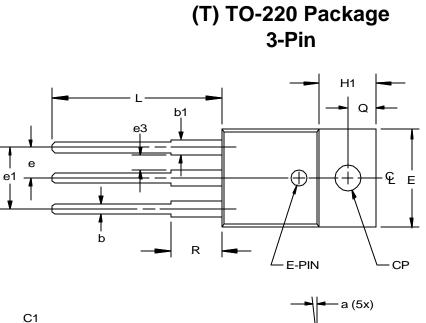

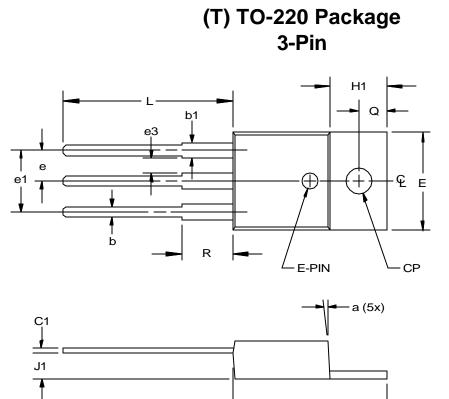

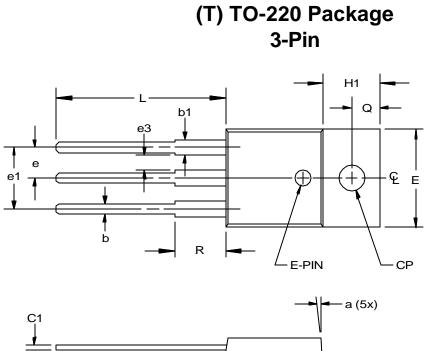

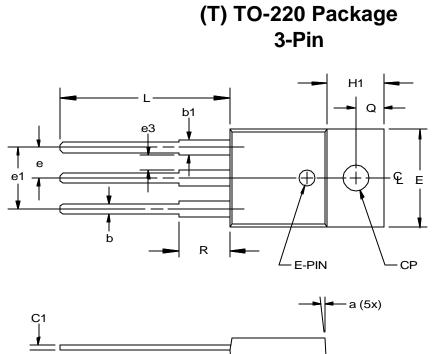

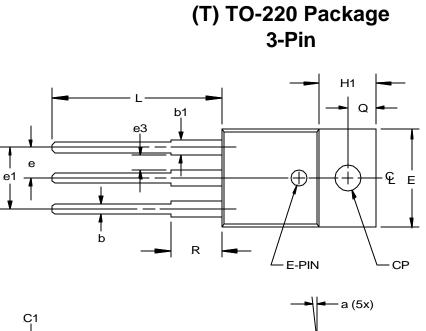

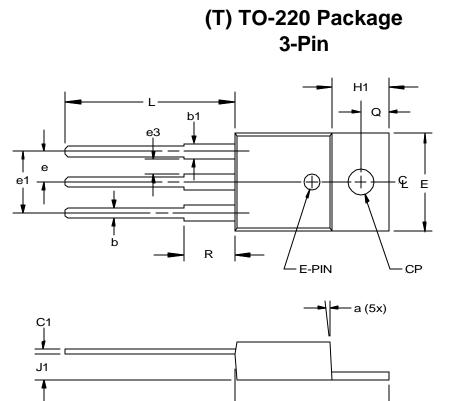

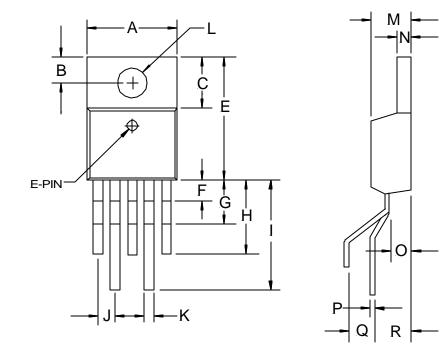

| TO-220 3, 5 and 7-Pin                         | Т                |

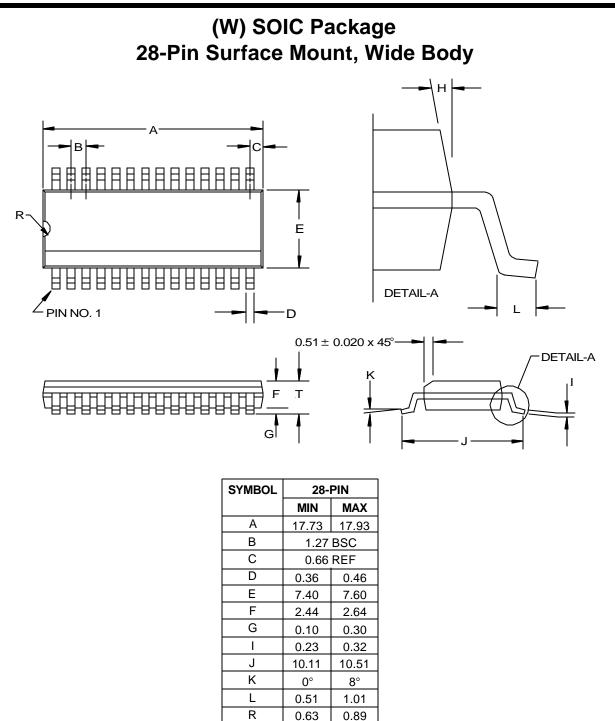

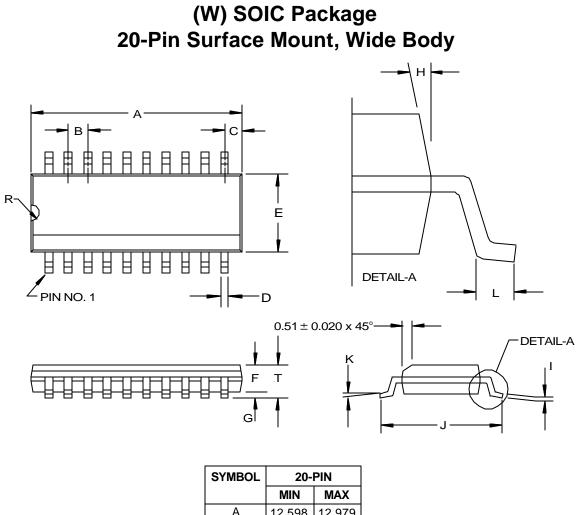

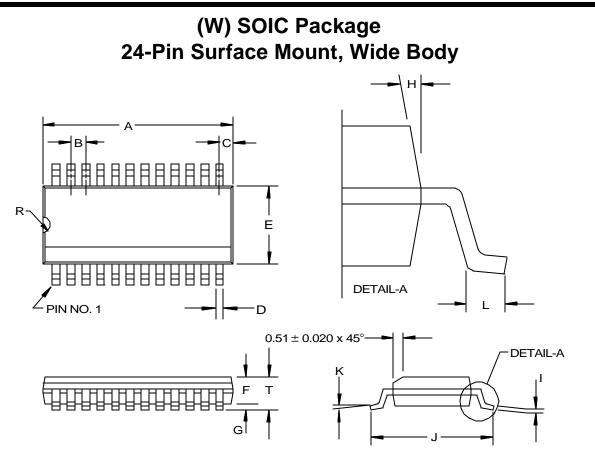

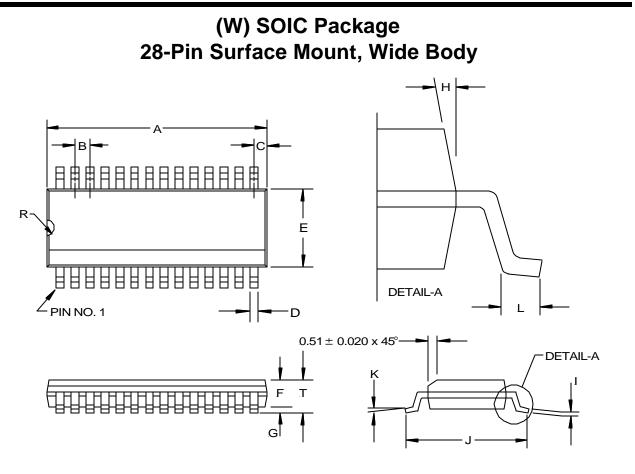

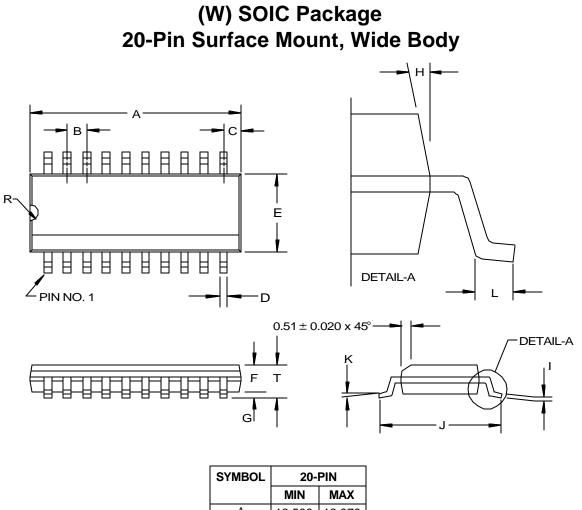

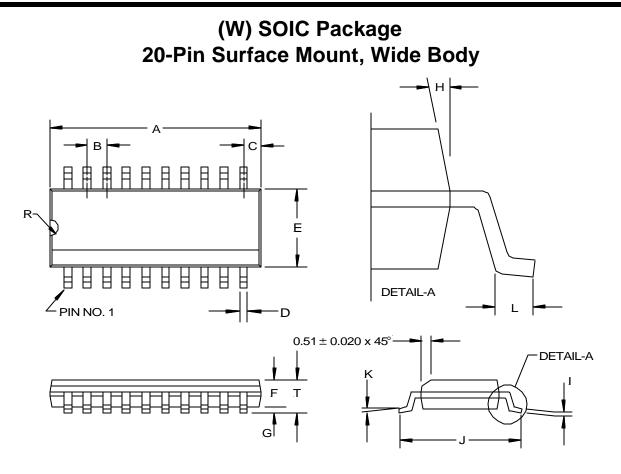

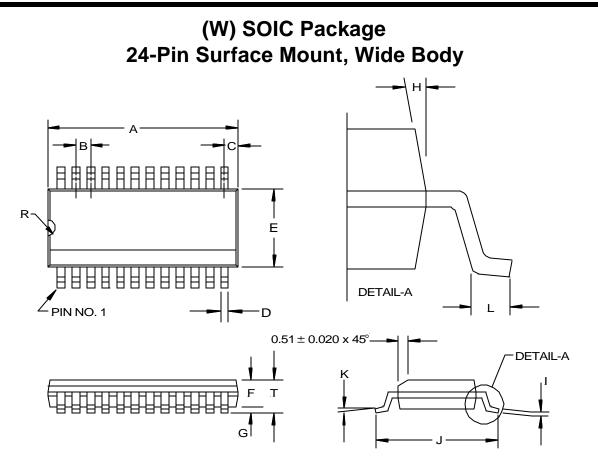

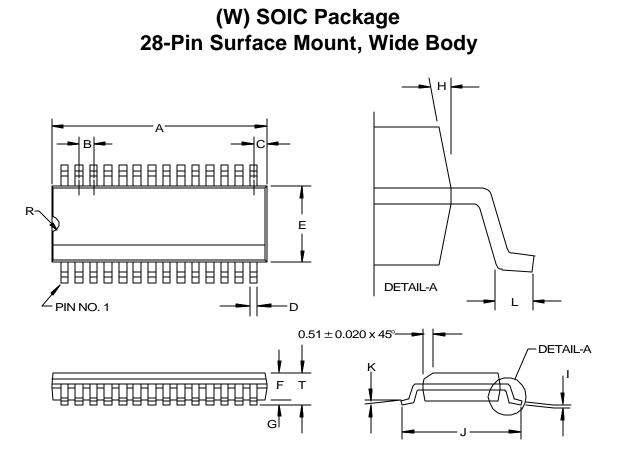

| SOIC Wide Body 20, 24 and 28-Pin              | W                |

| SOT-223 3-Pin                                 | Y                |

# **Quality / Reliability Program**

#### Qualification:

A minimum qualification testing is required to be performed on all new products/processes or any major process changes in the production line. A major change in the process will include an additional construction analysis. All samples will be collected from five different lots. Table I describes these requirements:

| TABLE I             |                                                                                                                                 |                         |                            |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--|--|--|--|--|--|--|

| Test Description    | Test Condition                                                                                                                  | Test Duration           | Sample Size/<br>Acceptance |  |  |  |  |  |  |  |

| Operating Life Test | T <sub>A</sub> = 125°C<br>T <sub>A</sub> = 150°C                                                                                | 1000 Hours<br>191 Hours | 77 / 0<br>77 / 0           |  |  |  |  |  |  |  |

| Autoclave           | T <sub>A</sub> = 121°C, 15 psi, 100% RH                                                                                         | 168 Hours               | 45 / 0                     |  |  |  |  |  |  |  |

| Temperature Cycle   | Air to Air, -65°C to +150°C                                                                                                     | 100 Cycles              | 45 / 0                     |  |  |  |  |  |  |  |

| Thermal Shock       | Liquid to Liquid, -55°C to +125°C                                                                                               | 100 Cycles              | 45 / 0                     |  |  |  |  |  |  |  |

| Power Cycle         | Power cycle "ON" and "OFF" at<br>maximum rated current as<br>required to keep the case<br>temperature between 40°C<br>and 125°C | 10,000 cycles           | 45 / 0                     |  |  |  |  |  |  |  |

| Highly Accelerated  | T <sub>A</sub> = + 85°C, RH = 85%, Biased                                                                                       | 1000 Hours              | 45 / 0                     |  |  |  |  |  |  |  |

| Stress Test (HAST)  | T <sub>A</sub> = +130°C, RH = 85%, Biased                                                                                       | 100 Hours               | 45 / 0                     |  |  |  |  |  |  |  |

#### On-Going Reliability Program

An on-going reliability program has been implemented to ensure continuous shipment of quality parts. On a regular basis, a minimum sample of parts according to their package outline and functionality will be selected and be introduced to certain testing procedures as described in Table II.

| Test Description                         | Test Condition                            | Test Duration | Sample Size/<br>Acceptance |  |  |  |  |

|------------------------------------------|-------------------------------------------|---------------|----------------------------|--|--|--|--|

| Operating Life Test                      | T <sub>A</sub> = 125°C                    | 168 Hours     | 77 / 0                     |  |  |  |  |

| Autoclave                                | T <sub>A</sub> = 121°C, 15 psi, 100% RH   | 96 Hours      | 45 / 0                     |  |  |  |  |

| Temperature Cycle                        | Air to Air, -65°C to +150°C               | 100 Cycles    | 45 / 0                     |  |  |  |  |

| Thermal Shock                            | Liquid to Liquid, -55°C to +125°C         | 100 Cycles    | 45 / 0                     |  |  |  |  |

| Highly Accelerated<br>Stress Test (HAST) | T <sub>A</sub> = +130°C, RH = 85%, Biased | 100 Hours     | 45/0                       |  |  |  |  |

TABLE II

#### On-Going Production Program

As part of our on going quality program, a minimum sample of 500 pieces from every production lot will be burned in a minimum of 168 hours at 125°C. All the data will be collected and every single rejected unit will be evaluated. This analysis will be done for a minimum of five production lots.

Also, as part of this program, all production parts will be tested for all extreme temperature requirements. The yield analysis from every lot at these extreme temperatures will enable us to optimize our probe programming while screening out marginal devices at these extreme temperatures.

# **Cross Reference by Manufacturer**

#### ALPHA/SIPEX SEMICONDUCTOR

| ALPHA/SIPEA | SEIMICONDUC | IUR                    |

|-------------|-------------|------------------------|

| Part #      | IR Cross    | Comments               |

| AS1115      | IRU1010     | Better Dropout Voltage |

| AS1115-18   | IRU1010-18  | Better Dropout Voltage |

| AS1115-25   | IRU1010-25  | Better Dropout Voltage |

| AS1115-33   | IRU1010-33  | Better Dropout Voltage |

| AS1117      | IRU1117     | Better Dropout Voltage |

| AS1117-18   | IRU1117-18  | Better Dropout Voltage |

| AS1117-25   | IRU1117-25  | Better Dropout Voltage |

| AS1117-33   | IRU1117-33  | Better Dropout Voltage |

| AS1580      | IRU1175     | Better Dropout Voltage |

| AS1581      | IRU1160     | Better Dropout Voltage |

| AS1582      | IRU1150     | Better Dropout Voltage |

| AS2810      | IRU1010     |                        |

| AS2810-18   | IRU1010-18  |                        |

| AS2810-25   | IRU1010-25  |                        |

| AS2810-33   | IRU1010-33  |                        |

| AS2815      | IRU1015     |                        |

| AS2830      | IRU1030     | Better Dropout Voltage |

| AS2830-33   | IRU1030-33  | Better Dropout Voltage |

| AS2840      | IRU1050     | Better Dropout Voltage |

| AS2840-33   | IRU1050-33  | Better Dropout Voltage |

| AS2850      | IRU1050     | Better Dropout Voltage |

| AS2850-33   | IRU1050-33  | Better Dropout Voltage |

| AS2870      | IRU1075     | Better Dropout Voltage |

| AS2884      | IRU1075     |                        |

| AS2885      | IRU1050     |                        |

| AS2885-33   | IRU1050-33  | Better Dropout Voltage |

| AS2887      | IRU1030     | Better Dropout Voltage |

| AS2887-33   | IRU1030-33  | Better Dropout Voltage |

|             |             |                        |

#### ADVANCED MONOLITHIC SYSTEMS (AMS)

| Part #     | IR Cross   | Comments               |

|------------|------------|------------------------|

| AMS1083    | IRU1075    | Better Dropout Voltage |

| AMS1084    | IRU1050    | Better Dropout Voltage |

| AMS1084-33 | IRU1050-33 | Better Dropout Voltage |

| AMS1085    | IRU1030    | Better Dropout Voltage |

| AMS1085-33 | IRU1030-33 | Better Dropout Voltage |

| AMS1086    | IRU1015    | Better Dropout Voltage |

| AMS1086-33 | IRU1015-33 | Better Dropout Voltage |

| AMS1117    | IRU1117    | Better Dropout Voltage |

| AMS1117-18 | IRU1117-18 | Better Dropout Voltage |

| AMS1117-25 | IRU1117-25 | Better Dropout Voltage |

| AMS1117-33 | IRU1117-33 | Better Dropout Voltage |

| AMS1503    | IRU1150    | Better Dropout Voltage |

| AMS1505    | IRU1160    | Better Dropout Voltage |

| AMS1508    | IRU1175    |                        |

| AMS1585    | IRU1050    |                        |

| AMS1585-33 | IRU1050-33 |                        |

| AMS1587    | IRU1030    | Better Dropout Voltage |

| AMS1587-33 | IRU1030-33 | Better Dropout Voltage |

|        | CHERRY/ON S  | EMICONDUCTO | DR                     |

|--------|--------------|-------------|------------------------|

|        | Part #       | IR Cross    | Comments               |

| е      | CS5201       | IRU1010     |                        |

| е      | CS52015      | IRU1015     | Better Dropout Voltage |

| е      | CS5203       | IRU1030     |                        |

| е      | CS5203-33    | IRU1030-33  |                        |

| е      | CS5203A      | IRU1050     | Better Dropout Voltage |

| е      | CS5203A-33   | IRU1050-33  |                        |

| е      | CS5204       | IRU1050     | Better Dropout Voltage |

| е      | CS5204-33    | IRU1050-33  | Better Dropout Voltage |

| е      | CS5205       | IRU1050     |                        |

| е      | CS5206       | IRU1075     | Better Dropout Voltage |

| е      | CS5207       | IRU1075     |                        |

|        | CS5207A      | IRU1075     |                        |

|        | CS5253       | IRU1150     | Better Dropout Voltage |

|        | CS5257A      | IRU1175     |                        |

|        |              |             |                        |

|        | FAIRCHILD    |             |                        |

| е      | Part #       | IR Cross    | Comments               |

| е      | RC1117       | IRU1117     | Better Dropout Voltage |

| e      | RC1117-33    | IRU1117-33  | Better Dropout Voltage |

| e      | RC1584       | IRU1075     | Better Dropout Voltage |

| e      | RC1585       | IRU1050     | Better Dropout Voltage |

| e      | RC1585-33    | IRU1050-33  | Better Dropout Voltage |

| е      | RC1587       | IRU1030     | Better Dropout Voltage |

|        | RC1587-33    | IRU1030-33  | Better Dropout Voltage |

| е      |              |             |                        |

| e      | LINEAR TECHN | IOLOGY      |                        |

| е      | Part #       | IR Cross    | Comments               |

|        | LT1083       | IRU1075     |                        |

|        | LT1084       | IRU1050     | Better dropout Voltage |

|        | LT1084-33    | IRU1050-33  |                        |

| ~      | LT1085       | IRU1030     | Better dropout Voltage |

| e      | LT1085-33    | IRU1030-33  |                        |

| e      | LT1086       | IRU1015     | Better dropout Voltage |

| e      | LT1086-33    | IRU1015-33  |                        |

| e<br>e | LT1117       | IRU1117     |                        |

| e<br>9 | LT1117-18    | IRU1117-18  |                        |

| e<br>9 | LT1117-25    | IRU1117-25  |                        |

| e<br>e | LT1117-33    | IRU1117-33  |                        |

| 0      | 1 74 500     |             |                        |

IRU1175

IRU1150

IRU1075

IRU1050

IRU1030

IRU1050-33

IRU1030-33

Better dropout Voltage

Better dropout Voltage

LT1580

LT1582

LT1584

LT1585

LT1587

LT1585-33

LT1587-33

# **Cross Reference by Manufacturer**

| LINFINITY MIC | <b>RO ELECTRON</b> | ICS                                              | MICREL              |                    |                                                  |

|---------------|--------------------|--------------------------------------------------|---------------------|--------------------|--------------------------------------------------|

| Part #        | IR Cross           | Comments                                         | Part #              | IR Cross           | Comments                                         |

| LX8117        | IRU1117            | Better Dropout Voltage                           | MIC39100-1.8        | IRU1206-18         |                                                  |

| LX8117-25     | IRU1117-25         | Better Dropout Voltage                           | MIC39100-2.5        | IRU1206-25         |                                                  |

| LX8117-33     | IRU1117-33         | Better Dropout Voltage                           | MIC39100-3.3        | IRU1206-33         |                                                  |

| LX8117A       | IRU1117            | Better Dropout Voltage                           | MIC39101-1.8        | IRU1207-18         |                                                  |

| LX8117A-25    | IRU1117-25         | Better Dropout Voltage                           | MIC39101-2.5        | IRU1207-25         |                                                  |

| LX8117A-33    | IRU1117-33         | Better Dropout Voltage                           | MIC39101-3.3        | IRU1207-33         |                                                  |

| LX8383        | IRU1075            | Better Dropout Voltage                           | MIC39102            | IRU1209            |                                                  |

| LX8383A       | IRU1075            | Beller Diopour vollage                           | MIC5205             | IRU1205            |                                                  |

| LX8384        | IRU1050            | Better Dropout Voltage                           |                     |                    |                                                  |

| LX8384A       | IRU1050            | Better Dropout Voltage                           | SEMTECH             |                    |                                                  |

| LX8384-33     | IRU1050-33         | Better Dropout Voltage                           |                     |                    | 0                                                |

| LX8385        | IRU1030            | Better Dropout Voltage                           | Part #              | IR Cross           | Comments                                         |

| LX8385A       | IRU1030            | Better Dropout Voltage                           | EZ1083              | IRU1075            |                                                  |

| LX8385-33     | IRU1030-33         | Beller Diopoul vollage                           | EZ1084              | IRU1050            |                                                  |

| LX8386        | IRU1015            | Better Dropout Voltage                           | EZ1084-33           | IRU1050-33         |                                                  |

| LX8386-33     | IRU1015-33         | Beller Dropoul vollage                           | EZ1085              | IRU1030            |                                                  |

| LX8415        | IRU1010            |                                                  | EZ1085-33           | IRU1030-33         |                                                  |

| LX8415-25     | IRU1010-25         |                                                  | EZ1086              | IRU1015            |                                                  |

| LX8415-33     | IRU1010-23         |                                                  | EZ1086-33           | IRU1015-33         | Better Dropout Voltage                           |

| LX8580        | IRU1175            | Pottor Dropout Voltago                           | EZ1117              | IRU1117            | Better Dropout Voltage                           |

| LX8584        | IRU1075            | Better Dropout Voltage<br>Better Dropout Voltage | EZ1117-25           | IRU1117-25         | Better Dropout Voltage                           |

| LX8585        | IRU1050            | Better Dropout Voltage                           | EZ1117-33           | IRU1117-33         | Better Dropout Voltage                           |

| LX8585-33     | IRU1050-33         | Beller Dropoul vollage                           | EZ1580              | IRU1175            |                                                  |

| LX8586        | IRU1050-55         | Better Dropout Voltage                           | EZ1581              | IRU1160            | Better Dropout Voltage                           |

| LX8586A       | IRU1075            | Better Dropout Voltage                           | EZ1582              | IRU1150            | Better Dropout Voltage                           |

| LX8587        | IRU1030            | Better Dropout Voltage                           | EZ1583              | IRU1150            | Better Dropout Voltage                           |

| LX8587A       | IRU1030            | Better Dropout Voltage                           | EZ1584              | IRU1075            |                                                  |

| LX8587-33     | IRU1030-33         | Beller Diopour vollage                           | EZ1585              | IRU1050            |                                                  |

| LX8610-25     | IRU1206-25*        | Better Dropout Voltage                           | EZ1585A             | IRU1050            |                                                  |

| LX8610-33     | IRU1206-33*        | Better Dropout Voltage                           | EZ1585-33           | IRU1050-33         |                                                  |

|               | 1101200 00         | Beller Bropoul Vollage                           | EZ1587              | IRU1030            | Better Dropout Voltage                           |

|               |                    |                                                  | EZ1587A             | IRU1030            | Better Dropout Voltage                           |

| NATIONAL      |                    |                                                  | EZ1587-33<br>EZ1588 | IRU1030-33         | Better Dropout Voltage                           |

| Part #        | IR Cross           | Comments                                         | SC1117              | IRU1030<br>IRU1117 | Better Dropout Voltage<br>Better Dropout Voltage |

| LM1084        | IRU1050            | Better Dropout Voltage                           | SC1117-33           | IRU1117-33         | Better Dropout Voltage                           |

| LM1084-33     | IRU1050-33         | Better Dropout Voltage                           | SC1202              | IRU1010            | Better Dropout Voltage                           |

| LM1085        | IRU1030            | Better Dropout Voltage                           | SC1202<br>SC1202-33 | IRU1010-33         | Better Dropout Voltage                           |

| LM1085-33     | IRU1030-33         | Better Dropout Voltage                           | SC431L              | IRU431L            | Beller Diopoul vollage                           |

| LM1086        | IRU1015            | Better Dropout Voltage                           | SC5205              | IRU1205            |                                                  |

| LM1086-33     | IRU1015-33         | Better Dropout Voltage                           | 303203              | 11(01205           |                                                  |

| LM1117        | IRU1117            | Better Dropout Voltage                           |                     |                    |                                                  |

| LM1117-33     | IRU1117-33         | Better Dropout Voltage                           | ST                  |                    |                                                  |

| LMS1585A      | IRU1050            |                                                  | Part #              | IR Cross           | Comments                                         |

| LMS1587       | IRU1030            | Better Dropout Voltage                           | LD1117D             | IRU1117            | Better Dropout Voltage                           |

| LMS8117       | IRU1010            | Better Dropout Voltage                           | LD1117D-33          | IRU1117-33         | Better Dropout Voltage                           |

|               |                    |                                                  | LF33CDT             | IRU1206-33CD       | Better Dropout Voltage                           |

|               |                    |                                                  | TEXAS INSTR         | UMENTS             |                                                  |

|               |                    |                                                  | Part #              | IR Cross           | Comments                                         |

|               |                    |                                                  | TLV431A             | IRU431L            |                                                  |

\*Not drop-in, but pin compatible only with SOT-223 packages. Refer to the datasheet to determine the suitability of the replacement for the specific application.

# Section 2: Linear Regulators

| Selection Gui | ides                                                                                  |

|---------------|---------------------------------------------------------------------------------------|

| IRU431L       | Low Voltage Adjustable Precision Shunt Regulator                                      |

| IRU431AL      | Low Voltage Adjustable Precision Shunt Regulator                                      |

| IRU1010       | 1A Low Dropout Positive Adjustable Regulator                                          |

| IRU1010-18    | 1A Low Dropout Positive Fixed 1.8V Regulator                                          |

| IRU1010-25    | 1A Low Dropout Positive Fixed 2.5V Regulator                                          |

| IRU1010-33    | 1A Low Dropout Positive Fixed 3.3V Regulator                                          |

| IRU1011-33    | 1.3A Low Dropout Positive Fixed Regulator                                             |

| IRU1015       | 1.5A Low Dropout Positive Adjustable Regulator                                        |

| IRU1015-33    | 1.5A Low Dropout Positive Fixed 3.3V Regulator                                        |

| IRU1030       | 3A Low Dropout Positive Adjustable Regulator                                          |

| IRU1030-33    | 3A Low Dropout Positive Fixed 3.3V Regulator                                          |

| IRU1050       | 5A Low Dropout Positive Adjustable Regulator                                          |

| IRU1050-33    | 5A Low Dropout Positive Fixed 3.3V Regulator                                          |

| IRU1075       | 7.5A Low Dropout Positive Adjustable Regulator                                        |

| IRU1117       | 800mA Low Dropout Positive Adjustable Regulator                                       |

| IRU1117-18    | 800mA Low Dropout Positive Fixed 1.8V Regulator                                       |

| IRU1117-25    | 800mA Low Dropout Positive Fixed 2.5V Regulator                                       |

| IRU1117-33    | 800mA Low Dropout Positive Fixed 3.3V Regulator                                       |

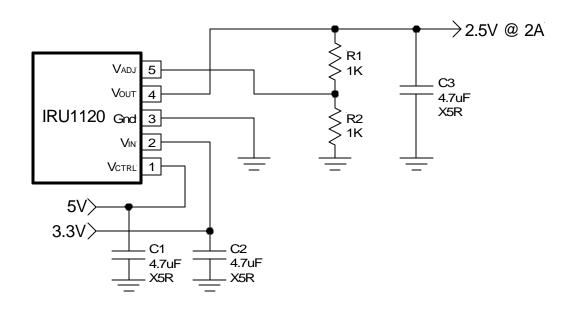

| IRU1120       | 2A Low Dropout Positive Adjustable Regulator                                          |

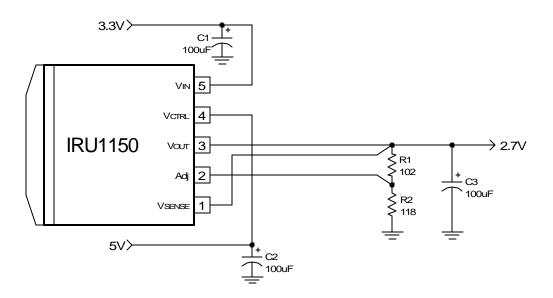

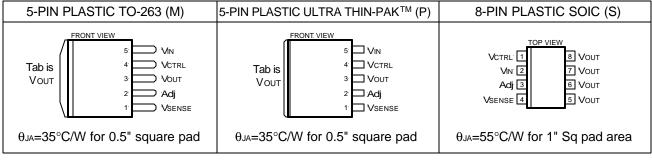

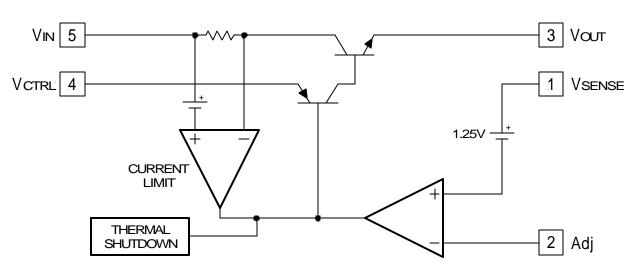

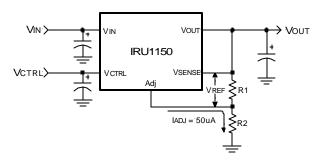

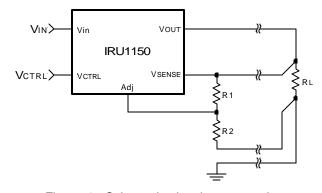

| IRU1150       | 4A Ultra Low Dropout Positive Adjustable Regulator                                    |

| IRU1160       | 6A Ultra Low Dropout Positive Adjustable Regulator                                    |

| IRU1175       | 7.5A Ultra Low Dropout Positive Adjustable Regulator                                  |

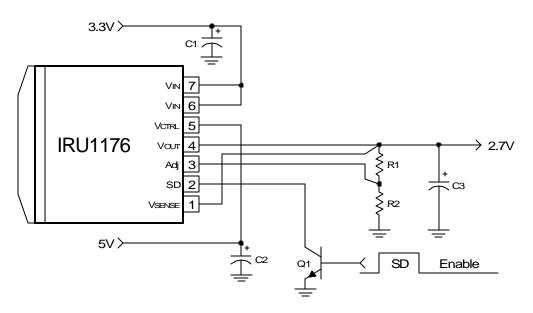

| IRU1176       | 7.5A Ultra Low Dropout Positive Adjustable Regulator with Shutdown Input              |

| IRU1205       | 300mA Ultra Low Dropout Positive Adjustable Regulator                                 |

| IRU1205-18    | 300mA Ultra Low Dropout Positive Fixed 1.8V Regulator                                 |

| IRU1205-25    | 300mA Ultra Low Dropout Positive Fixed 2.5V Regulator                                 |

| IRU1205-28    | 300mA Ultra Low Dropout Positive Fixed 2.8V Regulator                                 |

| IRU1205-30    | 300mA Ultra Low Dropout Positive Fixed 3V Regulator                                   |

| IRU1205-33    | 300mA Ultra Low Dropout Positive Fixed 3.3V Regulator                                 |

| IRU1205-36    | 300mA Ultra Low Dropout Positive Fixed 3.6V Regulator                                 |

| IRU1206-18    | 1A Ultra Low Dropout Positive Fixed 1.8V Regulator                                    |

| IRU1206-25    | 1A Ultra Low Dropout Positive Fixed 2.5V Regulator                                    |

| IRU1206-33    | 1A Ultra Low Dropout Positive Fixed 3.3V Regulator                                    |

| IRU1207-18    | 1A Ultra Low Dropout Positive Fixed 1.8V Regulator with Enable and Output Flag Pins   |

| IRU1207-25    | 1A Ultra Low Dropout Positive Fixed 2.5V Regulators with Enable and Output Flag Pins. |

| IRU1207-33    | 1A Ultra Low Dropout Positive Fixed 3.3V Regulator with Enable and Output Flag Pins   |

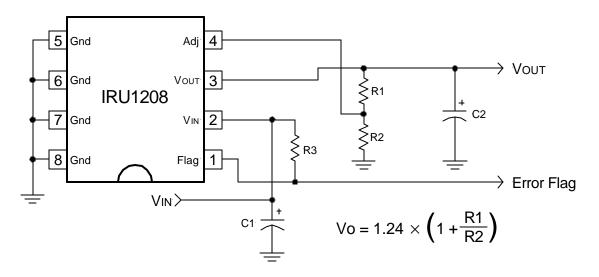

| IRU1208       | 1A Ultra Low Dropout Positive Adjustable Regulator with Output Flag Pin               |

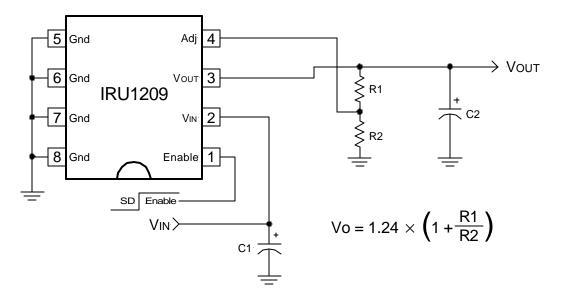

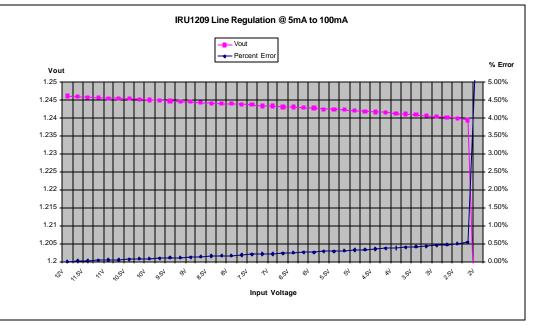

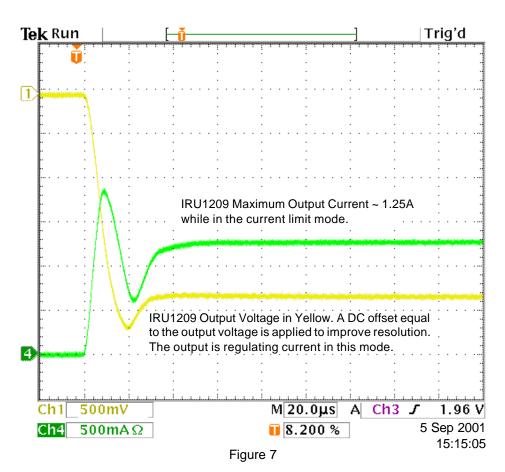

| IRU1209       | 1A Ultra Low Dropout Positive Adjustable Regulator with Enable Pin                    |

|               |                                                                                       |

# SINGLE LOW DROPOUT SELECTION GUIDE

|             |           | FEATU                 | RES                | 5      |            | PACKAGES                |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      |            |           |                   |                   |                      |                    |

|-------------|-----------|-----------------------|--------------------|--------|------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|----------------------|----------------------|----------------------|----------------------|------------|-----------|-------------------|-------------------|----------------------|--------------------|

| Part #      | lo<br>(A) | Max<br>Dropout<br>(V) | Adj/<br>Fix<br>(V) | SD Pin | Error Flag | D TO-252<br>2-Pin D-Pak | HLPM<br>6-Pin 3x3 | F SOT-23<br>3-Pin | г SOT-23<br>5-Pin | F SOT-23<br>6-Pin | ■ TO-263<br>3-Pin | TO-263     5-Pin | ▼ TO-263<br>7-Pin | ы 2-Pin<br>UThin-Pak | ы 3-Pin<br>UThin-Pak | ъ 5-Pin<br>UThin-Pak | ъ 7-Pin<br>UThin-Pak | o SOIC Pwr | <br>3-Pin | - TO-220<br>5-Pin | H TO-220<br>7-Pin | C 8-Pin<br>Mini MSOP | ≺ SOT-223<br>3-Pin |

| IRU1175     | 7.5       | 0.5                   | ADJ                |        |            |                         |                   |                   |                   | 20                |                   | x                |                   |                      | •                    | x                    | •                    | x          |           | •                 |                   |                      |                    |

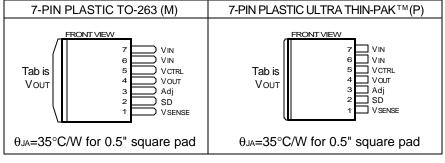

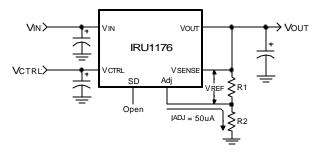

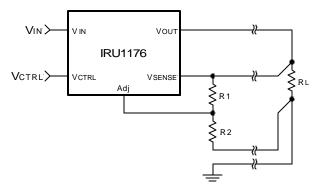

| IRU1176     | 7.5       | 0.65                  | ADJ                | x      |            |                         |                   |                   |                   |                   |                   |                  | x                 |                      |                      |                      | x                    |            |           |                   |                   | -                    |                    |

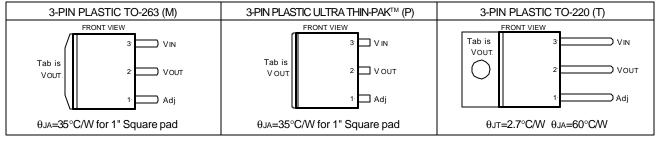

| IRU1075     | 7.5       | 1                     | ADJ                |        |            |                         |                   |                   |                   |                   | х                 |                  |                   |                      | x                    |                      |                      |            | x         |                   |                   |                      |                    |

| IRU1160     | 6         | 0.62                  | ADJ                |        |            |                         |                   |                   |                   |                   |                   | x                |                   |                      |                      | х                    |                      |            |           |                   |                   |                      |                    |

| IRU1050-33  | 5         | 1.3                   | FIX<br>3.3         |        |            | х                       |                   |                   |                   |                   | х                 |                  |                   | x                    |                      |                      |                      |            | x         |                   |                   |                      |                    |

| IRU1050     | 5         | 1.3                   | ADJ                |        |            | х                       |                   |                   |                   |                   | х                 |                  |                   | x                    |                      |                      |                      |            | x         |                   |                   |                      |                    |

| IRU1150     | 4         | 0.7                   | ADJ                |        |            |                         |                   |                   |                   |                   |                   | x                |                   |                      |                      | х                    |                      | x          |           |                   |                   |                      |                    |

| IRU1030-33  | 3         | 1.3                   | FIX<br>3.3         |        |            | x                       |                   |                   |                   |                   | х                 |                  |                   | x                    |                      |                      |                      |            | x         |                   |                   |                      |                    |

| IRU1030     | 3         | 1.3                   | ADJ                |        |            | x                       |                   |                   |                   |                   | х                 |                  |                   |                      |                      |                      |                      |            | x         |                   |                   |                      |                    |

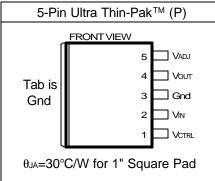

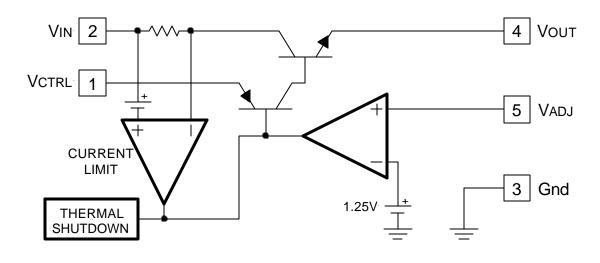

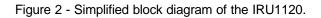

| IRU1120*    | 2         | 1.25                  | ADJ                |        |            |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      | х                    |                      |            |           |                   |                   |                      |                    |

| IRU1015-33  | 1.5       | 1.3                   | FIX<br>3.3         |        |            | x                       |                   |                   |                   |                   | х                 |                  |                   | х                    |                      |                      |                      |            | x         |                   |                   |                      |                    |

| IRU1015     | 1.5       | 1.3                   | ADJ                |        |            | x                       |                   |                   |                   |                   | х                 |                  |                   |                      |                      |                      |                      |            | x         |                   |                   |                      |                    |

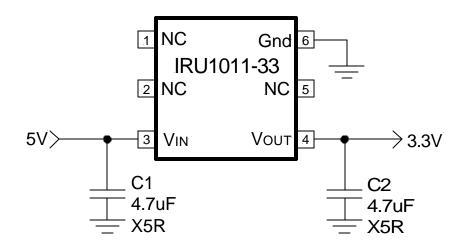

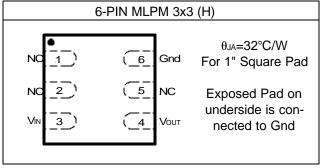

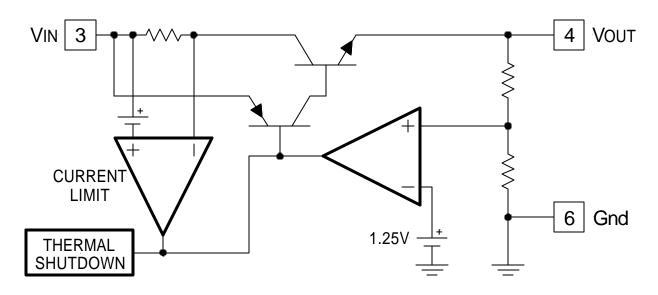

| IRU1011-33* | 1.3       | 1.3                   | FIX<br>3.3         |        |            |                         | x                 |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      |            |           |                   |                   |                      |                    |

| IRU1206-18  | 1         | 0.60                  | FIX<br>1.8         |        |            | х                       |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      |            |           |                   |                   |                      | x                  |

| IRU1207-18  | 1         | 0.60                  | FIX<br>1.8         | x      | х          |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      | x          |           |                   |                   |                      |                    |

| IRU1206-25  | 1         | 0.60                  | FIX<br>2.5         |        |            | х                       |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      |            |           |                   |                   |                      | x                  |

| IRU1207-25  | 1         | 0.60                  | FIX<br>2.5         | x      | х          |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      | x          |           |                   |                   |                      |                    |

| IRU1206-33  | 1         | 0.60                  | FIX<br>3.3         |        |            | x                       |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      |            |           |                   |                   |                      | x                  |

| IRU1207-33  | 1         | 0.60                  | FIX<br>3.3         | x      | x          |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      | x          |           |                   |                   |                      |                    |

| IRU1208     | 1         | 0.60                  | ADJ                |        | x          |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      | x          |           |                   |                   |                      |                    |

| IRU1209     | 1         | 0.60                  | ADJ                | x      |            |                         |                   |                   |                   |                   |                   |                  |                   |                      |                      |                      |                      | x          |           |                   |                   | 1                    |                    |

\*Note: Stable with ceramic capacitor.

## SINGLE LOW DROPOUT SELECTION GUIDE CONTINUED

|             | FEATURES  |                       |                    |        |            |                       |                   |                 |                 |                 |                 |                 | PA              | CK                 | ٩GE                | ES                 |                    |                   |                 |                 |                 |                    |                  |

|-------------|-----------|-----------------------|--------------------|--------|------------|-----------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------------------|--------------------|--------------------|--------------------|-------------------|-----------------|-----------------|-----------------|--------------------|------------------|

| Part #      | lo<br>(A) | Max<br>Dropout<br>(V) | Adj/<br>Fix<br>(V) | SD Pin | Error Flag | TO-252<br>2-Pin D-Pak | MLPM<br>6-Pin 3x3 | SOT-23<br>3-Pin | SOT-23<br>5-Pin | SOT-23<br>6-Pin | TO-263<br>3-Pin | TO-263<br>5-Pin | TO-263<br>7-Pin | 2-Pin<br>UThin-Pak | 3-Pin<br>UThin-Pak | 5-Pin<br>UThin-Pak | 7-Pin<br>UThin-Pak | 8-Pin<br>SOIC Pwr | TO-220<br>3-Pin | TO-220<br>5-Pin | TO-220<br>7-Pin | 8-Pin<br>Mini MSOP | SOT-223<br>3-Pin |

|             |           |                       |                    |        | _          | D                     | Н                 | L3              | L5              | L6              | М               | М               | М               | Р                  | Р                  | Ρ                  | Р                  | S                 | Т               | Т               | Т               | U                  | Y                |

| IRU1010-18  | 1         | 1.3                   | FIX<br>1.8         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1010-25  | 1         | 1.3                   | FIX<br>2.5         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1010-33  | 1         | 1.3                   | FIX<br>3.3         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | х                  |                    |                    |                    | х                 |                 |                 |                 |                    | x                |

| IRU1010     | 1         | 1.3                   | ADJ                |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1117-18  | 0.8       | 1.2                   | FIX<br>1.8         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1117-25  | 0.8       | 1.2                   | FIX<br>2.5         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | х                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1117-33  | 0.8       | 1.2                   | FIX<br>3.3         |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1117     | 0.8       | 1.2                   | ADJ                |        |            | x                     |                   |                 |                 |                 |                 |                 |                 | x                  |                    |                    |                    | x                 |                 |                 |                 |                    | x                |

| IRU1205-18* | 0.3       | 0.40                  | FIX<br>1.8         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

| IRU1205-25* | 0.3       | 0.40                  | FIX<br>2.5         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

| IRU1205-28* | 0.3       | 0.40                  | FIX<br>2.8         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

| IRU1205-30* | 0.3       | 0.40                  | FIX<br>3.0         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

| IRU1205-33* | 0.3       | 0.40                  | FIX<br>3.3         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

| IRU1205-36* | 0.3       | 0.40                  | FIX<br>3.6         |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 | 1                  |                  |

| IRU1205*    | 0.3       | 0.40                  | ADJ                |        |            |                       |                   |                 | x               |                 |                 |                 |                 |                    |                    |                    |                    |                   |                 |                 |                 |                    |                  |

\*Note: Stable with ceramic capacitor.

# International **TOR** Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01

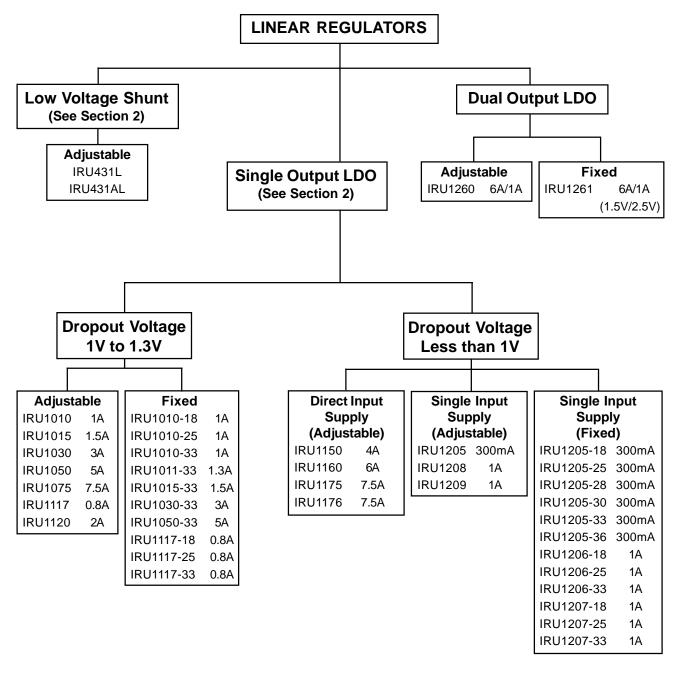

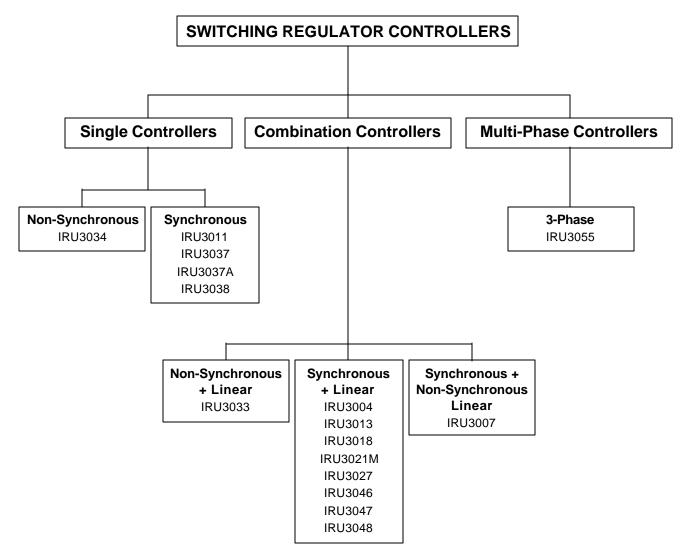

# **Selection Tree**

International **TGR** Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01

www.irf.com

# IRU431L / IRU431AL

# LOW -VOLTAGE ADJUSTABLE PRECISION SHUNT REGULATOR

## **FEATURES**

- SOT-23 Packages

- Voltage Reference Initial Accuracy (1% for IRU431L and 0.5% for IRU431AL)

- Low Operating Cathode Current (80µA max)

- Unconditionally Stable with only 1µF

- Adjustable Output from 1.24V to 15V

- $0.25\Omega$  Typical Output Impedance

- Pin to Pin Compatible with TLV431

# **APPLICATIONS**

- Precision Voltage Reference

- Linear Regulator Controller

- Secondary Side Controller for the low voltage power supply applications

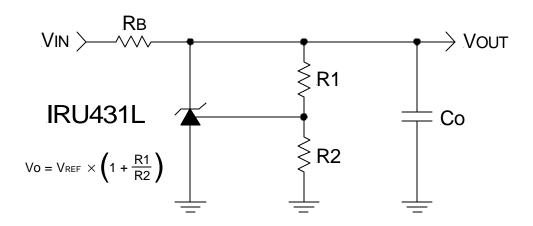

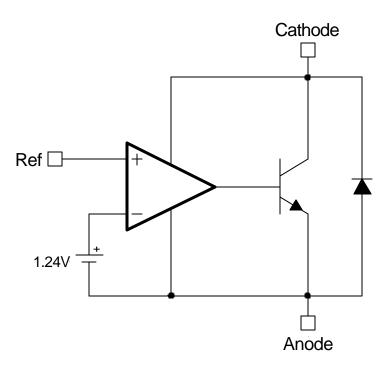

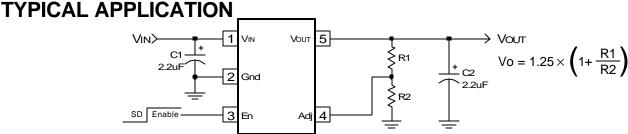

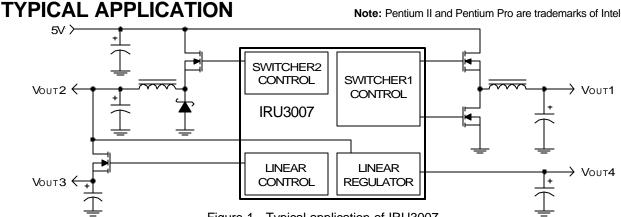

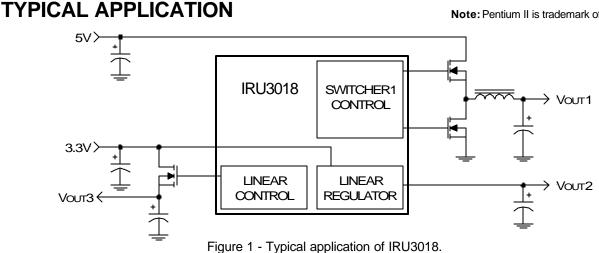

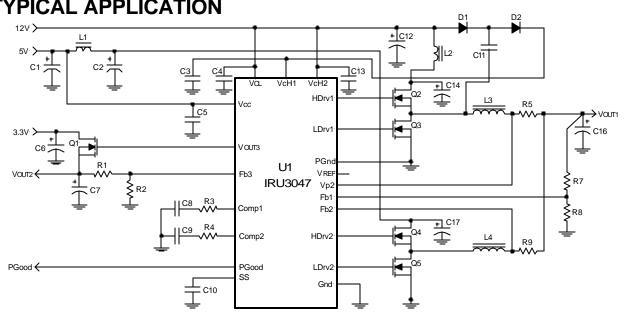

# **TYPICAL APPLICATION**

### DESCRIPTION

The IRU431L family are three-terminal adjustable shunt regulators that can also be used as precision voltage references. Its output voltage may be set to any value between V<sub>REF</sub>(1.24V) and 15V with two external resistors as shown in the typical application circuit. Other applications of this device include being used as a merged amplifier and reference in applications such as a linear regulator or as the secondary side controller in low voltage power supply applications. The IRU431L only requires  $80\mu$ A maximum quiescent current before regulating, making it ideal as a voltage reference for battery type applications. The IRU431L has  $\pm 1\%$  initial accuracy while IRU431AL provides  $\pm 0.5\%$  initial accuracy.

Figure 1 - Typical application of the IRU431L as a shunt regulator / voltage reference.

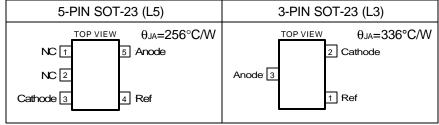

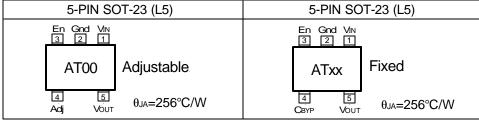

## PACKAGE ORDER INFORMATION

| T₄ (°C) | 5-PIN SOT-23 (L5) | 3-PIN SOT-23 (L3) |

|---------|-------------------|-------------------|

| 0 To 70 | IRU431LCL5        | IRU431LCL3        |

| 0 To 70 | IRU431ALCL5       | IRU431ALCL3       |

# **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage (VIN)                  | 15V            |

|--------------------------------------|----------------|

| Continuous Cathode Current Range     | -15mA to +15mA |

| Reference Current Range              | -0.05mA to 1mA |

| Storage Temperature Range            | -65°C to 150°C |

| Operating Junction Temperature Range | 0°C to 150°C   |

# PACKAGE INFORMATION

## **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over  $T_A=0$  to 70°C,  $Co=1\mu F$ . Typical values refer to  $T_A=25$ °C. Low duty cycle pulse testing is used which keeps junction and case temperatures equal to the ambient temperature.

| PARAMETER                 | SYM                              | TEST CONDITION                         | MIN   | TYP   | MAX   | UNITS |

|---------------------------|----------------------------------|----------------------------------------|-------|-------|-------|-------|

| Reference Voltage         | Vref                             | Iк=10mA, Vка=Vref, Ta=25°С             | 1.228 | 1.240 | 1.252 | V     |

| IRU431L                   |                                  | Ik=10mA, Vka=Vref                      | 1.221 | 1.240 | 1.259 |       |

| Reference Voltage         | Vref                             | IK=10mA, VKA=VREF, TA=25°C             | 1.234 | 1.240 | 1.246 | V     |

| IRU431AL                  |                                  | Ik=10mA, Vka=Vref                      | 1.228 | 1.240 | 1.252 |       |

| VREF Deviation over full  | VREF(DEV)                        | Vka=Vref, Ik=10mA                      |       | 6     |       | mV    |

| temperature range         |                                  | Note 1                                 |       |       |       |       |

| Ratio of VREF change to   | $\Delta V_{REF} / \Delta V_{KA}$ | IK=10mA, $\Delta V_{KA}=V_{REF}$ to 6V |       | -1    | -6    | mV/V  |

| cathode voltage change    |                                  |                                        |       |       |       |       |

| Reference Pin Current     |                                  | lκ=10mA, R1=10KΩ, R2=open              |       | 0.15  | 1     | μA    |

| IREF Deviation over full  | REF(DEV)                         | lκ=10mA, R1=10KΩ, R2=open              |       | 0.05  |       | μA    |

| temperature range         |                                  | Note 1                                 |       |       |       |       |

| Minimum Cathode Current   | K(MIN)                           | Vka=Vref                               |       | 55    | 80    | μA    |

| Off State Cathode Current | loff                             | Vka=6V, Vref=0V                        |       | 0.6   | 0.75  | μA    |

|                           |                                  | Vka=10V, Vref=0V                       |       | 1.8   | 5     |       |

|                           |                                  | Vka=15V, Vref=0V                       |       | 3.2   | 10    |       |

| Dynamic Impedance         | ZKAO                             | Vka=Vref, f<1KHz,                      |       | 0.25  | 0.4   | Ω     |

|                           |                                  | lκ=0.1 to 15mA, Note 2                 |       |       |       |       |

**Note 1:** The deviation parameters, V<sub>REF(DEV)</sub> and I<sub>REF(DEV)</sub> are defined as the differences between the maximum and the minimum values obtained over the rated temperature range. The average full range temperature coefficient of the reference input voltage is defined as:

$$|\alpha V_{\text{REF}}| = \frac{\left(\frac{V_{\text{REF}(\text{DEV})}}{V_{\text{REF}(25^{\circ}\text{C})}}\right) \times 10^{6}}{\Delta T_{\text{A}}}$$

Where:

|αVREF| unit is ppm/°C

$\Delta T_{\text{A}}$  is the rated operating free air temperature of the device.

$\alpha V_{\text{REF}}$  can be positive or negative depending on whether minimum V\_{\text{REF}} or maximum V\_{\text{REF}} respectively occurs at the lower temperature.

Note 2: The dynamic impedance when  $V_{\text{KA}}=V_{\text{REF}}$  is defined as:

$$|Z_{KA0}| = \frac{\Delta V_{KA}}{\Delta I_{K}}$$

When the device is operating with two external resistors (See Figure 3), the total dynamic impedance of the circuit is given by:

$$|Z_{KA}| = \frac{\Delta V}{\Delta I} = |Z_{KA0}| \times \left(1 + \frac{R1}{R2}\right)$$

## **PIN DESCRIPTIONS**

| 5-PIN | 3-PIN | PIN SYMBOL | PIN DESCRIPTION                                                                                                                                          |

|-------|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4     | 1     | Ref        | Resistors from the Ref pin to the Cathode pin and to ground form a divider that sets the output voltage.                                                 |

| 3     | 2     | Cathode    | The output of the shunt regulator. A capacitor of $1\mu$ F minimum value must be connected from this pin to Anode pin to insure unconditional stability. |

| 5     | 3     | Anode      | Ground pin. This pin must be connected to the lowest potential in the system and all other pins must be at higher potential with respect to this pin.    |

| 1, 2  | NA    | NC         | These pins are not connected internally.                                                                                                                 |

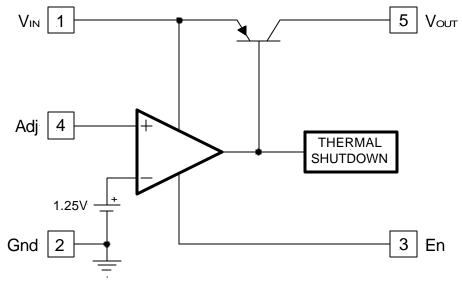

# **BLOCK DIAGRAM**

Figure 2 - Simplified block diagram of the IRU431L.

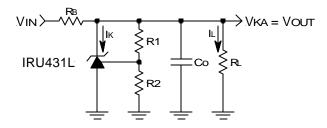

## **APPLICATION INFORMATION**

#### **Output Voltage Setting**

The IRU431L can be programmed to any voltages in the range of 1.24 to 15V with the addition of R1 and R2 external resistors according to the following formula:

$$Vo = V_{KA} = V_{REF} \times \left(1 + \frac{R1}{R2}\right) + I_{REF} \times R1$$

The IRU431L keeps a constant voltage of 1.240V between the Ref pin and Ground pin. By placing a resistor R2 across these two pins a constant current flows through R2, adding to the  $k_{\text{EF}}$  current and into the R1 resistor producing a voltage equal to:

$$\left(rac{1.240}{\text{R2}}

ight) imes$$

R1 + Iref  $imes$  R1

which will be added to the 1.240V to set the output voltage as shown in the above equation. Since the input bias current of the Ref pin is  $0.5\mu$ A max, it adds a very small error to the output voltage and for most applications can be ignored. For example, in a typical 5V to 3.3V application where R2=1.21K $\Omega$  and R1=2K $\Omega$  the error due to the IADJ is only 1mV which is about 0.03% of the nominal set point.

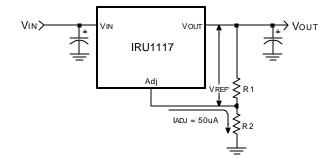

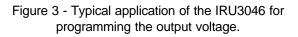

Figure 3 - Typical application of the IRU431L for programming the output voltage.

#### Biasing Resistor (RB) Selection

The biasing resistor  $R_B$  is selected such that it does not limit the input current under the minimum input supply and maximum load and biasing current.

An example is given below on how to properly select the biasing resistor.

Assuming:

The maximum value for the biasing resistor is calculated using the following equations:

$$R_{B(MAX)} = \frac{V_{MIN} - V_{KA}}{I_{B(MAX)} + I_{L(MAX)}}$$

$$I_{B(MAX)} = I_{K(MIN)} + I_{R}$$

Where:

V<sub>MIN</sub> = Minimum supply voltage I<sub>L(MAX)</sub> = Maximum load current I<sub>B(MAX)</sub> = Maximum bias current I<sub>K(MIN)</sub> = Maximum value for the minimum cathode current spec I<sub>R</sub> = Current through R1

Assuming R1 =  $2K\Omega$  as before,

$$I_{R} = \frac{3.3 - 1.24}{2} = 1.03 \text{mA}$$

$$I_{B(MAX)} = 0.08 + 1.03 = 1.11 \text{mA}$$

$$R_{B(MAX)} = \frac{4.5 - 3.3}{1.11 + 10} = 108\Omega$$

Select  $R_B = 100\Omega$

The maximum power dissipation of the resistor is calculated under the maximum supply voltage as follows:

$$\mathsf{P}_{\mathsf{R}_{\mathsf{B}}(\mathsf{MAX})} = \frac{\left(\mathsf{V}_{\mathsf{MAX}} - \mathsf{V}_{\mathsf{KA}}\right)^2}{\mathsf{R}_{\mathsf{B}}}$$

Where:

$$\label{eq:VMAX} \begin{split} V_{\text{MAX}} &= Maximum \ supply \ voltage \\ P_{\text{R}_{\text{B}}(\text{MAX})} &= Maximum \ R_{\text{B}} \ power \ dissipation \end{split}$$

$$\mathsf{P}_{\mathsf{R}_{\mathsf{B}}(\mathsf{MAX})} = \frac{(6 - 3.3)^2}{100} = 73 \mathrm{mW}$$

#### Thermal Design

The IRU431L is offered in the surface mount SOT-23 (L) packages. The SOT-23 package has the maximum power dissipation capability of 150mW at  $T_A=25^{\circ}C$  with the derating factor of -1.2mW /  $^{\circ}C$ .

The table below summarizes the maximum power dissipation capability of each package versus ambient temperature.

|        | Ambient Temperature (T <sub>A</sub> ) °C |       |       |       |      |  |

|--------|------------------------------------------|-------|-------|-------|------|--|

| Pkg    | 25                                       | 40    | 50    | 60    | 70   |  |

| SOT-23 | 150mW                                    | 132mW | 120mW | 108mW | 96mW |  |

In our previous example, the maximum power dissipation of the device is calculated under no load and maximum input supply condition.

The maximum power is calculated using the following equation:

$$\mathsf{P}_{\mathsf{MAX}} = \mathsf{V}_{\mathsf{KA}} \times \left(\frac{\mathsf{V}_{\mathsf{MAX}} - \mathsf{V}_{\mathsf{KA}}}{\mathsf{R}_{\mathsf{B}}}\right)$$

Where:

$P_{MAX}$  = Maximum power dissipation of the 431L

For our example:

$$P_{MAX} = 3.3 \times \left(\frac{6 - 3.3}{100}\right) = 89 \text{mW}$$

As shown in the power dissipation table, both packages can handle this power dissipation.

#### Stability

The IRU431L has many different domains of stability as a function of the cathode current. As is typical of three-terminal shunt regulators, the IRU431L has many domains of stability. The actual domain in which any practical circuit operates is related to cathode current. In general the device will be unconditionally stable for any cathode current if a capacitor,  $1\mu$ F or larger, is connected between the cathode and the anode. If the cathode current is always higher than 3mA under minimum line and maximum load conditions, the capacitor value can be reduced to  $0.01\mu$ F and the system will be stable.

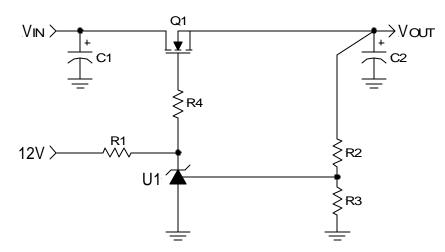

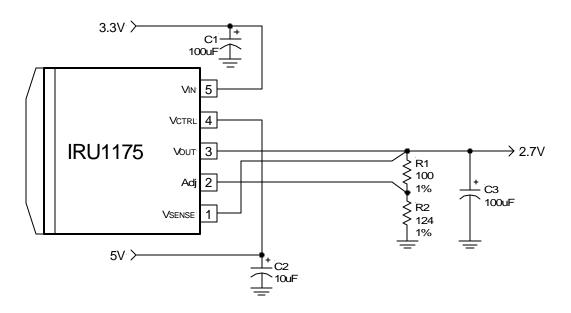

# **TYPICAL APPLICATION**

Figure 4 - Low cost 3.3V to 2.7V output.

| Ref Desig | Description     | Qty | Part #                                                           | Manuf     |

|-----------|-----------------|-----|------------------------------------------------------------------|-----------|

| U1        | Shunt Regulator | 1   | IRU431L                                                          | IR        |

| C1, C2    | Capacitor       | 2   | Elect, 220µF, 6.3V, ECAOJFQ221                                   | Panasonic |

| R1        | Resistor        | 1   | 6.2KΩ, 5%, SMT                                                   |           |

| R2        | Resistor        | 1   | 118Ω, 1%, SMT                                                    |           |

| R3, R4    | Resistor        | 2   | 100Ω, 1%, SMT                                                    |           |

| HS1       | Heat Sink       |     | Use minimum of 1" square copper pac<br>area for load current <4A |           |

International

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01

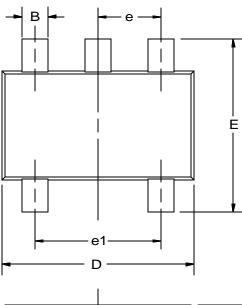

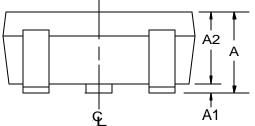

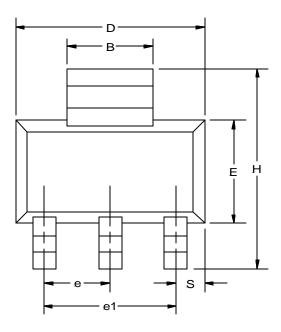

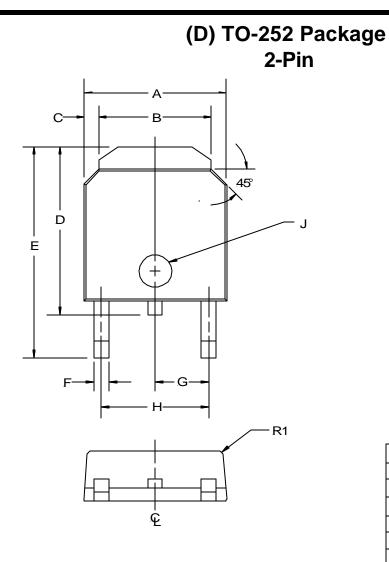

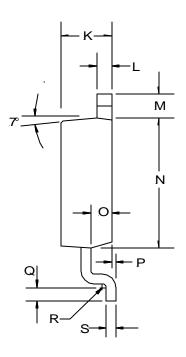

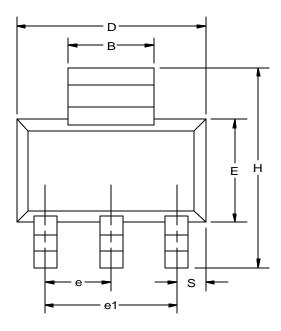

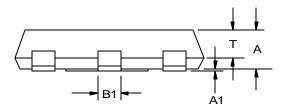

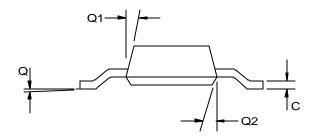

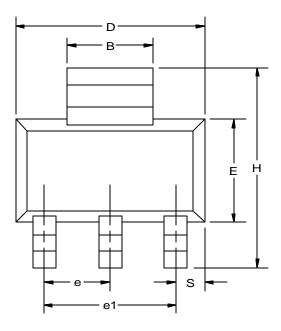

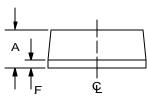

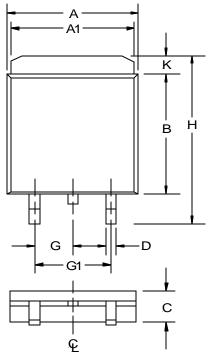

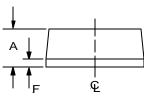

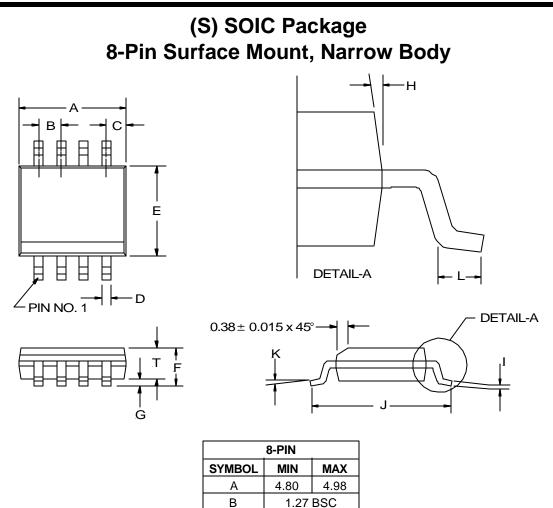

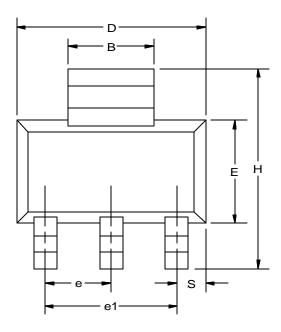

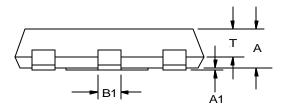

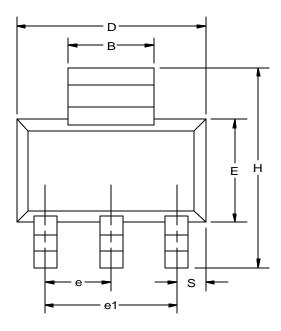

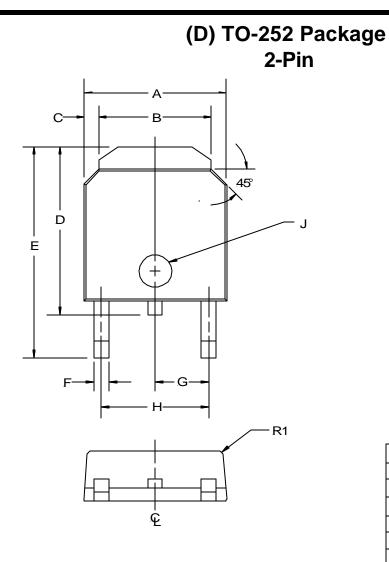

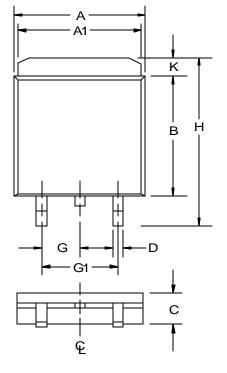

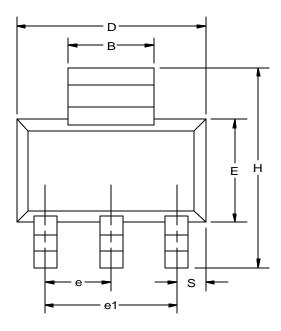

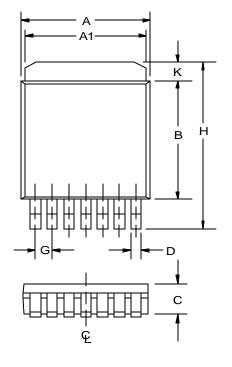

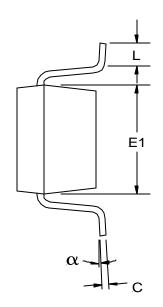

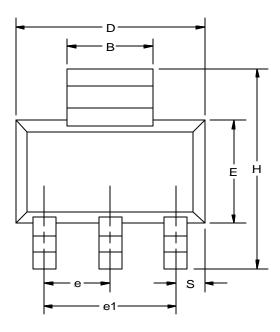

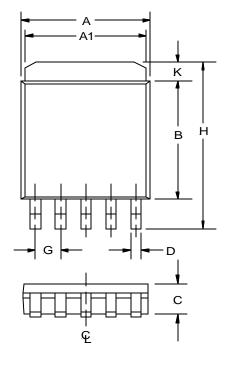

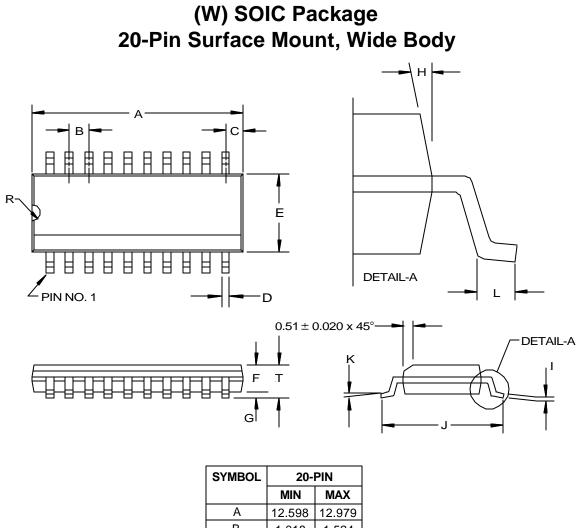

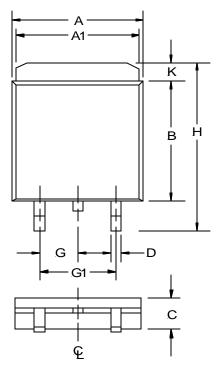

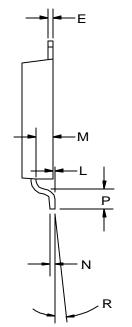

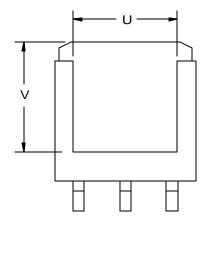

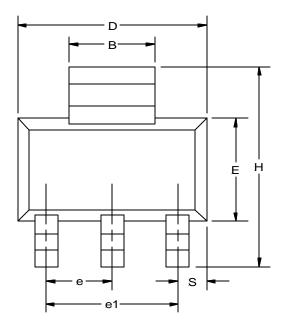

| SYMBOL | MIN      | MAX   |  |

|--------|----------|-------|--|

| Α      | 0.890    | 1.120 |  |

| A1     | 0.013    | 0.100 |  |

| В      | 0.370    | 0.510 |  |

| С      | 0.085    | 0.180 |  |

| D      | 2.800    | 3.040 |  |

| E      | 1.200    | 1.400 |  |

| е      | 0.890    | 1.030 |  |

| e1     | 1.780    | 2.050 |  |

| Н      | 2.100    | 2.640 |  |

| L      | 0.55 REF |       |  |

| S      | 0.450    | 0.600 |  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

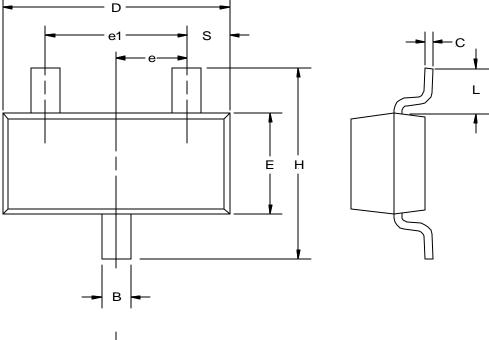

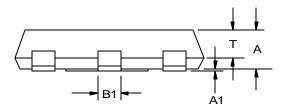

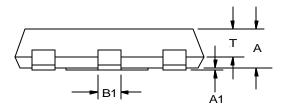

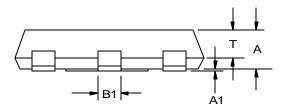

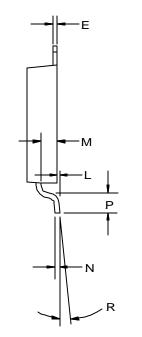

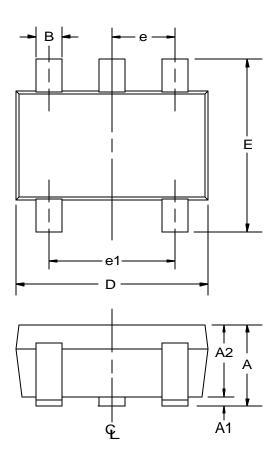

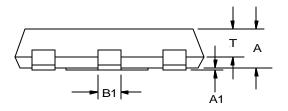

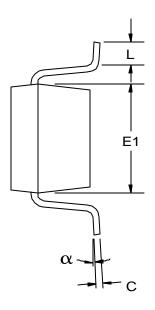

# IRU431L / IRU431AL

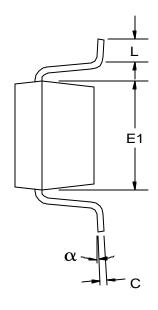

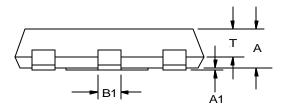

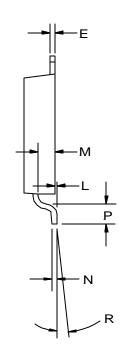

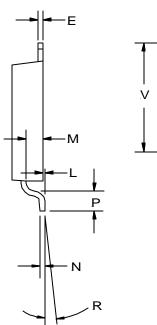

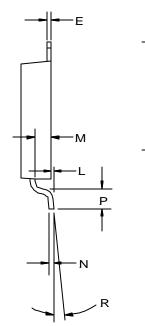

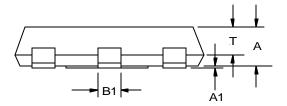

| SYMBOL | MIN  | MAX  |

|--------|------|------|

| А      | 0.90 | 1.45 |

| A1     | 0.00 | 0.15 |

| A2     | 0.90 | 1.30 |

| В      | 0.25 | 0.50 |

| С      | 0.09 | 0.20 |

| D      | 2.80 | 3.00 |

| Е      | 2.60 | 3.00 |

| E1     | 1.50 | 1.75 |

| е      | 0.95 | REF  |

| e1     | 1.90 | REF  |

| L      | 0.35 | 0.55 |

| α      | 0°   | 10°  |

NOTE: ALL MEASUREMENTS ARE IN MILLIMETERS.

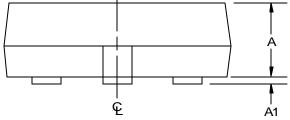

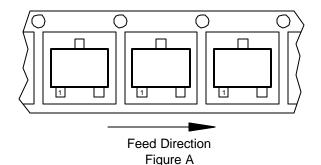

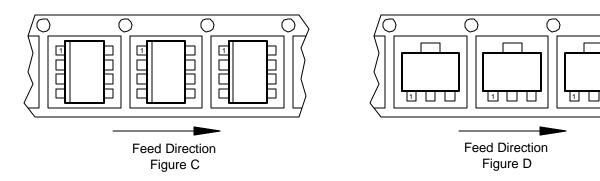

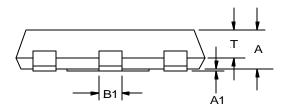

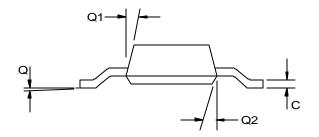

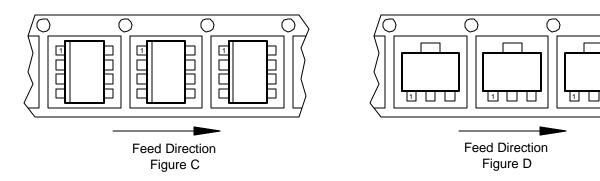

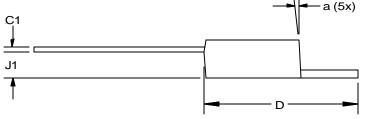

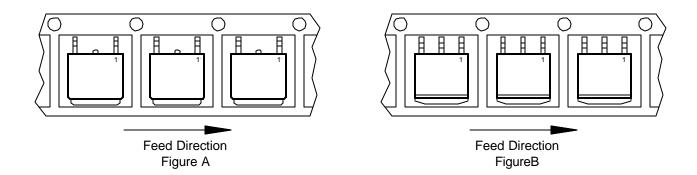

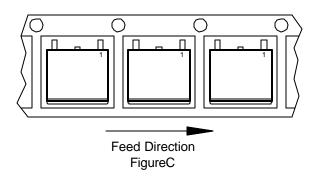

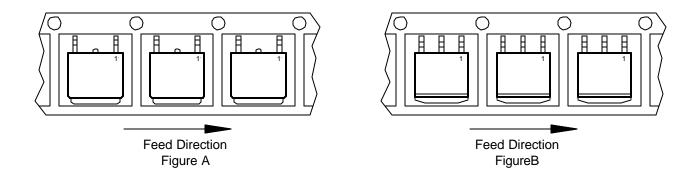

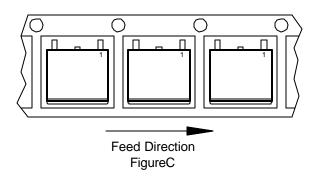

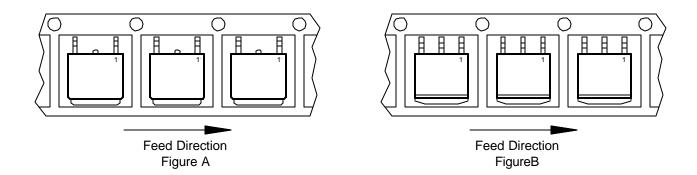

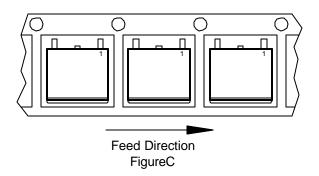

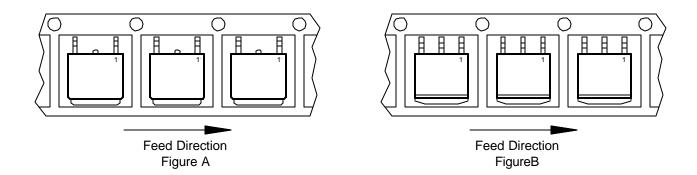

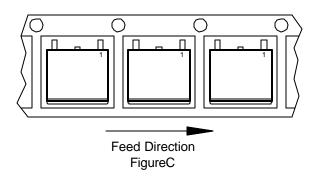

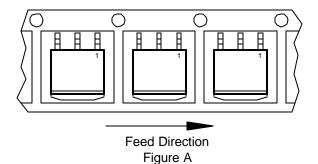

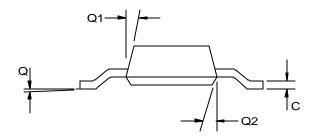

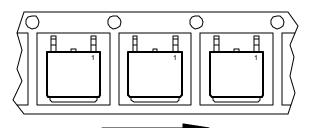

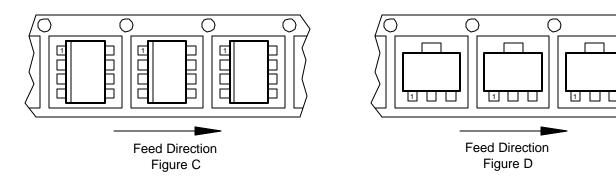

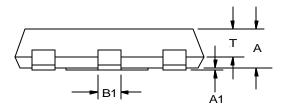

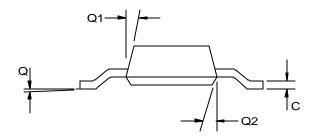

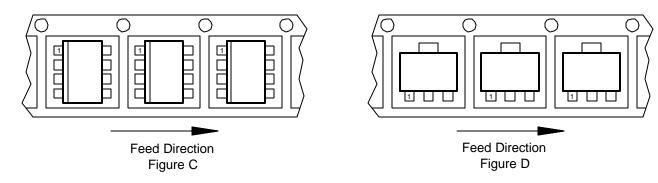

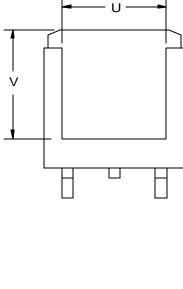

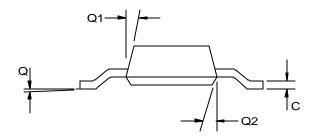

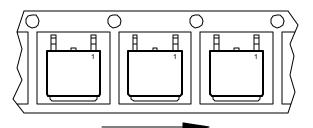

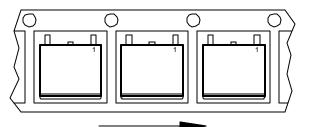

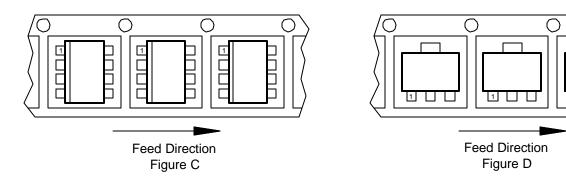

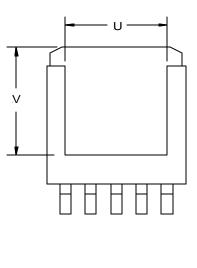

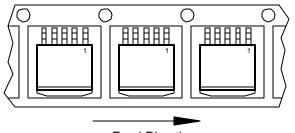

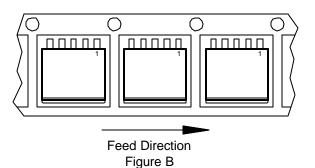

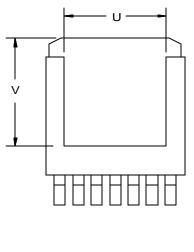

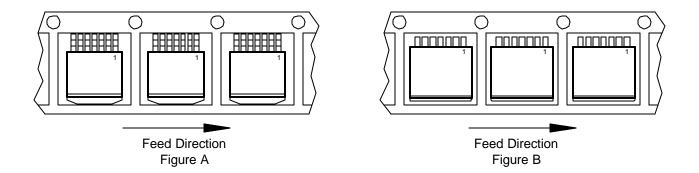

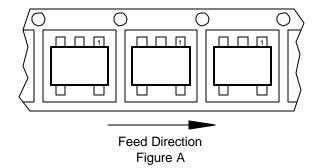

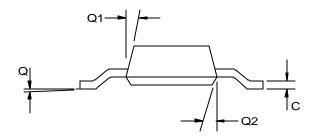

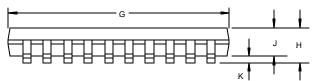

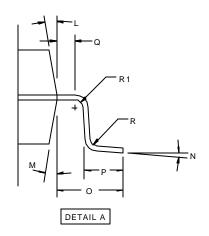

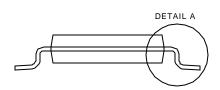

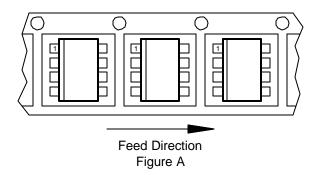

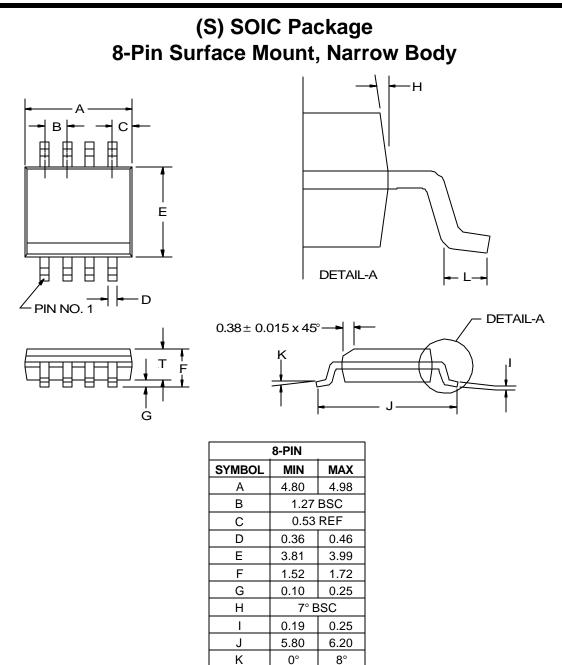

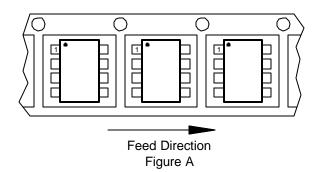

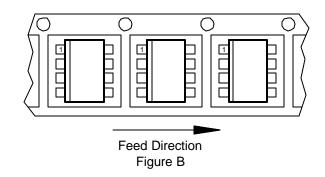

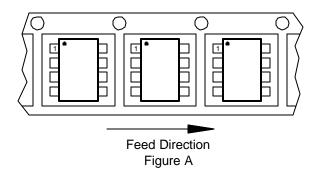

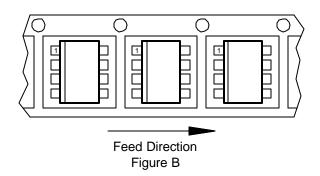

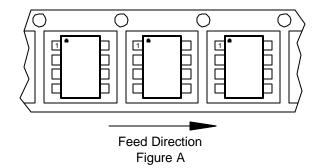

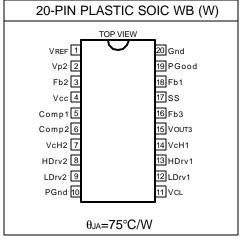

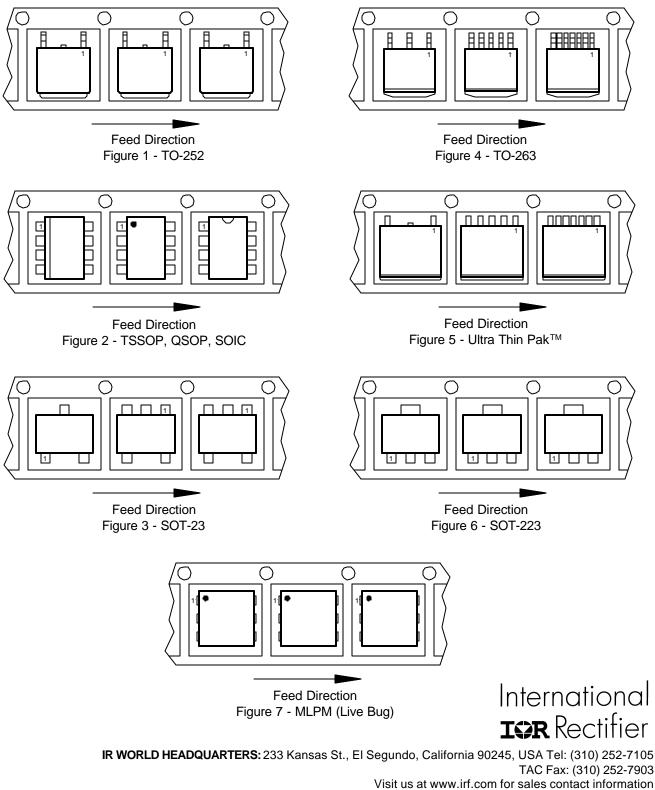

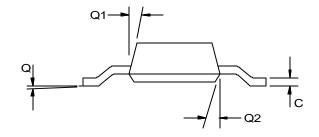

# PACKAGE SHIPMENT METHOD

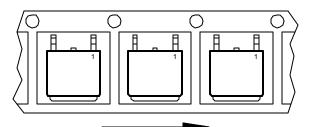

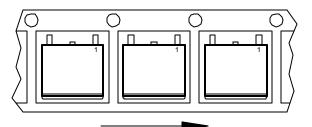

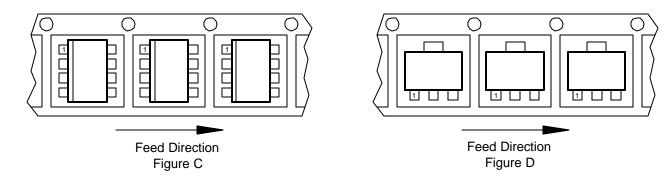

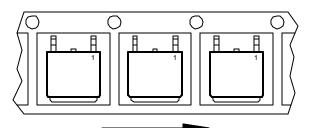

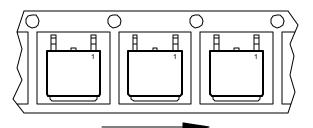

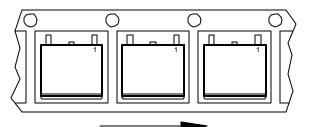

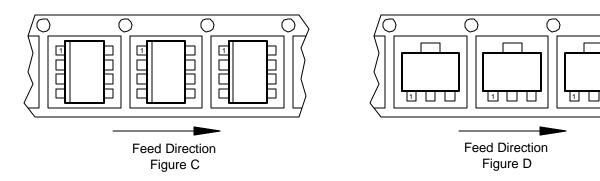

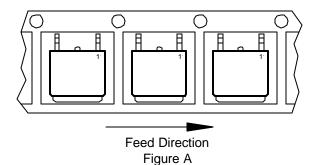

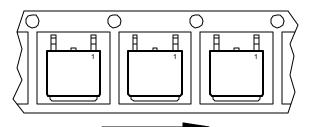

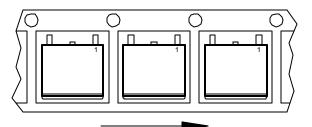

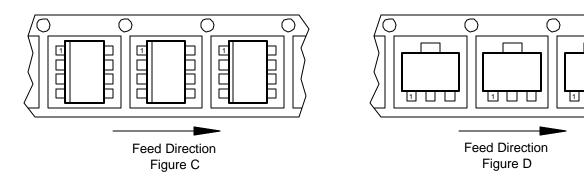

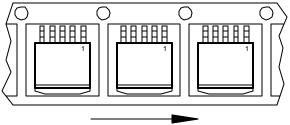

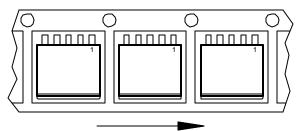

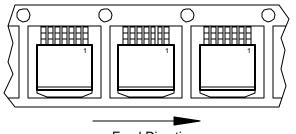

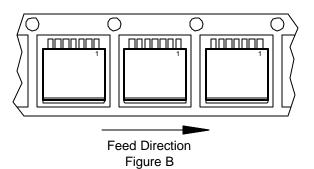

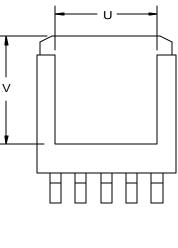

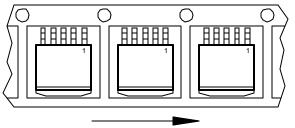

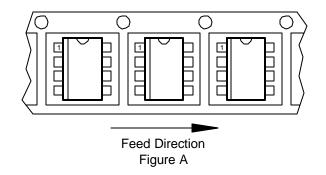

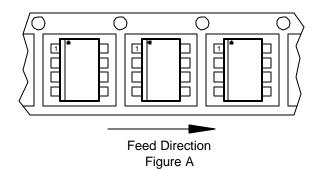

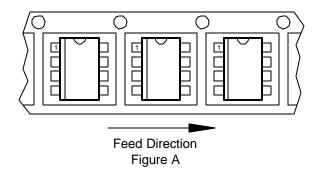

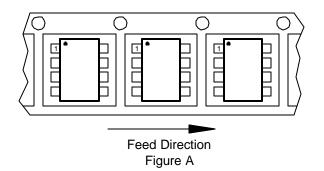

| PKG<br>DESIG | PACKAGE<br>DESCRIPTION | PIN<br>COUNT | PARTS<br>PER TUBE | PARTS<br>PER REEL | T & R<br>Orientation |

|--------------|------------------------|--------------|-------------------|-------------------|----------------------|

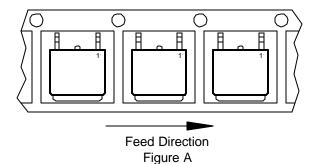

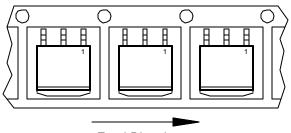

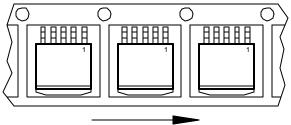

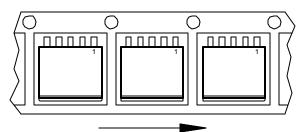

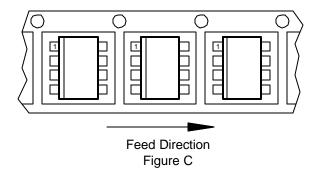

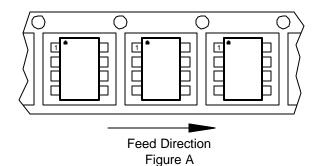

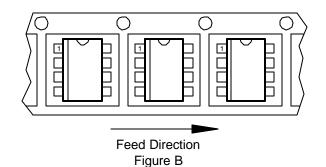

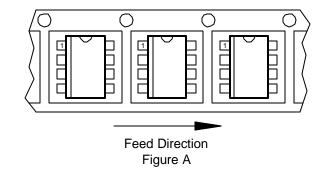

| L3           | SOT-23                 | 3            |                   | 3000              | Fig A                |

| L5           | SOT-23                 | 5            |                   | 3000              | Fig B                |

Feed Directior Figure B

International IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105 TAC Fax: (310) 252-7903 Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 02/01

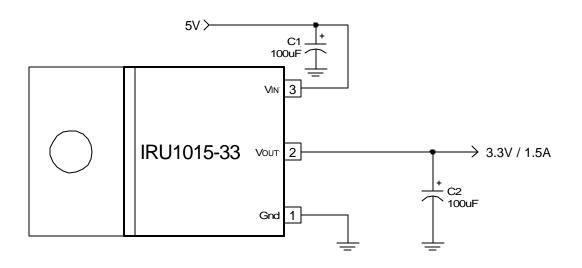

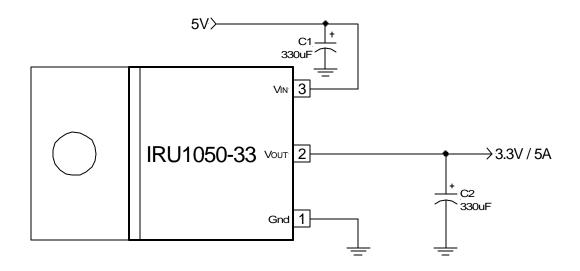

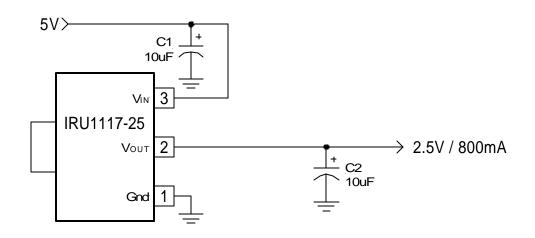

## **FEATURES**

- Guaranteed < 1.3V Dropout at Full Load Current

- Fast Transient Response

- 1% Voltage Reference Initial Accuracy

- Built-In Thermal Shutdown

- Available in SOT-223, D-Pak, Ultra Thin-Pak<sup>™</sup> and 8-Pin SOIC Surface-Mount Packages

## **APPLICATIONS**

- VGA & Sound Card Applications

- Low Voltage High Speed Termination Applications

- Standard 3.3V Chip Set and Logic Applications

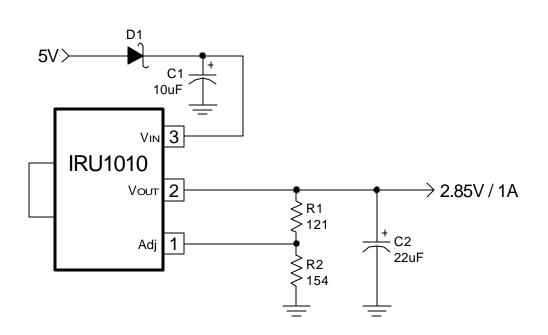

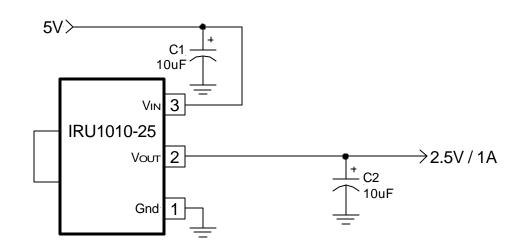

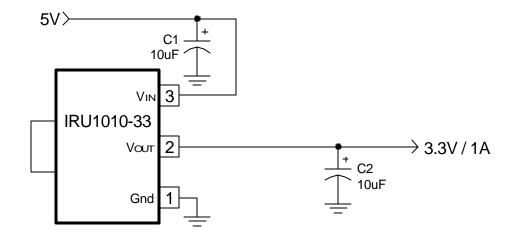

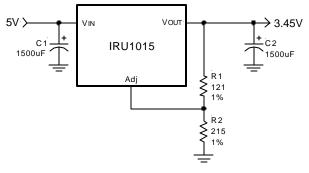

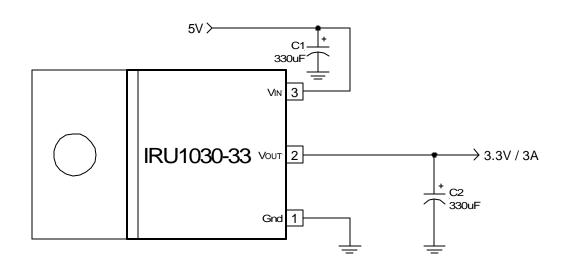

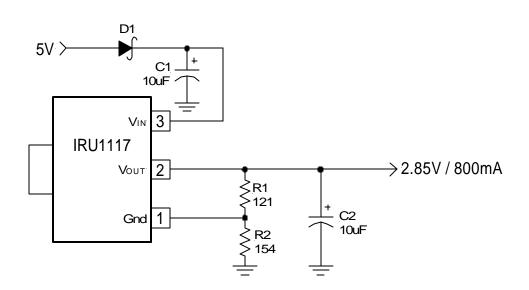

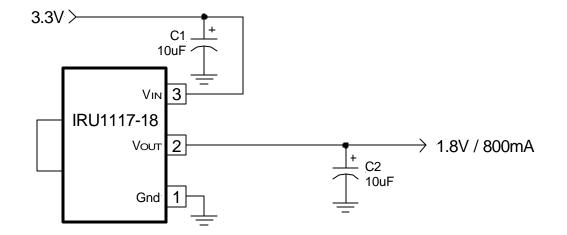

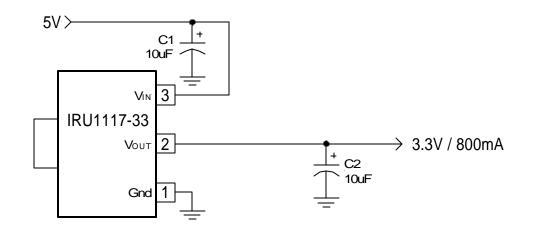

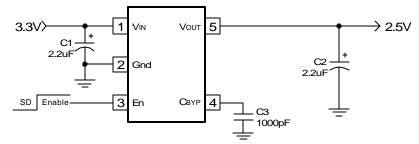

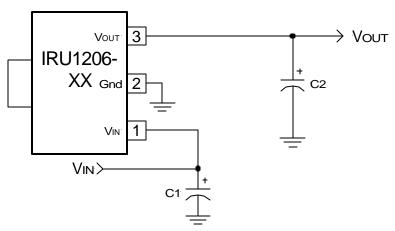

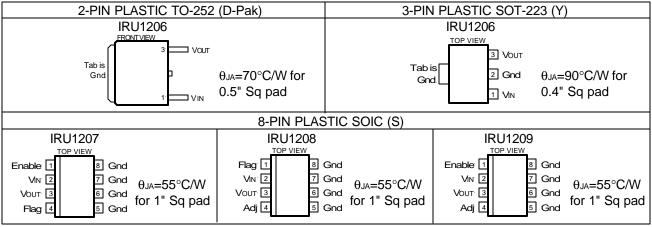

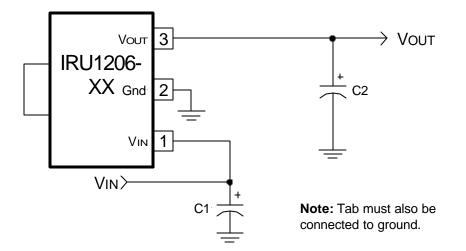

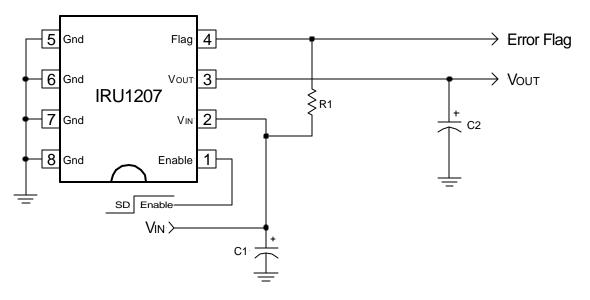

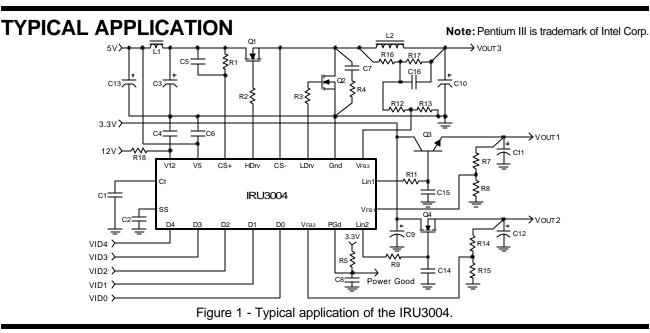

## **TYPICAL APPLICATION**

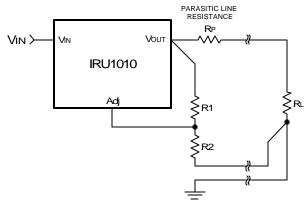

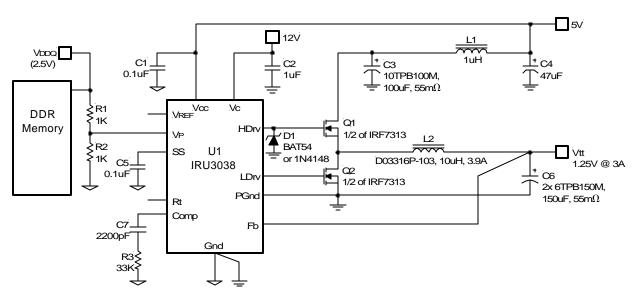

# 1A LOW DROPOUT POSITIVE ADJUSTABLE REGULATOR DESCRIPTION

The IRU1010 is a low dropout, three-terminal adjustable regulator with minimum of 1A output current capability. This product is specifically designed to provide well regulated supply for low voltage IC applications such as high speed bus termination and low current 3.3V logic supply. The IRU1010 is also well suited for other applications such as VGA and sound cards. The IRU1010 is guaranteed to have <1.3V dropout at full load current making it ideal to provide well regulated outputs of 2.5V to 3.6V with 4.75V to 7V input supply.

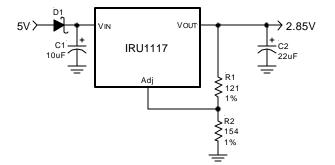

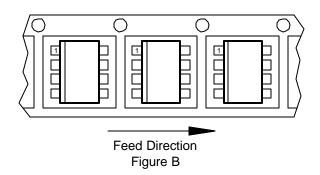

Figure 1 - Typical application of IRU1010 in a 5V to 2.85V SCSI termination regulator.

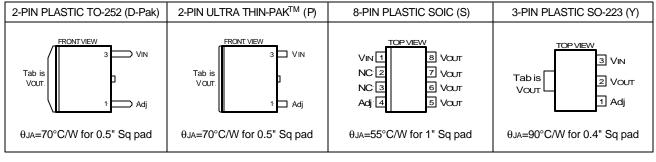

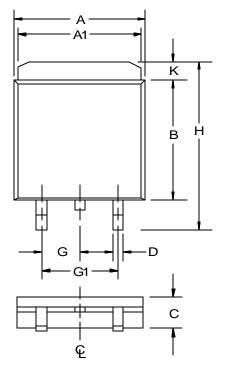

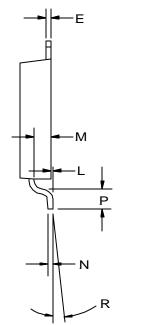

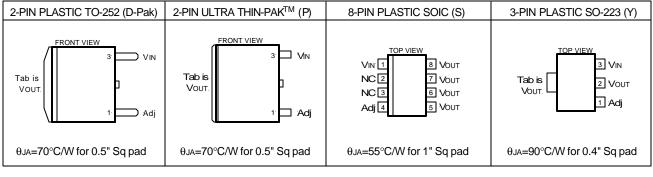

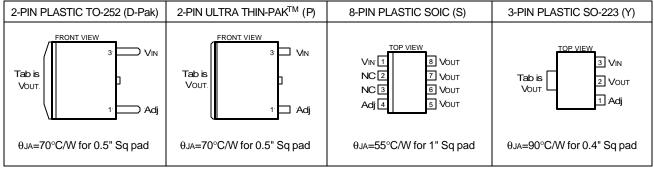

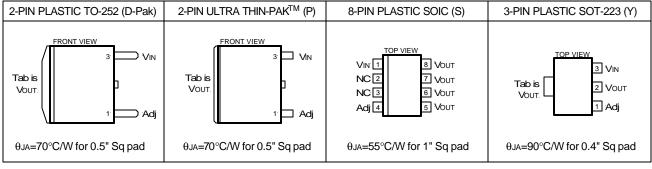

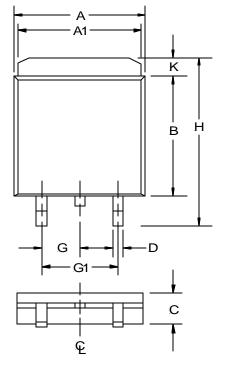

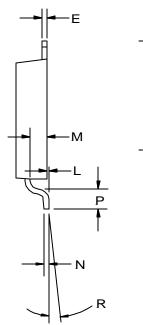

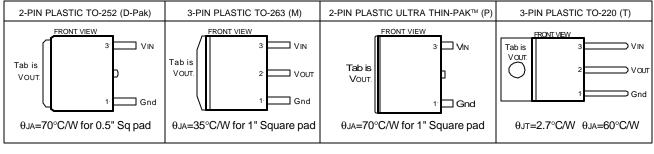

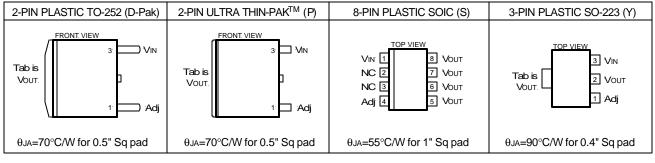

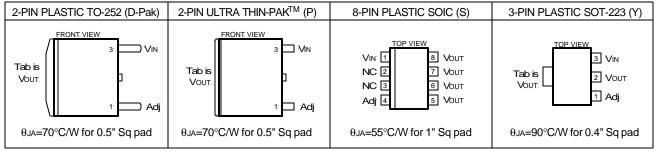

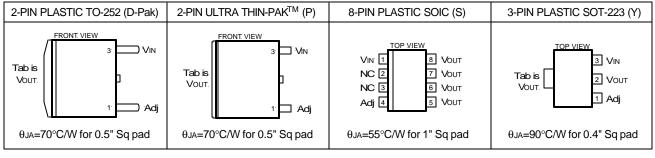

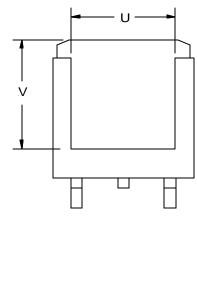

# PACKAGE ORDER INFORMATION

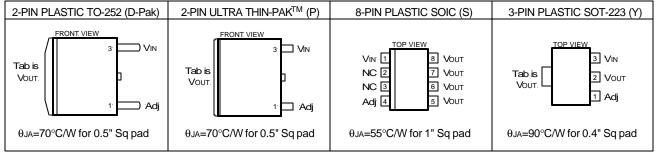

| TJ (°C)  | 2-PIN PLASTIC  | 2-PIN PLASTIC       | 8-PIN PLASTIC | 3-PIN PLASTIC |

|----------|----------------|---------------------|---------------|---------------|

|          | TO-252 (D-Pak) | Ultra Thin-Pak™ (P) | SOIC (S)      | SOT-223 (Y)   |

| 0 To 150 | IRU1010CD      | IRU1010CP           | IRU1010CS     | IRU1010CY     |

# **ABSOLUTE MAXIMUM RATINGS**

| Input Voltage (VIN)                  | 7V                 |

|--------------------------------------|--------------------|

| Power Dissipation                    | Internally Limited |

| Storage Temperature Range            | -65°C To 150°C     |

| Operating Junction Temperature Range | 0°C To 150°C       |

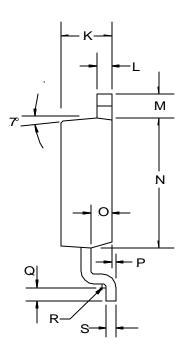

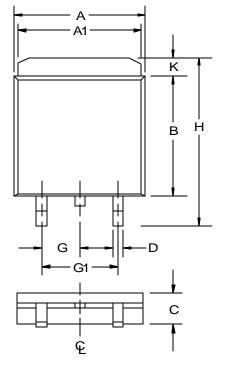

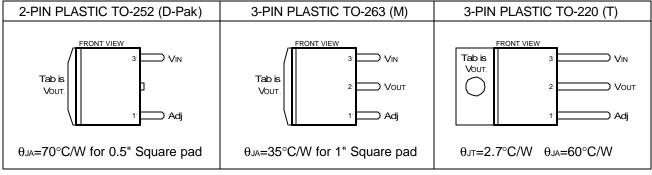

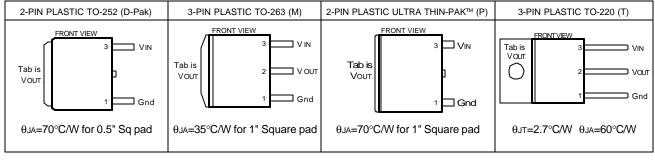

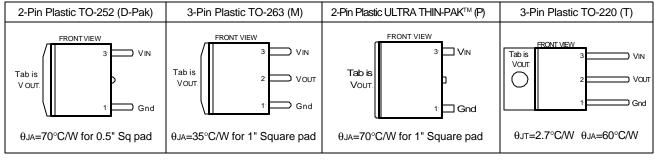

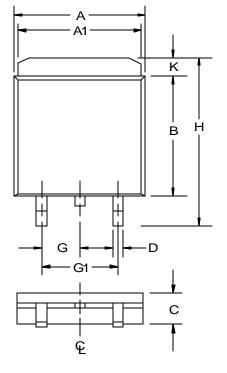

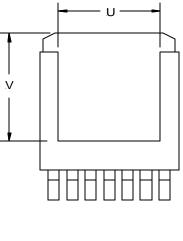

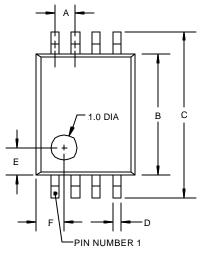

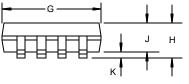

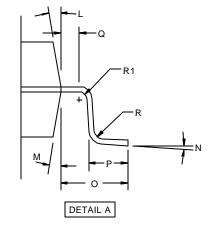

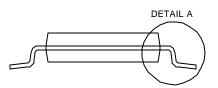

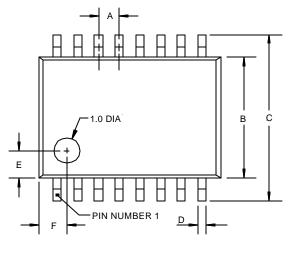

# PACKAGE INFORMATION

# **ELECTRICAL SPECIFICATIONS**

Unless otherwise specified, these specifications apply over  $C_{IN}=1\mu F$ ,  $C_{OUT}=10\mu F$ , and  $T_{J}=0$  to  $150^{\circ}C$ . Typical values refer to  $T_{J}=25^{\circ}C$ .

| PARAMETER                     | SYM  | TEST CONDITION                                                                         | MIN   | TYP   | MAX   | UNITS |

|-------------------------------|------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Reference Voltage             | Vref | Io=10mA, TJ=25°C, (VIN-Vo)=1.5V                                                        | 1.238 | 1.250 | 1.262 | V     |

|                               |      | Io=10mA, (Vı⊳-Vo)=1.5V                                                                 | 1.225 | 1.250 | 1.275 |       |

| Line Regulation               |      | Io=10mA, 1.3V<(Vı⊳-Vo)<7V                                                              |       |       | 0.2   | %     |

| Load Regulation (Note 1)      |      | VIN=3.3V, VADJ=0, 10mA <io<1a< td=""><td></td><td></td><td>0.4</td><td>%</td></io<1a<> |       |       | 0.4   | %     |

| Dropout Voltage (Note 2)      | ΔVo  | Note 2 , Io=1A                                                                         |       | 1.1   | 1.3   | V     |

| Current Limit                 |      | VIN=3.3V, ΔVo=100mV                                                                    | 1.1   |       |       | А     |

| Minimum Load Current (Note 3) |      | VIN=3.3V, VADJ=0V                                                                      |       | 5     | 10    | mA    |

| Thermal Regulation            |      | 30ms Pulse, VIN-Vo=3V, Io=1A                                                           |       | 0.01  | 0.02  | %/W   |

| Ripple Rejection              |      | f=120Hz, Co=25µF Tantalum,                                                             |       |       |       |       |

|                               |      | Io=0.5A, VIN-Vo=3V                                                                     | 60    | 70    |       | dB    |

| Adjust Pin Current            | ADJ  | Io=10mA, Vı⊳-Vo=1.5V, Tյ=25°C,                                                         |       |       |       |       |

|                               |      | Io=10mA, Vı⊳-Vo=1.5V                                                                   |       | 55    | 120   | μA    |

| Adjust Pin Current Change     |      | Io=10mA, Vı⊳-Vo=1.5V, Tյ=25°C                                                          |       | 0.2   | 5     | μA    |

| Temperature Stability         |      | VIN=3.3V, VADJ=0V, IO=10mA                                                             |       | 0.5   |       | %     |

| Long Term Stability           |      | TJ=125°C, 1000Hrs                                                                      |       | 0.3   | 1     | %     |

| RMS Output Noise              |      | T_=25°C, 10Hz <f<10khz< td=""><td></td><td>0.003</td><td></td><td>%Vo</td></f<10khz<>  |       | 0.003 |       | %Vo   |

**Note 1:** Low duty cycle pulse testing with Kelvin connections is required in order to maintain accurate data.

**Note 2:** Dropout voltage is defined as the minimum differential voltage between  $V_{IN}$  and  $V_{OUT}$  required to maintain regulation at  $V_{OUT}$ . It is measured when the output voltage drops 1% below its nominal value.

**Note 3:** Minimum load current is defined as the minimum current required at the output in order for the output voltage to maintain regulation. Typically, the resistor dividers are selected such that it automatically maintains this current.

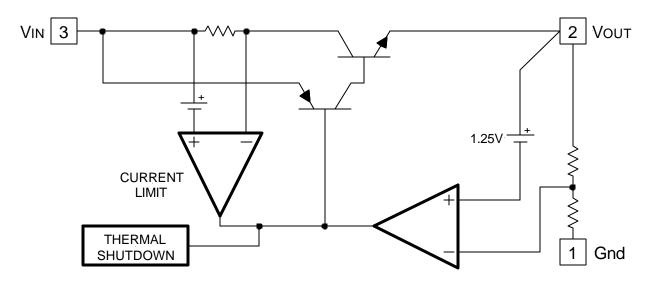

## **PIN DESCRIPTIONS**

| PIN # | PIN SYMBOL | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                               |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Adj        | A resistor divider from this pin to the $V_{OUT}$ pin and ground sets the output voltage.                                                                                                                                                                                                                                     |

| 2     | Vout       | The output of the regulator. A minimum of $10\mu$ F capacitor must be connected from this pin to ground to insure stability.                                                                                                                                                                                                  |

| 3     | Vin        | The input pin of the regulator. Typically a large storage capacitor is connected from this pin to ground to insure that the input voltage does not sag below the minimum dropout voltage during the load transient response. This pin must always be 1.3V higher than $V_{OUT}$ in order for the device to regulate properly. |

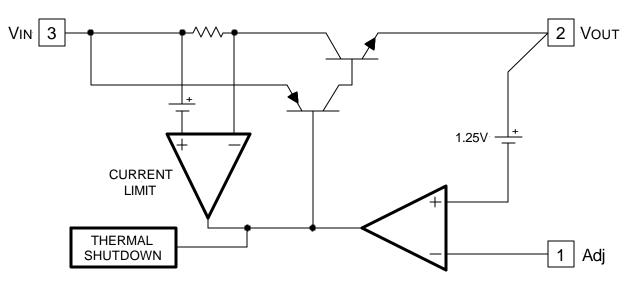

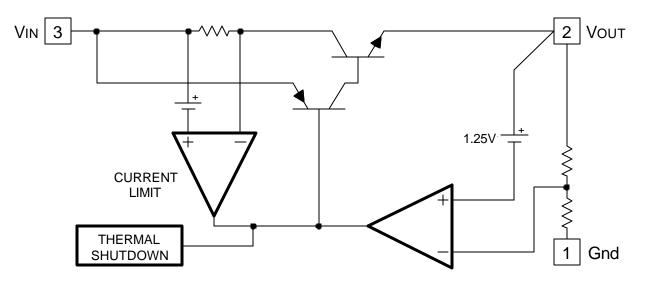

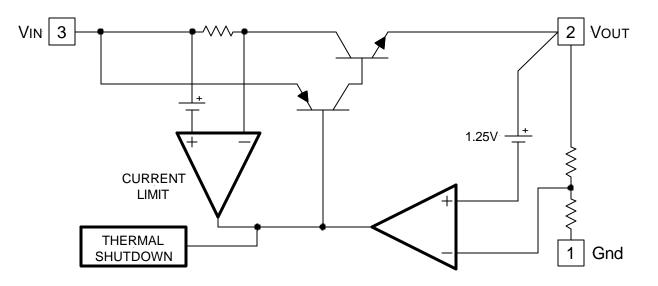

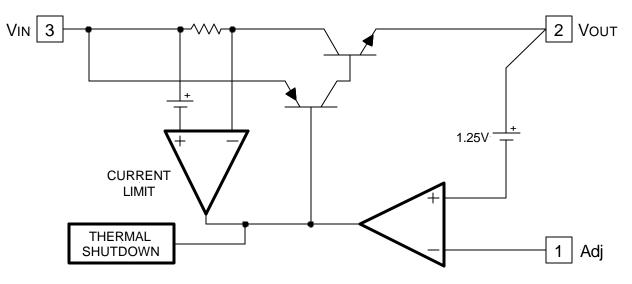

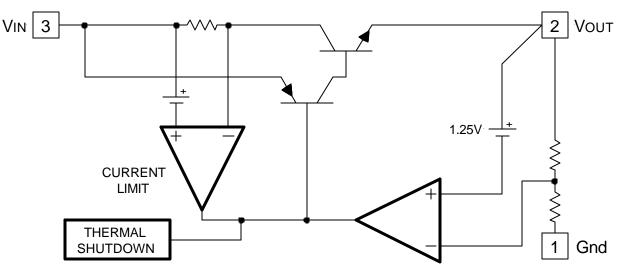

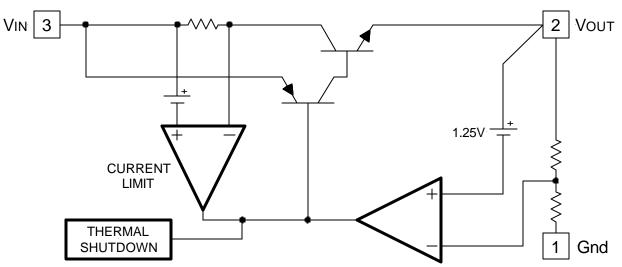

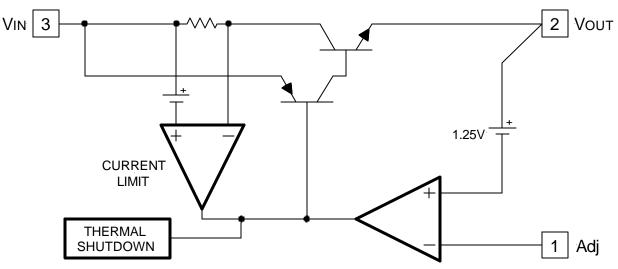

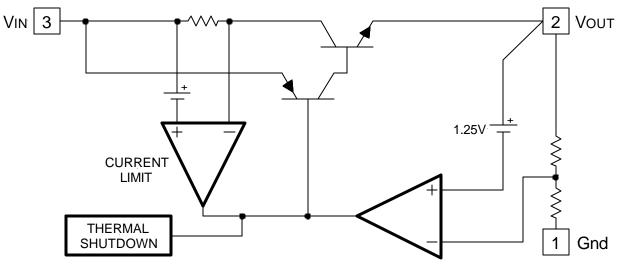

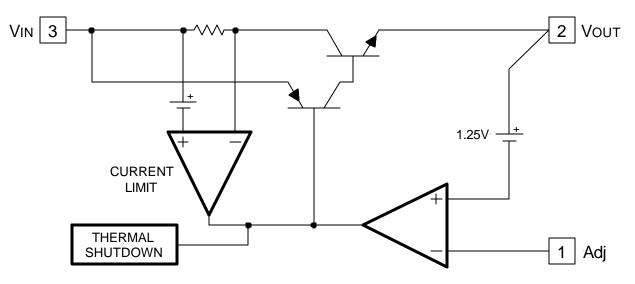

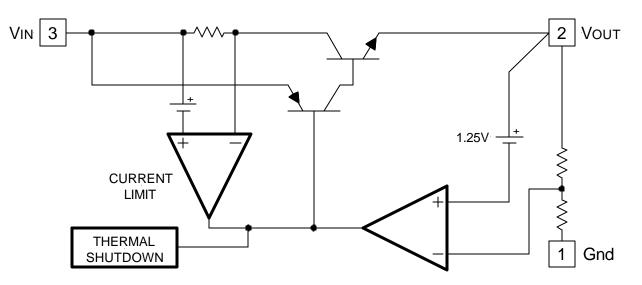

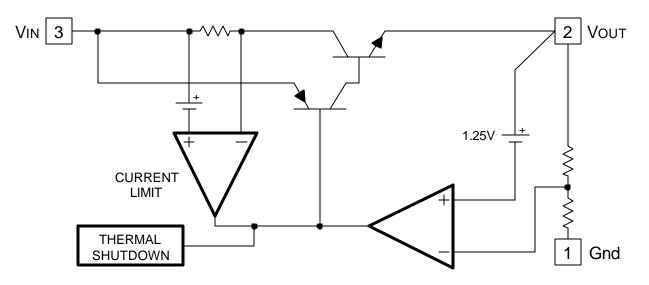

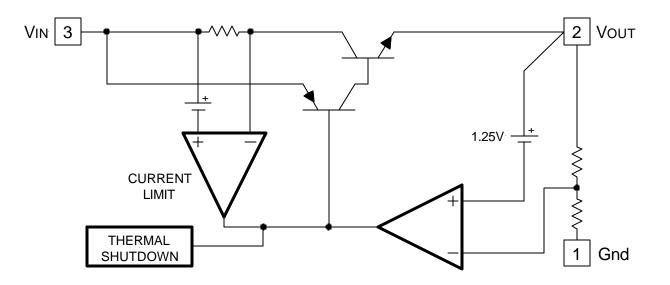

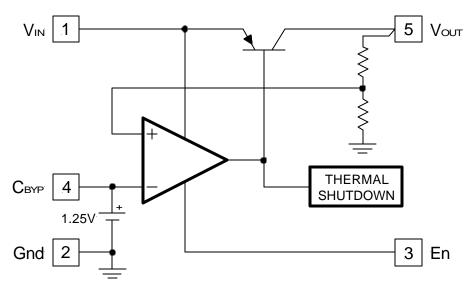

## **BLOCK DIAGRAM**

Figure 2 - Simplified block diagram of the IRU1010.

# **APPLICATION INFORMATION**

#### Introduction

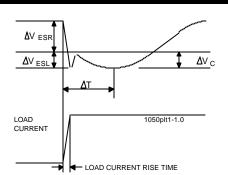

The IRU1010 adjustable Low Dropout (LDO) regulator is a three-terminal device which can easily be programmed with the addition of two external resistors to any voltages within the range of 1.25 to 5.5V. This regulator, unlike the first generation of the three-terminal regulators such as LM117 that required 3V differential between the input and the regulated output, only needs 1.3V differential to maintain output regulation. This is a key requirement for today's low voltage IC applications that typically need 3.3V supply and are often generated from the 5V supply. Other applications such as high speed memory termination need to switch the load current from zero to full load in tens of nanoseconds at their pins, which translates to an approximately 300 to 500ns current step at the regulator. In addition, the output voltage tolerances are sometimes tight and they include the transient response as part of the specification.

The IRU1010 is specifically designed to meet the fast current transient needs as well as providing an accurate initial voltage, reducing the overall system cost with the need for fewer output capacitors.

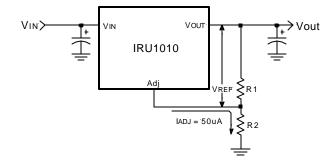

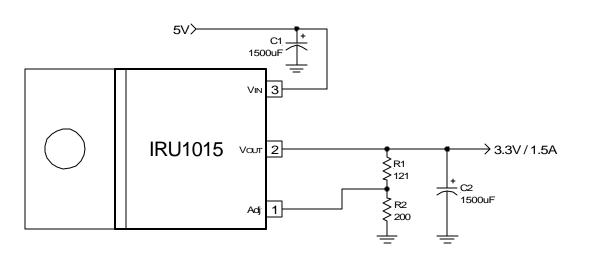

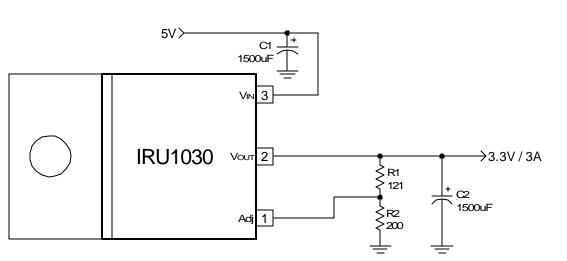

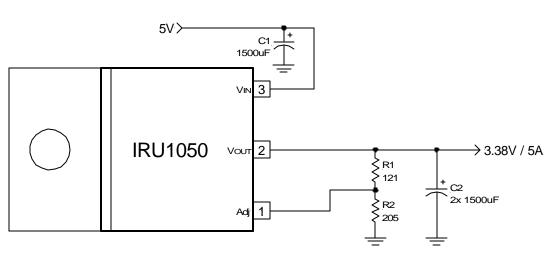

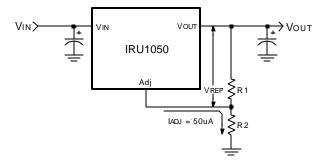

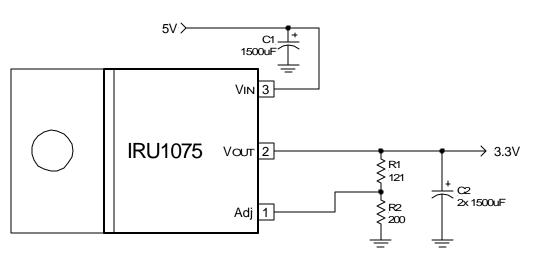

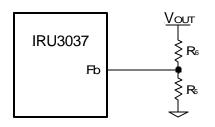

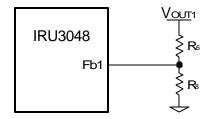

#### **Output Voltage Setting**

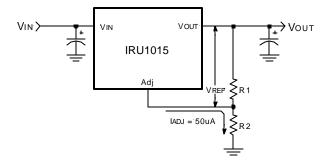

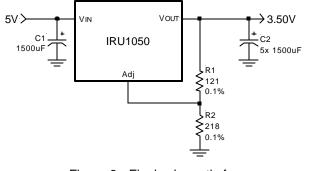

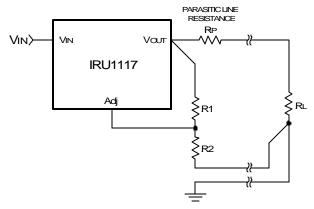

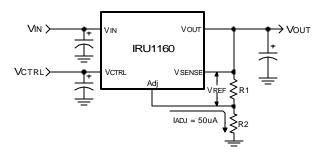

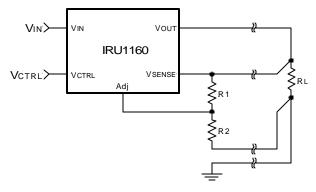

The IRU1010 can be programmed to any voltages in the range of 1.25V to 5.5V with the addition of R1 and R2 external resistors according to the following formula:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R2}{R1}\right) + I_{ADJ} \times R2$$

Where:

$\label{eq:VREF} \begin{array}{l} V_{\text{REF}} = 1.25V \mbox{ Typically} \\ I_{\text{ADJ}} = 50 \mu A \mbox{ Typically} \\ \text{R1 and R2 as shown in Figure 3:} \end{array}$

The IRU1010 keeps a constant 1.25V between the output pin and the adjust pin. By placing a resistor R1 across these two pins a constant current flows through R1, adding to the IADJ current and into the R2 resistor producing a voltage equal to the  $(1.25/R1) \times R2 + I_{ADJ} \times R2$  which will be added to the 1.25V to set the output voltage. This is summarized in the above equation. Since the minimum load current requirement of the IRU1010 is 10mA, R1 is typically selected to be  $121\Omega$  resistor so that it automatically satisfies the minimum current requirement. Notice that since IADJ is typically in the range of 50µA it only adds a small error to the output voltage and should only be considered when a very precise output voltage setting is required. For example, in a typical 3.3V application where R1=121 $\Omega$  and R2=200 $\Omega$  the error due to IADJ is only 0.3% of the nominal set point.

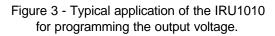

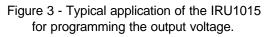

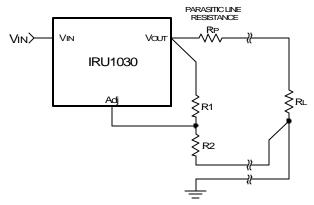

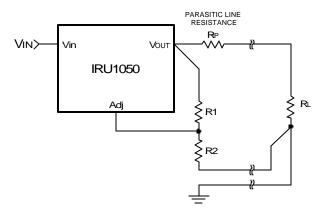

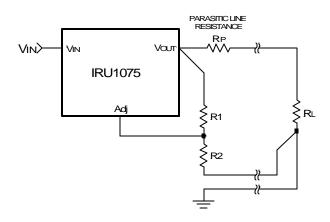

#### Load Regulation

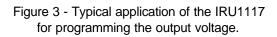

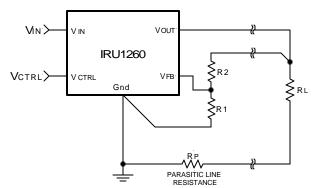

Since the IRU1010 is only a three-terminal device, it is not possible to provide true remote sensing of the output voltage at the load. Figure 4 shows that the best load regulation is achieved when the bottom side of R2 is connected to the load and the top side of R1 resistor is connected directly to the case or the Vout pin of the regulator and not to the load. In fact, if R1 is connected to the load side, the effective resistance between the regulator and the load is gained up by the factor of (1+ R2/R1), or the effective resistance will be  $R_{P(eff)}=R_P \times (1+ R2/R1)$ . It is important to note that for high current applications, this can represent a significant percentage of the overall load regulation and one must keep the path from the regulator to the load as short as possible to minimize this effect.

Figure 4 - Schematic showing connection for best load regulation.

#### Stability

The IRU1010 requires the use of an output capacitor as part of the frequency compensation in order to make the regulator stable. Typical designs for microprocessor applications use standard electrolytic capacitors with a typical ESR in the range of 50 to  $100m\Omega$  and an output capacitance of 500 to  $1000\mu$ F. Fortunately as the capacitance increases, the ESR decreases resulting in a fixed RC time constant. The IRU1010 takes advantage of this phenomena in making the overall regulator loop stable. For most applications a minimum of  $100\mu$ F aluminum electrolytic capacitor such as Sanyo MVGX series, Panasonic FA series as well as the Nichicon PL series insures both stability and good transient response.

#### **Thermal Design**

The IRU1010 incorporates an internal thermal shutdown that protects the device when the junction temperature exceeds the maximum allowable junction temperature. Although this device can operate with junction temperatures in the range of 150°C, it is recommended that the selected heat sink be chosen such that during maximum continuous load operation the junction temperature is kept below this number. The next example for a SCSI terminator application shows the steps in sellecting the proper regulator in a surface-mount package. (See IRU1015 for non-surface-mount packages)

Assuming the following specifications:

$$V_{IN} = 5V$$

$$V_F = 0.5V$$

$$V_{OUT} = 2.85V$$

$$I_{OUT(MAX)} = 0.8A$$

$$T_A = 35^{\circ}C$$

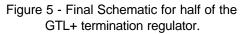

Where:  $V_F$  is the forward voltage drop of the D1 diode as shown in Figure 5.

The steps for selecting the right package with proper board area for heatsinking to keep the junction temperature below 135°C is given as: