# LT1103/LT1105

Offline Switching Regulator

### FEATURES

- ±1% Line and Load Regulation with No Opto-Coupler

- Switch Frequency up to 200kHz

- Internal 2A Switch and Current Sense (LT1103)

- Internal 1A Totem Pole Driver (LT1105)

- Start-Up Mode Draws Only 200µA

- Fully Protected Against Overloads

- Overvoltage Lockout of Main Supply

- Protected Against Underdrive or Overdrive to FET

- Operates in Continuous or Discontinuous Mode

- Ideal for Flyback and Forward Topologies

- Isolated Flyback Mode Has Fully Floating Outputs

# APPLICATIONS

- Up to 250W Isolated Mains Converter

- Up to 50W Isolated Telecom Converter

- Fully Isolated Multiple Outputs

- Distributed Power Conversion Networks

### DESCRIPTION

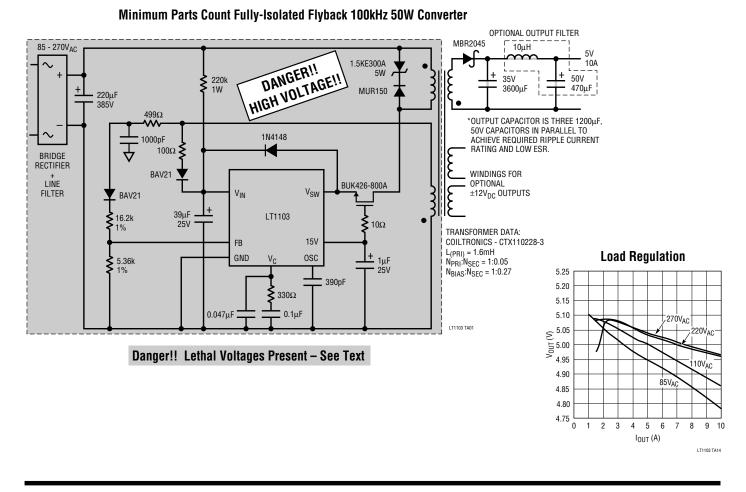

The LT1103 Offline Switching Regulator is designed for high input voltage applications using an external FET switch whose source is driven by the open collector output of the LT1103. The LT1103 is optimized for 15W–100W applications. For higher power applications or additional switch current flexibility, the LT1105 is available and its totem pole output drives the gate of an external FET. Unique design of the LT1103/LT1105 eliminates the need for an opto-coupler while still providing ±1% load and line regulation in a magnetic flux-sensed converter. This significantly simplifies the design of offline power supplies and reduces the number of components which must cross the isolation barrier to one, the transformer.

The LT1103/LT1105 current mode switching techniques are well suited to transformer-isolated flyback and forward topologies while providing ease of frequency compensation with a minimum of external components. Low external part count for a typical application combines with

T and LTC are registered trademarks and LT is a trademark of Linear Technology Corporation.

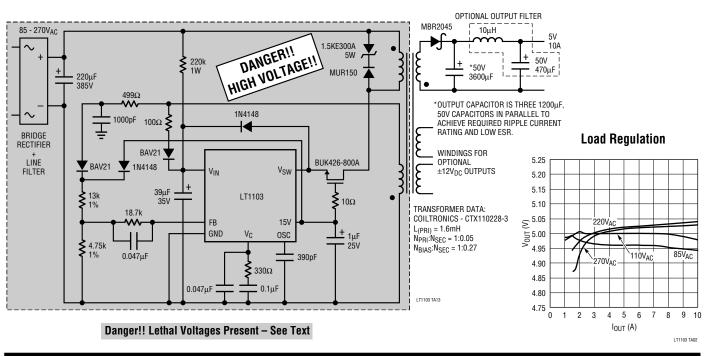

# TYPICAL APPLICATION

Fully-Isolated Flyback 100kHz 50W Converter with Load Regulation Compensation

TECHNOLOGY

# DESCRIPTION

a 200kHz maximum switching frequency to achieve high power density. Performance at switching frequencies above 100kHz may be degraded due to internal timing constraints associated with fully-isolated flyback mode.

Included are the oscillator, control, and protection circuitry such as current limit and overvoltage lockout. Switch frequency and maximum duty cycle are adjustable. Bootstrap circuitry draws 200µA for startup of isolated topologies. A 5V reference as well as a 15V gate bias are available to power external primary-side circuitry. No external current sense resistor is necessary with LT1103 because it is integrated with the high current switch. The LT1105 brings out the input to the current limit amplifier and requires the use of an external sense resistor.

The LT1103/LT1105 have unique features not found on other offline switching regulators. Adaptive anti-sat switch drive allows wide-ranging load currents while maintaining high efficiency. The external FET is protected from insufficient or excessive gate drive voltage with a drive detection circuit. An externally activated shutdown mode reduces total supply current to less than 200µA, typical for standby operation. Fully isolated and regulated outputs can be generated in the optional isolated flyback mode without the need for opto-couplers or other isolated feedback paths.

### WARNING!

DANGEROUS AND LETHAL POTENTIALS ARE PRESENT IN OFFLINE CIRCUITS!

**BEFORE PROCEEDING ANY FURTHER, THE READER IS WARNED THAT CAUTION MUST** BE USED IN THE CONSTRUCTION. TESTING AND USE OF OFFLINE CIRCUITS. HIGH **VOLTAGE. ACLINE-CONNECTED POTENTIALS** ARE PRESENT IN THESE CIRCUITS. EXTREME CAUTION MUST BE USED IN WORKING WITH AND MAKING CONNECTIONS TO THESE CIRCUITS. REPEAT: OFFLINE CIRCUITS **CONTAIN DANGEROUS, AC LINE-CONNECTED** HIGH VOLTAGE POTENTIALS. USE CAUTION. ALL TESTING PERFORMED ON AN OFFLINE **CIRCUIT MUST BE DONE WITH AN ISOLATION** TRANSFORMER CONNECTED BETWEEN THE OFFLINE CIRCUIT'S INPUT AND THE AC LINE. **USERS AND CONSTRUCTORS OF OFFLINE CIRCUITS MUST OBSERVE THIS PRECAUTION** WHEN CONNECTING TEST EQUIPMENT TO THE CIRCUIT TO AVOID ELECTRIC SHOCK. **REPEAT: AN ISOLATION TRANSFORMER MUST BE CONNECTED BETWEEN THE CIRCUIT**

INPUT AND THE AC LINE IF ANY TEST EQUIPMENT IS TO BE CONNECTED.

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub>                                | 30V   |

|------------------------------------------------|-------|

| V <sub>SW</sub> Output Voltage (LT1103)        |       |

| V <sub>SW</sub> Output Current (200ns)(LT1105) | ±1.5A |

| V <sub>C</sub> , FB, OSC, SS                   | 6V    |

| I <sub>LIM</sub> (LT1105)                      |       |

| OVLO Input Current                             | 1mA   |

| Lead Temperature (Soldering, 10 sec.)          | 300°C |

| Maximum Operating Ambient Temperature Range  |  |  |  |  |  |

|----------------------------------------------|--|--|--|--|--|

| LT1103C 0°C to 70°C                          |  |  |  |  |  |

| LT1105C 0°C to 70°C                          |  |  |  |  |  |

| Maximum Operating Junction Temperature Range |  |  |  |  |  |

| LT1103C0°C to +100°C                         |  |  |  |  |  |

| LT1105C 0°C to +100°C                        |  |  |  |  |  |

| Storage Temperature Range65°C to +150°C      |  |  |  |  |  |

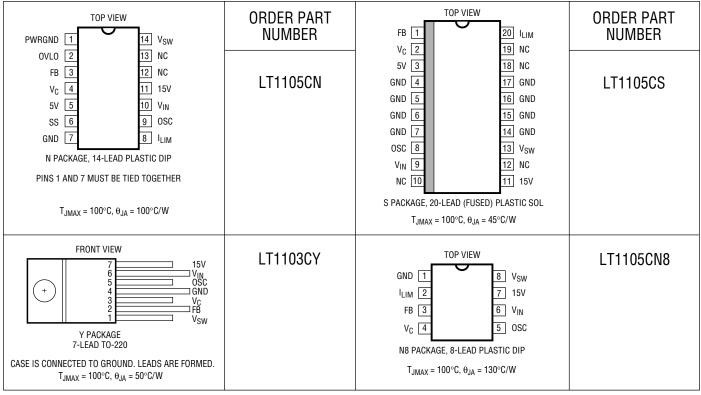

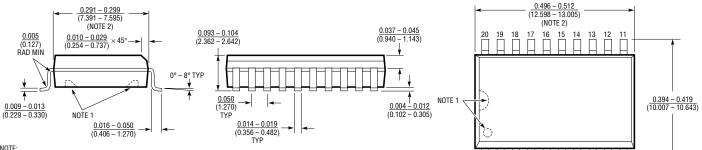

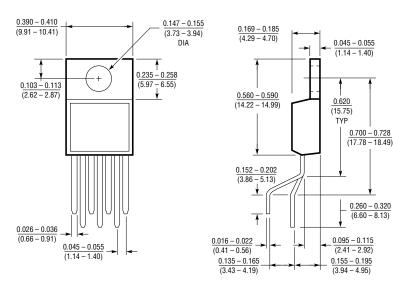

## PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 20V,  $V_C$  = 0.85V, OVLO = 0V,  $V_{SW}$  Open,  $T_A$  = 25°C, unless otherwise noted.

| SYMBOL             | PARAMETER                              | CONDITIONS                                                                                                                                                                  |   | MIN      | ТҮР      | MAX      | UNITS              |

|--------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|----------|----------|--------------------|

| IQ                 | Supply Current                         | $8V < V_{IN} < 30V$ , After device has started                                                                                                                              | • | 10       | 20       | 30       | mA                 |

| I <sub>START</sub> | Start-Up Current                       | V <sub>IN</sub> < V <sub>IN</sub> Start Threshold                                                                                                                           | • |          | 200      | 400      | μA                 |

|                    | V <sub>IN</sub> Start Threshold        |                                                                                                                                                                             | • | 14.5     | 16.0     | 17.5     | V                  |

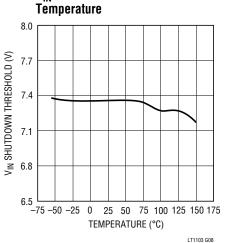

|                    | V <sub>IN</sub> Shutdown Threshold     | Note: Switching stops when $V_{SW}$ < 10V (LT1103) Note: Switching stops when $V_{GATE}$ < 10V (LT1105)                                                                     | • | 5.0      | 7.0      | 8.0      | V                  |

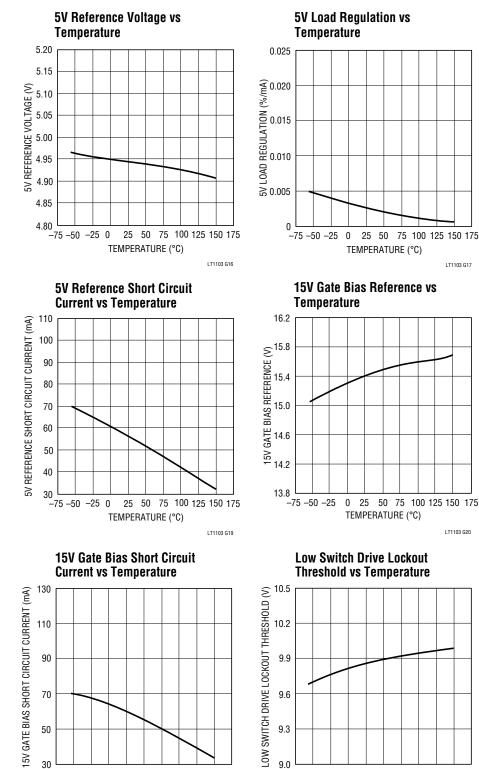

| V <sub>REF</sub>   | 5V Reference Voltage                   |                                                                                                                                                                             | • | 4.80     | 4.95     | 5.20     | V                  |

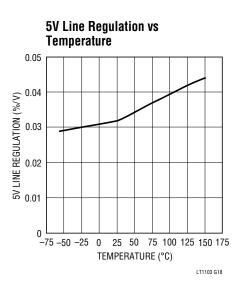

|                    | V <sub>REF</sub> Line Regulation       | 10V < V <sub>IN</sub> < 30V                                                                                                                                                 | • |          | 0.025    | 0.075    | %/V                |

|                    | V <sub>REF</sub> Load Regulation       | $0mA < I_L < 20mA$                                                                                                                                                          | • |          | 0.025    | 0.05     | %/mA               |

|                    | V <sub>REF</sub> Short Circuit Current |                                                                                                                                                                             | • | 25       | 60       | 110      | mA                 |

| V <sub>GATE</sub>  | 15V Gate Bias Reference                | $17 < V_{IN} < 30V, 0mA < I_L < 30mA$                                                                                                                                       | • | 13.8     | 15.0     | 16.2     | V                  |

|                    | 15V Dropout Voltage                    | V <sub>IN</sub> = 15V, I <sub>L</sub> = 30mA                                                                                                                                | • |          | 2.0      | 2.5      | V                  |

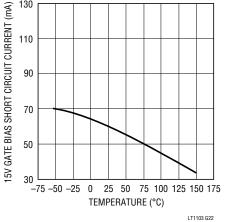

|                    | 15V Short Circuit Current              |                                                                                                                                                                             | • | 30       | 70       | 130      | mA                 |

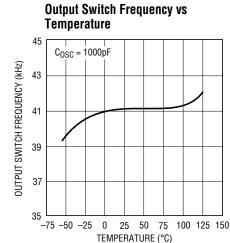

| SF                 | Oscillator Scaling Factor              | $\label{eq:FB} \begin{array}{l} FB = 4V,  V_{C} = Open,  Measured   at  V_{SW},  I_{SW} = 25mA, \\ OVLO = 5V,  F_{OSC} = SF/C_{OSC},  40kHz < F_{OSC} < 200kHz \end{array}$ | • | 36<br>32 | 40<br>40 | 44<br>48 | Hz • μF<br>Hz • μF |

|                    | Oscillator Valley Voltage              |                                                                                                                                                                             |   |          | 2.0      |          | V                  |

|                    | Oscillator Peak Voltage                |                                                                                                                                                                             |   |          | 4.5      |          | V                  |

### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 20V,  $V_C$  = 0.85V, OVLO = 0V,  $V_{SW}$  Open,  $T_A$  = 25°C, unless otherwise noted.

| SYMBOL                                        | PARAMETER                                                                              | CONDITONS                                                                                                                                                                                                                                                                                         |   | MIN            | ТҮР          | MAX            | UNIT           |

|-----------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|--------------|----------------|----------------|

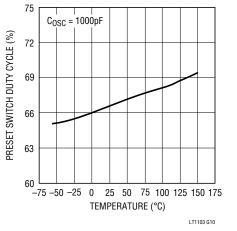

| DC                                            | Preset Max. Switch Duty Cycle<br>(LT1103)<br>Preset Max. Switch Duty Cycle<br>(LT1105) | $\label{eq:FB} \begin{array}{l} FB = 4V,  V_{C} = Open,  F_{OSC} = 40kHz,  I_{SW} = 25mA, \\ Note:  Maximum  Duty  Cycle  can  be  altered  at  OSC  pin \\ FB = 4V,  V_{C} = Open,  F_{OSC} = 40kHz,  I_{SW} = 25mA, \\ Note:  Maximum  Duty  Cycle  can  be  altered  at  OSC  pin \end{array}$ | • | 58<br>56       | 65<br>63     | 72<br>70       | %              |

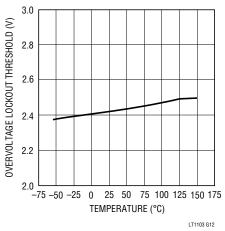

|                                               | OVLO Threshold                                                                         | Overvoltage Lockout Threshold at which switching is inhibited                                                                                                                                                                                                                                     | • | 2.3            | 2.5          | 2.7            | V              |

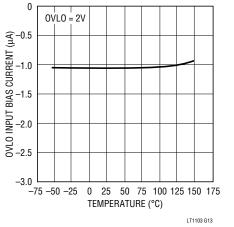

|                                               | OVLO Input Bias Current                                                                | OVLO = 2V, Measured out of pin (Note 1)                                                                                                                                                                                                                                                           | • |                | 1.0          | 3.0            | μA             |

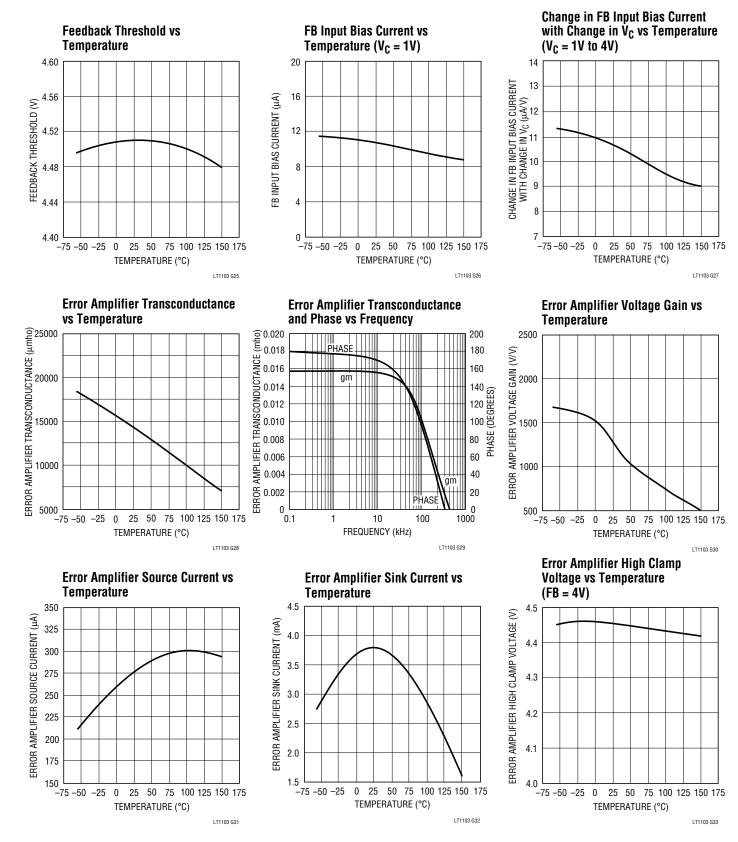

| V <sub>FB</sub>                               | FB Threshold Voltage                                                                   | I(V <sub>C</sub> ) = 0mA                                                                                                                                                                                                                                                                          |   | 4.425<br>4.400 | 4.50<br>4.50 | 4.575<br>4.600 | V<br>V         |

|                                               | FB Input Bias Current                                                                  | FB = V <sub>FB</sub> (Note 2)                                                                                                                                                                                                                                                                     | • | 5              | 10           | 20             | μA             |

|                                               | Change in FB Input<br>Bias Current with Change in V <sub>C</sub>                       | $FB = V_{FB}, V_C = 1V \text{ to } 4V \text{ (Note 2)}$                                                                                                                                                                                                                                           | • | 8<br>7         | 11<br>11     | 13<br>14       | μΑ/ V<br>μΑ/ V |

|                                               | FB Threshold Line Regulation                                                           | 10V < V <sub>IN</sub> < 30V                                                                                                                                                                                                                                                                       | • |                | 0.025        | 0.05           | %/V            |

| gm                                            | Error Amp Transconductance                                                             | $\Delta I(V_{C}) = \pm 50 \mu A$                                                                                                                                                                                                                                                                  | • | 9k<br>6k       | 12k<br>12k   | 17.5k<br>20.0k | µmho<br>µmho   |

| A <sub>V</sub>                                | Error Amp Voltage Gain                                                                 | $1V < V_{C} < 3V$                                                                                                                                                                                                                                                                                 | • | 500            | 1250         |                | V/ V           |

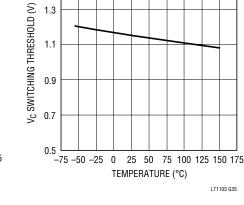

|                                               | V <sub>C</sub> Switching Threshold                                                     | Switch Duty Cycle = 0%                                                                                                                                                                                                                                                                            | • | 0.85           | 1.25         | 1.4            | V              |

|                                               | Shutdown Threshold Voltage                                                             |                                                                                                                                                                                                                                                                                                   | • | 50             | 150          | 250            | mV             |

|                                               | Error Amp Source Current                                                               |                                                                                                                                                                                                                                                                                                   | • | 150            | 275          |                | μA             |

|                                               | Error Amp Sink Current                                                                 |                                                                                                                                                                                                                                                                                                   | • | 1.5            | 3            | 4.5            | mA             |

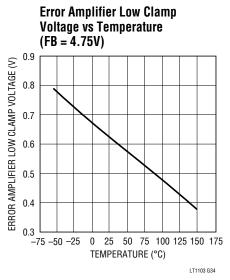

|                                               | Error Amp Clamp Voltage                                                                | FB = 4.75V<br>FB = 4.0V                                                                                                                                                                                                                                                                           | • | 0.3<br>4.2     | 0.7<br>4.4   | 0.9<br>4.6     | V<br>V         |

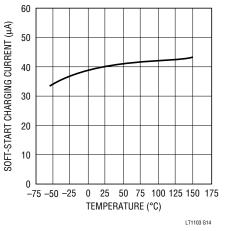

|                                               | Soft-Start Charging Current                                                            | SS = 0V                                                                                                                                                                                                                                                                                           | • | 25             | 40           | 60             | μA             |

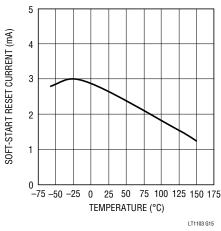

|                                               | Soft-Start Reset Current                                                               | V <sub>IN</sub> = 6V, SS = 0.3V                                                                                                                                                                                                                                                                   | • | 1              | 2            |                | mA             |

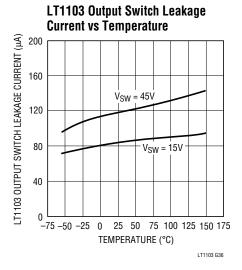

|                                               | Output Switch Leakage<br>(LT1103)                                                      | V <sub>SW</sub> = 45V<br>V <sub>SW</sub> = 15V                                                                                                                                                                                                                                                    | • |                |              | 500<br>200     | μΑ<br>μΑ       |

| BV                                            | Switch Breakdown Voltage<br>(LT1103)                                                   | I <sub>SW</sub> = 5mA                                                                                                                                                                                                                                                                             | • | 50             | 70           |                | V              |

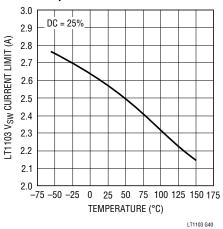

|                                               | V <sub>SW</sub> Current Limit (LT1103)                                                 | Duty Cycle = 25% (Note 3)                                                                                                                                                                                                                                                                         | • | 2.0            | 2.5          | 3.0            | A              |

|                                               | Output Switch ON<br>Resistance (LT1103)                                                |                                                                                                                                                                                                                                                                                                   | • |                | 0.4          | 0.75           | Ω              |

| $\frac{\Delta I_{\rm IN}}{\Delta I_{\rm SW}}$ | I <sub>Q</sub> Increase During Switch ON Time<br>(LT1103)                              | I <sub>SW</sub> = 0.5A to 1.5A                                                                                                                                                                                                                                                                    | • |                | 30           | 50             | mA/A           |

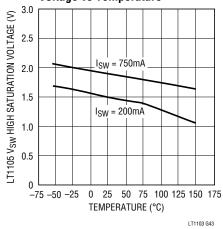

|                                               | Switch Output High Level<br>(LT1105)                                                   | I <sub>SW</sub> =200mA, V <sub>GATE</sub> = 15V<br>I <sub>SW</sub> = 750mA, V <sub>GATE</sub> = 15V                                                                                                                                                                                               |   | 13.0<br>12.5   | 13.5<br>13.2 |                | V<br>V         |

|                                               | Switch Output Low Level<br>(LT1105)                                                    | I <sub>SW</sub> = 200mA<br>I <sub>SW</sub> = 750mA                                                                                                                                                                                                                                                | • |                | 0.25<br>0.75 | 0.50<br>1.50   | V<br>V         |

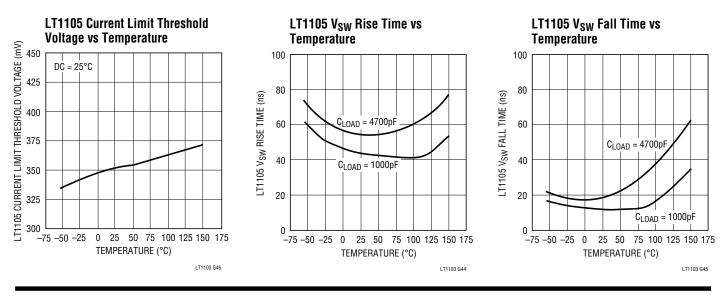

|                                               | Rise Time (LT1105)                                                                     | CL = 1000pF                                                                                                                                                                                                                                                                                       |   |                | 50           |                | ns             |

|                                               | Fall Time (LT1105)                                                                     | CL = 1000pF                                                                                                                                                                                                                                                                                       |   |                | 20           |                | ns             |

## **ELECTRICAL CHARACTERISTICS**

| SYMBOL | PARAMETER CONDITONS                         |                                                                                      |   | MIN  | ТҮР  | MAX  | UNIT |

|--------|---------------------------------------------|--------------------------------------------------------------------------------------|---|------|------|------|------|

|        | I <sub>LIM</sub> Threshold Voltage (LT1105) | Duty Cycle = 25% (Note 4)                                                            | • | 300  | 375  | 450  | mV   |

|        | Low Switch Drive Lockout<br>Threshold       | Measured at V <sub>SW</sub> (LT1103)<br>Measured at 15V Gate Bias Reference (LT1105) | • | 9.0  | 9.5  | 10.5 | V    |

|        | High Switch Drive Lockout<br>Threshold      | Measured at V <sub>SW</sub> (LT1103)<br>Measured at 15V Gate Bias Reference (LT1105) | • | 17.0 | 18.5 | 20.0 | V    |

$V_{IN}$  = 20V,  $V_C$  = 0.85V, 0VLO = 0V,  $V_{SW}$  Open,  $T_A$  = 25°C, unless otherwise noted.

The  ${ullet}$  denotes specifications which apply over the full operating temperature range.

**Note 1:** The OVLO pin is clamped with a 5.5V Zener and can sink a maximum input current of 1mA.

**Note 2:** FB input bias current changes as a function of the V<sub>C</sub> pin voltage. Rate of change of FB input bias current is  $11\mu$ A/V of change on V<sub>C</sub>. By including a resistor in series with the FB pin, load regulation can be set to zero.

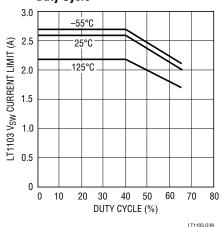

**Note 3:** Current limit on V<sub>SW</sub> is constant for DC < 35% and decreases for DC > 35% due to internal slope compensation circuity. The LT1103 switch current limit is given by I<sub>LIM</sub> = 1.76 (1.536 – DC) above 35% duty cycle. **Note 4:** The current limit threshold voltage is constant for DC < 35% and decreases for DC > 35% due to internal slope compensation circuitry. The LT1105 switch current limit threshold voltage is given by V<sub>LIM</sub> = 0.225 (1.7 – DC) above 35% duty cycle.

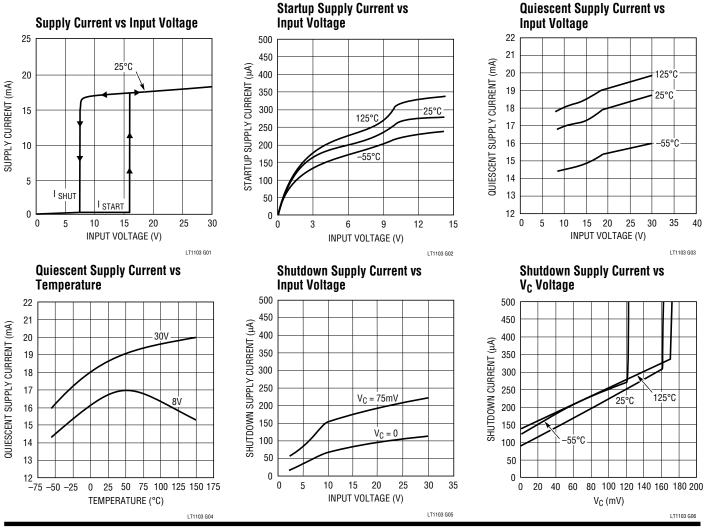

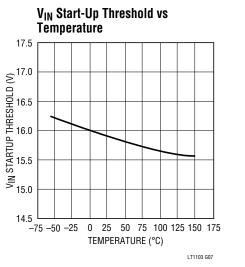

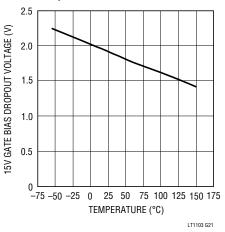

## **TYPICAL PERFORMANCE CHARACTERISTICS**

VIN Shutdown Threshold vs

LT1103 G09

Preset Switch Maximum Duty Cycle vs Temperature

OVLO Input Bias Current vs Temperature

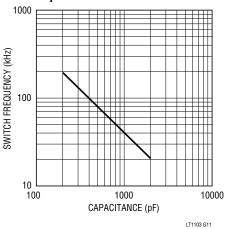

Switch Oscillator Frequency vs Capacitance

Soft-Start Charging Current vs Temperature

Overvoltage Lockout Threshold vs Temperature

Soft-Start Reset Current vs Temperature

, -75 -50 -25

0

25 50 75 100 125 150 175

LT1103 G23

TEMPERATURE (°C)

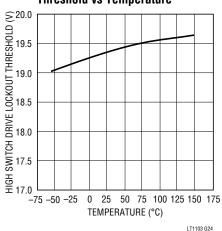

**15V Gate Bias Dropout Voltage vs** Temperature

**High Switch Drive Lockout** Threshold vs Temperature

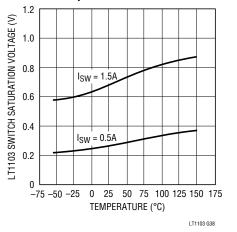

LT1103 Switch Saturation Voltage vs Temperature

LT1103 Driver Current vs Temperature 50 LT1103 DRIVER CURRENT (mA/A) 40 30 20 10 0 , -75 -50 -25 0 25 50 75 100 125 150 175 TEMPERATURE (°C) LT1103 G41

LT1103 V<sub>SW</sub> Current Limit vs **Duty Cycle**

V<sub>C</sub> Switching Threshold Voltage

vs Temperature

1.5

1.3

1.1

LT1105 V<sub>SW</sub> Low Saturation

$I_{SW} = 750 \text{mA}$

I<sub>SW</sub> = 200mA

100 125 150 175

LT1103 G42

50

TEMPERATURE (°C)

75

25

0

Voltage vs Temperature

3.0

2.5

2.0

1.5

1.0

0.5

0

-75 -50 -25

LT1105 V<sub>SW</sub> LOW SATURATION VOLTAGE (V)

LT1103 V<sub>SW</sub> Current Limit vs Temperature

LT1105 V<sub>SW</sub> High Saturation Voltage vs Temperature

# PIN FUNCTIONS

### LT1103

**FB:** The Feedback pin is the inverting input to the sampling error amplifier. The noninverting input is tied to a 4.5V reference. The FB pin is used for output voltage sensing. The input bias current is a function of the control pin  $V_C$  voltage and can be used for load regulation compensation by including a resistor in series with the FB pin. The sampling error amplifier has a typical gm of 0.012 mhos and the output of the sampling error amplifier has asymmetrical slew rate to reduce overshoot during startup conditions or following the release of an output overload.

$V_C$ : The V<sub>C</sub> control pin is used for frequency compensation, current limiting and shutdown. It is the high impedance output of the sampling error amplifier and the input of the current limit comparator.

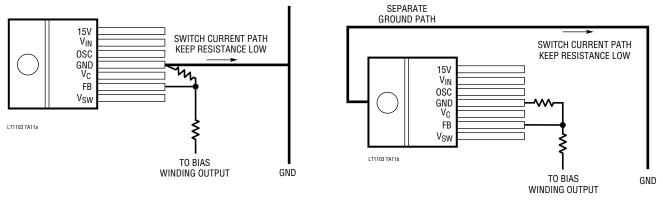

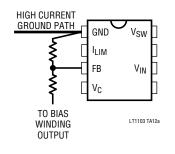

**GND:** The Ground pin acts as both the negative sense point for the internal sampling error amplifier feedback signal and as the high current path for the 2A switch. Also, the case of the 7-lead TO-220 is connected to ground. Proper connections to ground for signal paths and high current paths must be made in order to insure good load regulation.

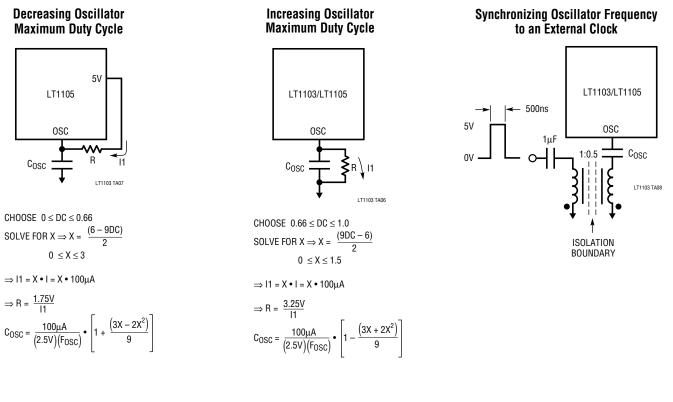

**OSC:** The Oscillator pin sets the operating frequency of the regulator with one external capacitor to ground. Maximum

duty cycle can also be adjusted by using an external resistor to alter the charge/discharge ratio.

$V_{IN}$ : The Input Supply pin is designed to operate with voltages of 12V to 30V. The supply current is typically 200µA up to the startup threshold of 16V. Normal operating supply current is fairly flat at 18mA down to the shutdown threshold of 7V. Switching is inhibited for  $V_{IN}$  less than 12V due to the gate drive detection circuit.

**15V:** A 15V reference is used to bias the gate of an external power FET. The voltage temperature coefficient is typically  $3mV/^{\circ}C$  and the output can source 30mA. Typical dropout voltage is 1.5V for V<sub>IN</sub> less than 17V and 30mA of load current.

$V_{SW}$ : The Switch Output pin is the collector of the internal NPN power switch. This pin has a typical ON resistance of 0.4 $\Omega$  and a minimum breakdown voltage of 50V. This pin also ties to the FET gate drive detection circuit.

### LT1105

All functions on the LT1105 are equivalent to the LT1103 with the exception of the  $V_{SW}$  pin and the  $I_{LIM}$  pin and the availability of the OVLO, 5V, and SS functions.

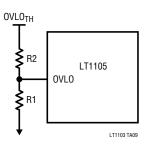

**OVLO:** The Overvoltage Lockout pin inhibits switching when the pin is pulled above its threshold voltage of 2.5V.

### PIN FUNCTIONS

OVLO is implemented with a resistor divider network from the rectified DC line and is used to protect the external FET from an overvoltage condition in the off state. This function is only available on the 14-lead DIP.

**5V:** A 5V reference is available to power primary-side circuitry. The temperature coefficient is typically 50ppm/ °C and the output can source 25mA. This function is only available on the 14-lead DIP.

**SS:** The Soft-start pin is used to either program start-up time with a capacitor to ground or to set external current limit with a resistor divider. The SS pin has a  $40\mu$ A pullup current and is reset to 0V by a 1mA pulldown current

during startup and shutdown. This function is only available on the 14-lead DIP.

$V_{SW}$ : The Switch Output pin is the output of a 1A NPN totem pole stage. The V<sub>SW</sub> pin turns the external FET on by pulling its gate high. Break-Before-Make action of 200ns on each switch edge is built in to eliminate cross-conduction currents.

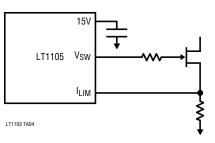

**I**<sub>LIM</sub>: The I<sub>LIM</sub> pin is the input to the current limit amplifier and requires the use of a non-inductive, power sense resistor from I<sub>LIM</sub> to ground to set current limit. The typical current limit threshold voltage is 350mV. The typical input bias current is 100 $\mu$ A out of the pin.

**BLOCK DIAGRAMS**

# **BLOCK DIAGRAMS**

# OPERATION

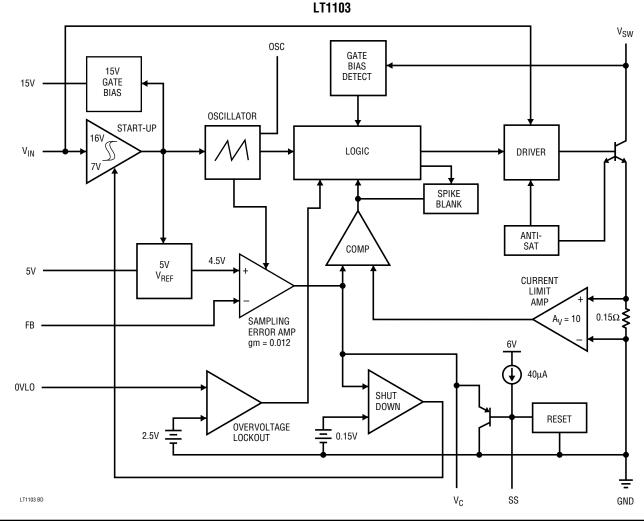

### LT1103

The LT1103 is a current-mode switcher. Switch duty cycle is controlled by switch current rather than directly by the output voltage. Referring to the block diagram, the switch is turned on at the start of each oscillator cycle. It is turned off when switch current reaches a pre-determined level. Control of output voltage is obtained by using the output of a voltage sensing error amplifier to set current trip level. This technique has several advantages. First, it has immediate response to input voltage variations, unlike ordinary switchers which have notoriously poor line transient response. Second, it reduces the 90° phase shift at midfrequencies in the transformer. This greatly simplifies closed loop frequency compensation under widely varying input voltage or output load conditions. Finally, it allows simple pulse-by-pulse current limiting to provide maximum switch protection under output overload or short-circuit conditions.

A start-up loop with hysteresis allows the IC supply voltage to be bootstrapped from an extra primary-side winding on the power transformer. From 0V to 16V on  $V_{IN}$ , the LT1103 is in a pre-start mode and total input current is typically 200µA. Above 16V, up to 30V, the 6V regulator that biases the internal circuitry and the externally avail-

# OPERATION

able 15V regulator is turned on. The internal circuitry remains biased on until  $V_{\rm IN}$  drops below 7V and the part returns to the pre-start mode. Output switching stops when the  $V_{SW}$  drive is less than 10V corresponding to  $V_{\rm IN}$  of about 12V.

The oscillator provides the basic clock for all internal timing. Frequency is adjustable to 200kHz with one external capacitor from OSC to ground. The oscillator turns on the output switch via the logic and driver circuitry. Adaptive anti-sat circuitry detects the onset of saturation in the power switch and adjusts driver current instantaneously to limit switch saturation. This minimizes driver dissipation and provides very rapid turn-off of the switch.

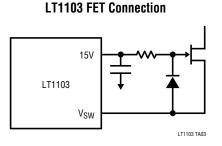

The LT1103 is designed to drive the source of an external power FET in common-gate configuration. The 15V regulator biases the gate to guarantee the FET is on when the switch is on. Special drive detection circuitry senses the gate bias voltage and prevents the output switch from turning on if the gate voltage is less than 10V or greater than 20V, the industry standards for power MOSFET operation.

The switch current is sensed internally and amplified to trip the comparator and turn off the switch according to the  $V_C$  pin control voltage. A blanking circuit suppresses the output of the current limit comparator for 500ns at the beginning of each switch cycle. This prevents false tripping of the comparator due to current spikes caused by external parasitic capacitance and diode stored charge.

The 4.5V Zener-based reference biases the positive input of the sampling error amplifier. The negative input (FB) is used for output voltage sensing. The sampling error amplifier allows the LT1103 to operate in fully-isolated flyback mode by regulating from the flyback voltage of the bootstrap winding. The leakage inductance spike at the leading edge of the flyback waveform is ignored with a blanking circuit. The flyback waveform is directly proportional to the output voltage in a transformer-coupled flyback topology. Output voltages are fully floating up to the breakdown voltage of the transformer windings. Multiple floating outputs are easily obtained with additional windings. The error signal developed at the comparator input is brought out externally. This  $V_C$  pin has three functions including frequency compensation, current limit adjustment, and total regulator shutdown. During normal operation, this pin sits at a voltage between 1.2V (low output current) and 4.4V (high output current). The error amplifier is a current output (gm) type, so this voltage can be externally clamped for adjusting current limit. Switch duty cycle goes to zero if the V<sub>C</sub> pin is pulled to ground through a diode, placing the LT1103 in an idle mode. Pulling the V<sub>C</sub> pin below 0.15V causes total regulator shutdown and places the LT1103 in a pre-start mode.

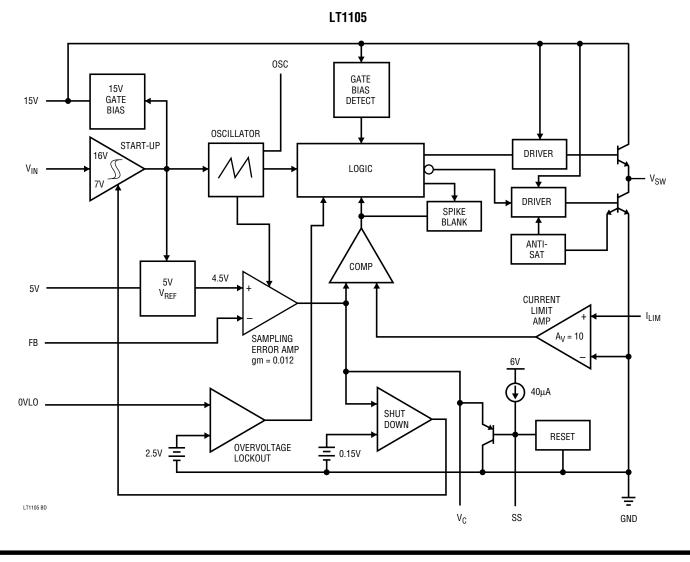

#### LT1105

The LT1105 is a current-mode switcher. Switch duty cycle is controlled by switch current rather than directly by output voltage. Referring to the block diagram, the switch is turned on at the start of each oscillator cycle. It is turned off when switch current reaches a pre-determined level. Control of output voltage is obtained by using the output of a voltage sensing error amplifier to set current trip level. This technique has several advantages. First, it has immediate response to input voltage variations, unlike ordinary switchers which have notoriously poor line transient response. Second, it reduces the 90° phase shift at midfrequencies in the transformer. This greatly simplifies closed loop frequency compensation under widely varying input voltage or output load conditions. Finally, it allows simple pulse-by-pulse current limiting to provide maximum switch protection under output overload or short-circuit conditions.

A start-up loop with hysteresis allows the IC supply voltage to be bootstrapped from an extra primary-side winding on the power transformer. From 0V to 16V on  $V_{IN}$ , the LT1105 is in pre-start mode and total input current is typically 200µA. Above 16V, up to 30V, the 6V regulator that biases the internal circuitry and the externally available 5V and 15V regulators are turned on. The internal circuitry remains biased on until  $V_{IN}$  drops below 7V and the part returns to pre-start mode. Output switching stops when the 15V gate bias reference is less than 10V corresponding to  $V_{IN}$  of about 12V.

# OPERATION

The oscillator provides the basic clock for all internal timing. Frequency is adjustable to 200kHz with one external capacitor from OSC to ground. The oscillator turns on the output switch via the logic and driver circuitry.

The LT1105 is designed to drive the gate of an external power FET in common-source configuration. The drivers and the 1A maximum totem-pole output stage are biased from the 15V gate bias reference. Special drive detection circuity senses the gate bias reference voltage and prevents the output switch from turning on if this voltage is less than 10V or greater than 20V. Break-Before-Make action of 200ns is built into each switch edge to eliminate cross conduction currents.

Switch current is sensed externally through a precision, power resistor. This allows for greater flexibility in switch current and output power than allowed by the LT1103. The voltage across the sense resistor is fed into the  $I_{LIM}$  pin and amplified to trip the comparator and turn off the switch according to the V<sub>C</sub> pin control voltage. A blanking circuit suppresses the output of the current limit comparator for 500ns at the beginning of each switch cycle. This prevents false tripping of the comparator due to current spikes caused by external parasitic capacitance and diode stored charge.

A 4.5V Zener-based reference biases the positive input of the sampling error amplifier. The negative input (FB) is used for output voltage sensing. The sampling error amplifier allows the LT1105 to operate in fully-isolated flyback mode by regulating the flyback voltage of the bootstrap winding. The leakage inductance spike at the leading edge of the flyback waveform is ignored with a blanking circuit. The flyback waveform is directly proportional to the output voltage in the transformer-coupled flyback topology. Output voltages are fully floating up to the breakdown voltage of the transformer windings. Multiple floating outputs are easily obtained with additional windings.

The error signal developed at the comparator input is brought out externally. The V<sub>C</sub> pin has three functions including frequency compensation, current limit adjustment, and total regulator shutdown. During normal operation, this pin sits at a voltage between 1.2V (low output current) and 4.4V (high output current). The error amplifier is a current output (gm) type, so this voltage can be externally clamped for adjusting current limit. Switch duty cycle goes to zero if the V<sub>C</sub> pin is pulled to ground through a diode, placing the LT1105 in an idle mode. Pulling the V<sub>C</sub> pin below 0.15V causes total regulator shutdown and places the LT1105 in pre-start mode.

The SS pin implements soft-start with one external capacitor to ground. The internal pullup current and clamp transistor limit the voltage at  $V_C$  to one diode drop above the voltage at the SS pin, thereby controlling the rate of rise of switch current in the regulator. The SS pin is reset to 0V when the LT1105 is in pre-start mode.

A final protection feature includes overvoltage lockout monitoring of the main supply voltage on the OVLO pin. If the OVLO pin is greater than 2.5V, the output switch is prevented from turning on. This function can be disabled by grounding the OVLO pin.

# **APPLICATIONS INFORMATION**

### **Bootstrap Start**

It is inefficient as well as impractical to power a switching regulator control IC from the rectified DC input as this voltage is several hundred volts. Self-biased switching regulator topologies take advantage of a lower voltage auxiliary winding on the power transformer or inductor to power the regulator, but require a startup cycle to begin regulation. Start-up circuitry with hysteresis built into the LT1103/ LT1105 allows the input voltage to increase from 0V to 16V before the regulator tries to start. During this time the startup current of the switching regulator is typically 200 $\mu$ A and all internal voltage regulators are off. The low quiescent current allows the input voltage to be trickled up with only 500 $\mu$ A of current from the rectified DC line voltage, thereby minimizing power dissipation in the startup resistor. At 16V, the internal voltage regulators are turned

on and switching begins. If enough power feeds back through the auxiliary winding to keep the input voltage to the switching regulator above 12V, then switching continues and a bootstrap start is accomplished. If the input voltage drops below 12V, then the FET drive detection circuit locks out switching. The input voltage continues to fall as the  $V_{IN}$  bypass capacitor is discharged by the normal quiescent current of the LT1103/LT1105. Once the input voltage falls below 7V, the internal voltage regulators are turned off and the switching regulator returns to the low startup current state. A continuous "burp start" mode indicates a fault condition or an incomplete power loop.

The trickle current required to bootstrap the regulator input voltage is typically generated with a resistor from the rectified DC input voltage. When combined with the regulator input bypass capacitor, the startup resistor creates a ramp whose slope governs the turn-on time of the regulator as well as the period of the "burp start" mode. The design trade-offs are power dissipated in the trickle resistor, the turn-on time of the regulator, and the hold-up time of the regulator input bypass capacitor. The value of the startup resistor is set by the minimum rectified DC input voltage to guarantee sufficient startup current. The recommended minimum trickle current is 500µA. The power rating of the startup resistor is set by the maximum rectified DC input voltage. A final consideration for the startup resistor is to insure that the maximum voltage rating of the resistor is not exceeded. Typical carbon film resistors have a voltage rating of 250V. The most reliable and economical solution for the startup resistor is generally provided by placing several 0.25W resistor in series.

The LT1103/LT1105 is designed to operate with supply pin voltages up to 30V. However, the auxiliary bias winding should be designed for a typical output voltage of 17V to minimize IC power dissipation and efficiency loss. Allowances must also be made for cross regulation of the bias voltage due to variations in the rectified DC line voltage and output load current.

#### Soft-Start

Soft-start refers to the controlled increase of switch current from a startup or shutdown state. This allows the power

This feature exhibits itself as a typical 3mA sink current capability on the  $V_C$  pin whereas source current is only 275µA. The low gm of the error amplifier allows small-valued compensation capacitors to be used on  $V_C$ . This allows the sink current to slew the compensation capacitor quickly. Therefore, overshoot of the output voltage on startup sequences and recovery from overload or short circuit conditions is prevented. However, if a longer startup period is required, the soft-start function can be used.

Soft-start is implemented with an internal  $40\mu$ A pullup and a transistor clamp on the V<sub>C</sub> pin so that a single external capacitor from SS ground can define the linear ramp function. The voltage at V<sub>C</sub> is limited to one V<sub>BE</sub> above the Soft-start pin (SS). The time to maximum switch current is defined as the capacitance on SS multiplied by the active range in volts of the V<sub>C</sub> pin divided by the pullup current:

$$\mathsf{T} = \frac{\mathsf{C} \bullet (3.2\mathsf{V})}{40\mu\mathsf{A}}$$

SS is reset to 0V whenever  $V_{IN}$  is less than 7V (pre-start mode) or when shutdown is activated by pulling  $V_C$  below 0.15V. The SS pin has a guaranteed reset sink current of 1mA when either the regulator supply voltage  $V_{IN}$  falls below 7V or the regulator is placed in shutdown.

#### Shutdown

The LT1103/LT1105 can be put in a low quiescent current shutdown mode by pulling V<sub>C</sub> below 150mV. In the shutdown mode the internal voltage regulators are turned off, SS is reset to 0V and the part draws less than 200 $\mu$ A. To initiate shutdown, about 400 $\mu$ A must be pulled out of V<sub>C</sub> until the internal voltage regulators turn off. Then, less than 50 $\mu$ A pulldown current is required to maintain shutdown. The shutdown function has about 60mV of hysteresis on the V<sub>C</sub> pin before the part returns to normal

operation. Soft-start, if used, controls the recovery from shutdown.

#### 5V Reference

A 5V reference output is available for the user's convenience to power primary-side circuitry or to generate a clamp voltage for switch current limiting. The output will source 25mA and the voltage temperature coefficient is typically 50ppm/°C. If bypassing of the 5V reference is required, a 0.1 $\mu$ F is recommended. Values of capacitance greater than 1 $\mu$ F may be susceptible to ringing due to decreased phase margin. In such cases, the capacitive load can be isolated from the reference output with a small series resistor at the expense of load regulation performance.

#### **Overvoltage Lockout**

The switching supply and primarily the external power MOSFET can be protected from an extreme surge of the input line voltage with the overvoltage lockout feature implemented on the OVLO pin. If the voltage on OVLO rises above its typical threshold voltage of 2.5V, output switching is inhibited. This feature can be implemented with a resistive divider off of the rectified DC input voltage. This feature is only available on the LT1105 in the 14-lead DIP and must be tied to ground if left unused.

### Ground (LT1103)

The ground pin of the LT1103 is important because it acts as the negative sense point for the internal error amplifier feedback signal, the negative sense point for the current limit amplifier and as the high current path for the 2A switch. The tab of the 7-lead TO-220 is internally connected to ground (pin 4).

To avoid degradation of load regulation, the feedback resistor divider string and the reference side of the bias winding should be directly connected to the ground pin on the package. These ground connections should not be mixed with high current carrying ground return paths. The length of the switch current ground path should be as short as possible to the input supply bypass capacitor and low resistance for best performance. The case of the LT1103 package is desirable to use as the high current ground return path as this is a lower resistive and inductive path than that of the actual package pin and will help minimize voltage spikes associated with the high dl/dt switch current.

Avoiding long wire runs to the ground pin minimizes load regulation effects and inductive voltages created by the high dl/dt switch current. Ground plane techniques should also be used and will help keep EMI to a minimum. Grounding techniques are illustrated in the Typical Applications section.

#### Ground (LT1105)

The ground pin of the LT1105 is important because it acts as the negative sense point for the internal error amplifier feedback signal and as the negative sense point for the current limit amplifier. The LT1105 8-pin MiniDIP has pin 1 as its ground. The LT1105 14-pin DIP has pin 1 and pin 7 as grounds and must be tied together for proper operation.

To avoid degradation of load regulation, the feedback resistor divider should be directly connected to the package ground pin. These ground connections should not be mixed with high current carrying ground return paths. The length of the switch current ground path should be as short as possible to the input supply bypass capacitor and low resistance for best performance. This will help minimize voltage spikes associated with the high dl/dt switch current.

Avoiding long wire runs to the ground pin minimizes load regulation effects and inductive voltages created by the high dl/dt switch current. Ground plane techniques should also be used and will help keep EMI to a minimum. Grounding techniques are illustrated in the Typical Applications section.

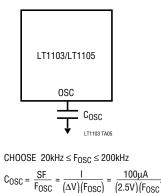

#### Oscillator

The oscillator of the LT1103/LT1105 is a linear ramp type powered from the internal 6V bias line. The charging currents and voltage thresholds are generated internally so that only one external capacitor is required to set the frequency. The  $150\mu$ A pullup current, which is on all the time, sets the preset maximum on-time of the switch and

the 450 $\mu$ A pulldown current which is turned on and off, sets the dead time. The threshold voltages are typically 2V and 4.5V, so for a 400pF capacitor the ramp-up time of the voltage on the OSC pin is 6.67 $\mu$ s and the ramp-down time is 3.3 $\mu$ s, resulting in an operating frequency of 100kHz. Although the oscillator, as well as the rest of the switching regulator, will function at higher frequencies, 200kHz is the practical upper limit that will allow control range for line and load regulation. The lowest operating frequency is limited by the sampling error amplifier to about 10kHz.

The frequency temperature coefficient is typically–80ppm/ °C with a good low T.C. capacitor. This means that with a low temperature coefficient capacitor, the temperature coefficient of the currents and the temperature coefficient of the thresholds sum to–80ppm/°C over the commercial temperature range. Bowing in the temperature coefficient of the currents affects the frequency about  $\pm 3\%$  at the extremes of the military temperature range. The capacitor type chosen will have a direct effect on the frequency tempco.

Maximum duty cycle is set internally by the pullup and pulldown currents, independent of frequency. It can be adjusted externally by modifying the fixed pullup current with an additional resistor. In practice, one resistor from the OSC pin to the 5V reference or to ground does the job. Note that the capacitor value must change to maintain the same frequency. For example, a 24k resistor from 5V to OSC and a 440pF capacitor from OSC to ground will yield 100kHz with 50% maximum duty cycle. A 56k resistor and a 280pF capacitor from OSC to ground will yield 100 kHz with 80% maximum duty cycle.

The oscillator can be synchronized to an external clock by coupling a sync pulse into the OSC pin. The width of this pulse should be a minimum of 500ns. The oscillator can only be synchronized up in frequency and the synchronizing frequency must be greater than the maximum possible unsynchronized frequency (for the chosen oscillator capacitor value). The amplitude of the sync pulse must be chosen so that the sum of the oscillator voltage amplitude plus the sync pulse amplitude does not exceed the 6V bias reference. Otherwise, the oscillator pullup current source will saturate and erroneous operation will result. If the LT1103/LT1105 is positioned on the primary side of the transformer and the external clock on the isolated secondary output side, the sync signal must be coupled into the OSC pin using a pulse transformer. The pulse transformer must meet all safety/isolation requirements as it also crosses the isolation boundary. An example of externally synchronizing the oscillator is shown in the Typical Applications section.

#### Gate Biasing (LT1103)

The LT1103 is designed to drive an external power MOSFET in the common-gate or cascode connection with the  $V_{SW}$  pin. The advantage is that the switch current can be sensed internally, eliminating a low-value, power sense resistor. The gate needs to be biased at a voltage high enough to guarantee that the FET is saturated when the open-collector source drive is on. This means 10V as specified in FET data sheets, plus 1V for the typical switch saturation voltage, plus a couple of volts for temperature variations and processing tolerances. This leads to 15V for a practical gate bias voltage.

Power MOSFETs are well suited to switching power supplies because their high speed switching characteristics promote high switching efficiency. To achieve high switching speed, the gate capacitance must be charged and discharged quickly with high peak currents. In particular, the turn-off current can be as high as the peak switch current. The switching speed is controlled by the impedance seen by the gate capacitance. Practically speaking, zero impedance is not desirable because of the high frequency noise spikes introduced to the system. The gate bias should be bypassed with a 1µF low ESR capacitor to ground and should have a 5 $\Omega$  resistor or larger in series with the gate to define the source impedance.

The LT1103 provides a 15V output intended for biasing the gate of the MOSFET. It will source 30mA into a capacitive load with no stability problems. The voltage temperature coefficient is +3mV/°C. If V<sub>IN</sub> drops below 17V, the 15V output follows about 2.0V below V<sub>IN</sub> until the part shuts down. If the 15V output is pulled above 17.5V, it will sink 5mA.

A special circuit in the LT1103 senses the voltage at V<sub>SW</sub> prior to turning on the switch. V<sub>SW</sub> is tied to the source of the FET and should represent the bias voltage on the gate when the switch is off. When the switch first turns off, the drain flies back until it is clamped by a snubber network. The source also flies high due to parasitic capacitive coupling on the FET and parasitic inductance of the leads. An extra diode from the source to the gate or  $V_{IN}$  will provide insurance against fault conditions that might otherwise damage the FET. The diode clamps the source to one diode drop above the gate or  $V_{IN}$ , thereby limiting the gate-source reverse bias. Once the energy in the leakage inductance spike is dissipated and the primary is being regulated to its flyback voltage, the diode shuts off. The source is then floating and its voltage will be close to the gate voltage. If the sensed voltage on V<sub>SW</sub> is less than 10V or greater than 20V, the circuit prevents the switch from turning on. This protects the FET from dissipating high power in a non-saturated state or from excessive gate-source voltage. The oscillator continues to run and the net effect is to skip switching cycles until the gate bias voltage is corrected. One consequence of the gate bias detection circuit is that the startup window is 6V if the gate is biased from  $V_{IN}$  and to 4V if the gate is biased from the 15V output. This influences the size of the bypass capacitor on VIN.

### V<sub>SW</sub> Output (LT1103)

The V<sub>SW</sub> pin of the LT1103 is the collector of an internal NPN power switch. This NPN has a typical on resistance of 0.4 $\Omega$  and a typical breakdown voltage (BV<sub>CBO</sub>) of 75V. Fast switching times and high efficiency are obtained by using a special driver loop which automatically adapts base drive current to the minimum required to keep the switch in a quasi-saturated state. The key element in the loop is an extra emitter on the output power transistor as seen in the block diagram. This emitter carries no current when the NPN output transistor collector is high (unsaturated). In this condition, the driver circuit can deliver very high base drive to the switch for fast turn-on. When the switch saturates, the extra emitter acts as a collector of an NPN

operating in inverted mode and pulls base current away from the driver. This linear feedback loop serves itself to keep the switch just at the edge of saturation. Very low switch current results in nearly zero driver current and high switch currents automatically increase driver current as necessary. The ratio of switch current to driver current is approximately 30:1. This ratio is determined by the sizing of the extra emitter and the value of the current source feeding the driver circuitry. The quasi-saturation state of the switch permits rapid turn-off without the need for reverse base-emitter voltage drive.

### Gate Biasing (LT1105)

The LT1105 is designed to drive an external power MOSFET in the common-source configuration with the totem-pole output  $V_{SW}$  pin. The advantage is added switch current flexibility (limited only by the choice of external power FET) and higher output power applications than allowed by LT1103. An external, non-inductive, power sense resistor must be used in series with the source of the FET to detect switch current and must be tied to the input of the current limit amplifier. The gate needs to be biased at a voltage high enough to guarantee that the FET is saturated when the totem-pole gate drive is on. This means 10V as specified in FET data sheets, plus the totem-pole high side saturation voltage plus a couple of volts for temperature variations and processing tolerances. This leads to 15V for a practical gate bias voltage.

Power MOSFETs are well suited to switching power supplies because their high speed switching characteristics promote high switching efficiency. To achieve high switching speed, the gate capacitance must be charged and discharged quickly with high peak currents. In particular, the turn-off current can be as high as the peak switch current. The switching speed is controlled by the impedance seen by the gate capacitance. Practically speaking, zero impedance is not desirable because of the high frequency noise spikes introduced to the system. The gate bias supply which drives the totem-pole output stage should be bypassed with a  $1\mu$ F low ESR capacitor to ground. This capacitor supplies the energy to charge the gate capacitance during gate drive turn-on. The power MOSFET should have a  $5\Omega$

resistor or larger in series with its gate from the  $V_{SW}\xspace$  pin to define the source impedance.

The LT1105 provides a 15V regulated output intended for driving the totem-pole output stage. It will source 30mA into a capacitive load with no stability problems. The output voltage temperature coefficient is +3mV/°C. If  $V_{IN}$  drops below 17V, the 15V output follows about 2.0V below  $V_{IN}$  until the part shuts down. If the 15V output is pulled above 17.5V, it will sink 5mA.

A special circuit in the LT1105 senses the voltage at the 15V regulated output prior to turning on the switch. The 15V regulator drives the totem-pole output stage and the V<sub>SW</sub> pin will pull the gate of the FET very close to the value of the 15V output when  $V_{SW}$  turns on. Therefore, the 15V output represents what the gate bias voltage on the FET will be when the FET is turned on. If the sensed voltage on the 15V output is less than 10V or greater than 20V, the circuit prevents the switch from turning on. This protects the FET from dissipating high power in a non-saturated state or from excessive gate-source voltage. The oscillator continues to run and the net effect is to skip switching cycles until the gate bias voltage is corrected. One consequence of the gate bias detection circuit is that the startup window is 4V. This influences the size of the bypass capacitor on V<sub>IN</sub>.

#### V<sub>SW</sub> Output (LT1105)

The  $V_{SW}$  pin of the LT1105 is the output of a 1A totem-pole driver stage. This output stage turns an external power MOSFET on by pulling its gate high. Break-Before-Make action of 200ns is built into each switch edge to eliminate cross-conduction currents. Fast switching times and high efficiency are obtained by using a low loss output stage and a special driver loop which automatically adapts base drive current to the totem-pole low-side drive. The key element in the loop is an extra emitter on the output pulldown transistor as seen in the block diagram. This emitter carries no current when the low-side transistor collector is high (unsaturated). In this condition, the driver can deliver very high base drive to the output transistor for fast turn-off. When the low-side transistor saturates, the extra emitter acts as a collector of an NPN operating in inverted mode and pulls base current away from the driver. This linear feedback loop serves itself to keep the switch just at the edge of saturation. This results in nearly zero driver current. The quasi-saturation state of the low-side switch permits rapid turn-on of the external FET when  $V_{SW}$  pulls high.

#### Fully-Isolated Flyback Mode

A unique sampling error amplifier included in the control loop of the LT1103/LT1105 eliminates the need for an opto-isolator while providing  $\pm 1\%$  line and load regulation in a magnetic flux-sensed flyback converter. In this mode, the flyback voltage on the primary during "switch off" time is sensed and regulated. It is difficult to derive a feedback signal directly from the primary flyback voltage as this voltage is typically several hundred volts. A dedicated winding is not required because the bias winding for the regulator lends itself to flux-sensing. Flux-sensing made practical simplifies the design of offline power supplies by minimizing the total number of external components and reduces the components which must cross the isolation barrier to one, the transformer. This inherently implies greater safety and reliability. The transformer must be optimized for coupling between the bias winding and the secondary output winding(s) while maintaining the required isolation and minimizing the parasitic leakage inductances.

Although magnetic flux-sensing has been used in the past, the technique has exhibited poor output voltage regulation due to the parasitics present in a transformer-coupled design. Transformers which provide the safety and isolation as required by various international safety/regulatory agencies also provide the poorest output voltage regulation. Solutions to these parasitic elements have been achieved with the novel sampling error amplifier of the LT1103/ LT1105. A brief review of flyback converter operation and the problems which create a poorly regulated output will provide insight on how the sampling error amplifier of the LT1103/LT1105 addresses the regulation issue of magnetic flux-sensed converters.

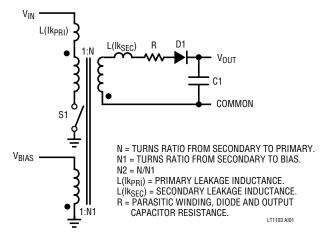

The following figure shows a simplified diagram of a flyback converter using magnetic flux-sensing. The major parasitic elements present in the transformer-coupled

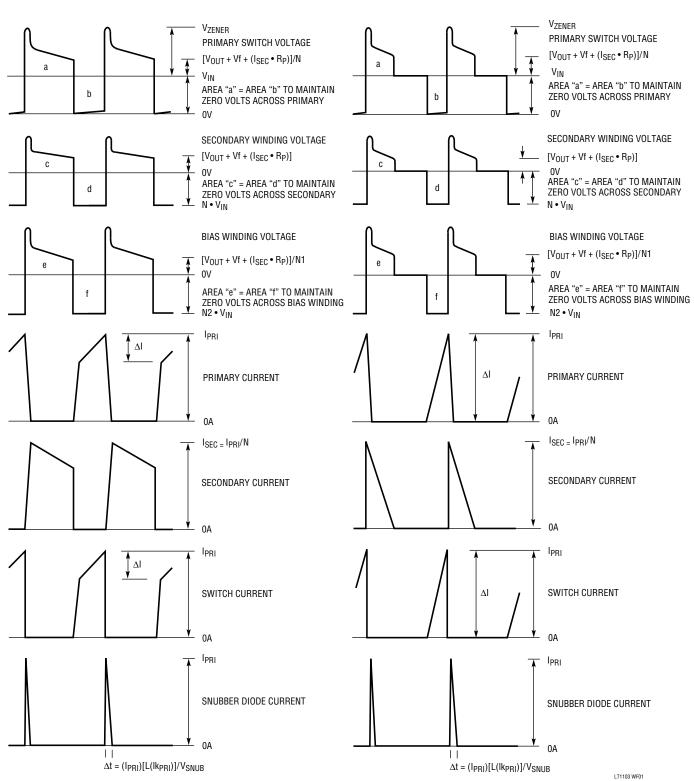

design are indicated. The relationships between the primary voltage, the secondary voltage, the bias voltage and the winding currents are indicated in the figures found on the following page for both continuous and discontinuous modes of operation.

#### **Simplified Flyback Converter**

When the switch "turns on," the primary winding sees the input voltage and the secondary and bias windings go to negative voltages as a function of the turns ratio. Current builds in the primary winding as the transformer stores energy. When the switch "turns off," the voltage across the switch flies back to a clamp level as defined by a snubber network until the energy in the leakage inductance of the primary dissipates. Leakage inductance is one of the main parasitic elements in a flux-sensed converter and is modeled as an inductor in series with the primary and secondary of the transformer. These parasitic inductances contribute to changes in the bias winding voltage and thus the output voltage with increasing load current.

The energy stored in the transformer transfers through the secondary and bias windings during "switch off" time. Ideally, the voltage across the bias winding is set by the DC output voltage, the forward voltage of the output diode, and the turns ratio of the transformer after the energy in the leakage inductance spike of the primary is dissipated.

This relationship holds until the energy in the transformer drops to zero (discontinuous mode) or the switch turns on again (continuous mode). Either case results in the voltage across the secondary and bias windings decreasing to zero or changing polarity. Therefore, the voltage on the bias winding is only valid as a representation of the output voltage while the secondary is delivering current.

Although the bias winding flyback voltage is a representation of the output voltage, its voltage is not constant. For a brief period following the leakage inductance spike, the bias winding flyback voltage decreases due to nonlinearities and parasitics present in the transformer. Following this nonlinear behavior is a period where the bias winding flyback voltage decreases linearly. This behavior is easily explained. Current flow in the secondary decreases linearly at a rate determined by the voltage across the secondary and the inductance of the secondary. The parasitic secondary leakage inductance appears as an impedance in series with the secondary winding. In addition, parasitic resistances exist in the secondary winding. the output diode and the output capacitor. These impedances can be combined to form a lumped sum equivalent and which cause a voltage drop as secondary current flows. This voltage drop is coupled from the secondary to the bias winding flyback voltage and becomes more significant as the output is loaded more heavily. This voltage drop is largest at the beginning of "switch off" time and smallest just prior to either all transformer energy being depleted or the switch turning on again.

The best representation of the output voltage is just prior to either all transformer energy being used up and the bias winding voltage collapsing to zero or just prior to the switch turning on again and the bias winding going negative. This point in time also represents the smallest forward voltage for the output diode. It is possible to redefine the relationship between the secondary winding voltage and the bias winding voltage as:

$$V_{BIAS} = \frac{\left(V_{OUT} + Vf + I \bullet R_{P}\right)}{N1}$$

where Vf is the forward voltage of the output diode, I is the current flowing in the secondary,  $R_P$  is the lumped sum equivalent secondary parasitic impedance and N1 is thetransformer turns ratio from the secondary to the bias winding. It is apparent that even though the above point in

Flyback Waveform for Continuous Mode Operation

#### Flyback Waveform for Discontinuous Mode Operation

**TECHNOLOGY**

time is the most accurate representation of the output voltage, the answer given by the bias winding voltage is still off from the "true" answer by the amount  $I \cdot R_P/N1$ .

The sampling error amplifier of the LT1103/LT1105 provides solutions to the errors associated with the bias winding flyback voltage. The error amplifier is comprised of a leakage inductance spike blanking circuit, a slew rate limited tracking amplifier, a level detector, a sample and hold, an output gm stage and load regulation compensation circuitry. This all seems complicated at first glance, but its operation is straightforward and transparent to the user of the IC. When viewed from a system or block level, the sampling error amplifier behaves like a simple transconductance amplifier. Here's how it works.

The sampling error amplifier takes advantage of the fact that the voltage across the bias winding during at least a portion of switch-off time is proportional to the DC output voltage of the secondary winding. The feedback network used to sense the bias winding voltage is no longer comprised of a traditional peak detector in conjunction with a resistor divider network. The feedback network consists of a diode in series with the bias winding feeding the resistor divider network directly. The resultant error signal is then fed into the input of the error amplifier. The purpose of the diode in series with the bias winding is now not to peak detect, but to prevent the FB pin (input of the error amplifier) from being pulled negative and forward biasing the substrate of the IC when the bias winding changes polarity with "switch turn-on."

The primary winding leakage inductance spike effects are first eliminated with an internal blanking circuit in the LT1103/LT1105 which suppresses the input of the FB pin for  $1.5\mu$ s at the start of "switch off" time. This prevents the primary leakage inductance spike from being propagated through the error amplifier and affecting the regulated output voltage.

With the effects of the leakage inductance spike eliminated, the effects of decreasing bias winding flyback voltage can be addressed. With the traditional diode/ capacitor peak detector circuitry eliminated from the feedback network, the tracking amplifier of the LT1103/LT1105 follows the flyback waveform as it changes with time and amplifies the difference between the flyback signal and the internal 4.5V reference. Tracking is maintained until the point in time where the bias winding voltage collapses as a result of all transformer energy being depleted (discontinuous mode) or the switch turning on again (continuous mode). The level detector circuit senses the fact that the bias winding flyback voltage is no longer a representation of the output voltage and activates an internal peak detector. This effectively saves the most accurate representation of the output voltage which is then buffered to the second stage of the error amplifier.

The second stage of the error amplifier consists of a sample and hold. When the switch turns on, the sample and hold samples the buffered error voltage for  $1\mu$ s and then holds for the remainder of the switch cycle. This held voltage is then processed by the output gm stage and converted into a control signal at the output of the error amplifier, the V<sub>C</sub> pin.

The final adjustment in regulation is provided by the load regulation compensation circuitry. As stated earlier, output regulation degrades with increasing load current (output power). The effect is traced to secondary leakage inductance and parasitic secondary winding, diode and output capacitor resistances. Even though the tracking amplifier has obtained the most accurate representation of the output voltage, its answer is still flawed by the amount of the voltage drop across the secondary parasitic lumped sum equivalent impedance which is coupled to the bias winding voltage. This error increases with increasing load current. Therefore, a technique for sensing load current conditions has been added to the LT1103/LT1105. The switch current is proportional to the load current by the turns ratio of the transformer. A small current proportional to switch current is generated in the LT1103/LT1105 and fed back to the FB pin. This allows the input bias current of the sampling error amplifier to be a function of load current. A resistor in series with the FB pin generates a linear increase in the effective reference voltage with increasing load current. This translates to a linear increase in output voltage with increasing load current. By adjusting the value of the series resistor, the slope of the load compensation can be set to cancel the effects of these parasitic voltage drops. The feature can be ignored by

eliminating the series resistor and lowering the equivalent divider impedance to swamp out the effects of the input bias current.

#### **Frequency Compensation**

In order to prevent a regulator loop using the LT1103/ LT1105 from oscillating, frequency compensation is required. Although the architecture of the LT1103/LT1105 is simple enough to lend itself to a mathematical approach to frequency compensation, the added complication of input/or output filters, unknown capacitor ESR, and gross operating point changes with input voltage and load current variations all suggest a more practical empirical approach. Many hours spent on breadboards have shown that the simplest way to optimize the frequency compensation of the LT1103/LT1105 is to use transient response techniques and an "R-C" box to quickly iterate toward the final compensation network. Additional information on this technique of frequency compensation can be found in Linear Technology's Application Note 19.

In general, frequency compensation is accomplished with an R-C series network on the V<sub>C</sub> pin. The error amplifier has a Gm (voltage "in" to current "out") of  $\approx$  12000 µmhos. Voltage gain is determined by multiplying Gm times the total equivalent error amplifier output loading, consisting of the error amplifier output impedance in parallel with the series R-C external frequency compensation network. At DC, the external R-C can be ignored. The output impedance of the error amplifier is typically 100k $\Omega$  resulting in a voltage gain of  $\approx$  1200. At frequencies just above DC, the voltage gain is determined by the external compensation, R<sub>C</sub> and C<sub>C</sub>. The gain at mid frequencies is given by:

$$A_{V} = \frac{Gm}{2\pi \bullet f \bullet C_{C}}$$

The gain at high frequencies is given by:

$A_V = Gm \bullet R_C$

Phase shift from the FB pin to the V<sub>C</sub> pin is 90° at mid frequencies where the external C<sub>C</sub> is controlling gain, then drops back to 0° (actually 180° since FB is an inverting

input) when the reactance of  $C_C$  is small compared to  $R_C$ . Thus, this R-C series network forms a pole-zero pair. The pole is set by the high impedance output of the error amplifier and the value of  $C_C$  on the  $V_C$  pin. The zero is formed by the value of  $C_C$  and the value of  $R_C$  in series with  $C_C$  on the  $V_C$  pin. The R-C series network will have capacitor values in the range of  $0.1\mu F - 1.0\mu F$  and series resistor values in the range of  $100\Omega - 1000\Omega$ .

It is noted that the R-C network on the V<sub>C</sub> pin forms the main compensation network for the regulator loop. However, if the load regulation compensation feature is used as explained in the section on fully-isolated flyback mode, additional frequency compensation components are required. The load regulation compensation feature involves the use of local positive feedback from the  $V_{\rm C}$  pin to the FB pin. Thus, it is possible to add enough load regulation compensation to make the loop oscillate. In order to prevent oscillation, it is necessary to roll off this local positive feedback at high frequencies. This is accomplished by placing a capacitor in parallel with the compensation resistor which is in series with the FB pin. A value for this capacitor in the range of  $0.01\mu$ F to  $0.1\mu$ F is recommended. The time constant associated with this R/ C combination will be longer than that associated with the loop bandwidth. Thus, transient response will be affected in that settling time will be increased. However, this is typically not as important as controlling the absolute under or overshoot amplitude of the system in response to load current changes which could cause deleterious system operation.

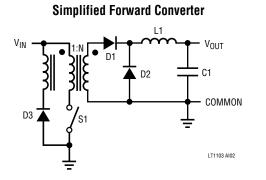

#### Switching Regulator Topologies

Two basic switching regulator topologies are pertinent to the LT1103/LT1105, the flyback and forward converter. The flyback converter employs a transformer to convert one voltage to either a higher or lower output voltage.  $V_{OUT}$  in *continuous mode* is defined as:

$$V_{OUT} = V_{IN} \bullet N \bullet \frac{DC}{(1 - DC)}$$

where N is the transformer turns ratio of secondary to primary and DC is the duty cycle. This formula can be rewritten in terms of duty cycle as:

$$\mathsf{DC} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\left(\mathsf{V}_{\mathsf{OUT}} + \mathsf{N} \bullet \mathsf{V}_{\mathsf{IN}}\right)}$$

It is important to define the full range of input voltage, the range of output loading conditions and the regulation requirements for a design. Duty cycle should be calculated for both minimum and maximum input voltage.

In many applications, N can vary over a wide range without degrading performance. If maximum output power is desired, N can be optimized:

$$N_{(OPT)} = \frac{V_{OUT} + Vf}{\left(V_{M} - V_{IN(MAX)} - V_{SNUB}\right)}$$

where Vf = Forward voltage of the output diode

V<sub>M</sub> = Maximum switch voltage

V<sub>SNUB</sub> = Snubber clamp level – primary flyback voltage.

In the isolated flyback mode, the LT1103/LT1105 sense and regulate the transformer primary voltage  $V_{PRI}$  during "switch off" time. The secondary output voltage will be regulated if  $V_{PRI}$  is regulated.  $V_{PRI}$  is related to  $V_{OUT}$  by:

$$V_{PRI} = \frac{(V_{OUT} + Vf)}{N}$$

This allows duty cycle for an isolated flyback converter to be rewritten as:

$$DC = Duty Cycle = \frac{V_{PRI}}{(V_{PRI} + V_{IN})}$$

An important transformer parameter to be determined is the primary inductance  $L_{PRI}$ . The value of this inductance is a trade-off between core size, regulation requirements, leakage inductance effects and magnetizing current  $\Delta I$ . Magnetizing current is the difference between the primary current at the start of "switch on" time and the current at the end of "switch on" time. If maximum output power is needed, a reasonable starting value is found by assigning  $\Delta$ I a value of 20% of the peak switch current (2A for the LT1103 and set by the external FET rating used with the LT1105). With this design approach, L<sub>PRI</sub> is defined as:

$$L_{PRI} = \frac{V_{IN}}{(\Delta I)(f)\left(1 + \frac{V_{IN}}{V_{PRI}}\right)}$$

If maximum output power is not required, then  $\Delta I$  can be increased which results in lower primary inductance and smaller magnetics. Maximum output power with an isolated flyback converter is defined by the primary flyback voltage and the peak allowed switch current and is limited to:

$$P_{OUT(MAX)} = \frac{(V_{PRI})}{(V_{PRI} + V_{IN})} \left[ V_{IN} \left( I_{P} - \frac{\Delta I}{2} \right) - \left( I_{P} \right)^{2} R \right] E$$

where R = Total "switch" ON resistance

$I_P$  = Maximum switch current