## Z8400/Z84C00 NMOS/CMOS Z80® CPU Central Processing Unit

#### **FEATURES**

The extensive instruction set contains 158 instructions, including the 8080A instruction set as a subset.

- NMOS version for low cost high performance solutions, CMOS version for high performance low power designs.

- NMOS Z0840004 4 MHz, Z0840006 6.17 MHz, Z0840008 - 8 MHz.

- CMOS Z84C0006 DC to 6.17 MHz, Z84C008 DC to 8 MHz, Z84C0010 - DC to 10 MHz, Z84C0020 - DC -20 MHz

- 6 MHz version can be operated at 6.144 MHz clock.

- The Z80 microprocessors and associated family of peripherals can be linked by a vectored interrupt system. This system can be daisy-chained to allow implementation of a priority interrupt scheme.

- Duplicate set of both general-purpose and flag registers.

- Two sixteen-bit index registers.

- Three modes of maskable interrupts:

Mode 0—8080A similar;

Mode 1—Non-Z80 environment, location 38H;

Mode 2—Z80 family peripherals, vectored interrupts.

- On-chip dynamic memory refresh counter.

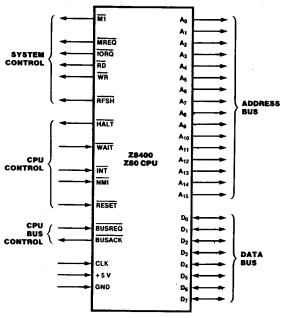

Figure 1. Pin Functions

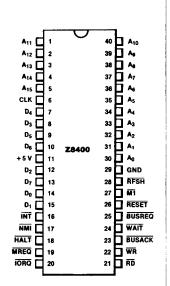

Figure 2. 40-pin Dual-In-Line (DIP), Pin Assignments

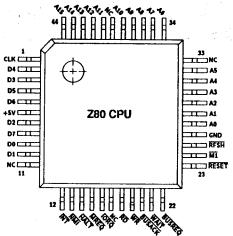

44 pin Quad Flat Pack (QFP), Pin Assignments (Only available for 84C00)

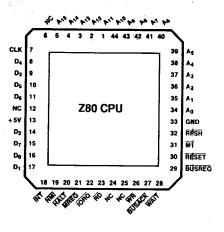

Figure 2b. 44-Pin Chip Carrier Pin Assignments

#### **GENERAL DESCRIPTION**

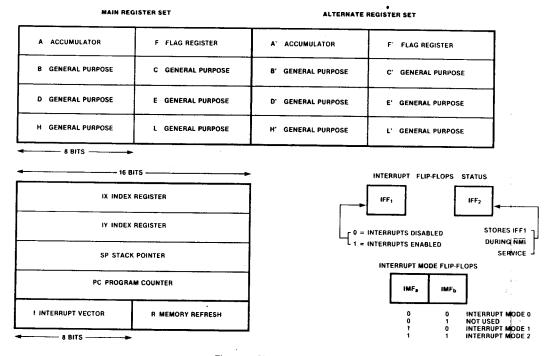

The CPUs are fourth-generation enhanced microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second- and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response.

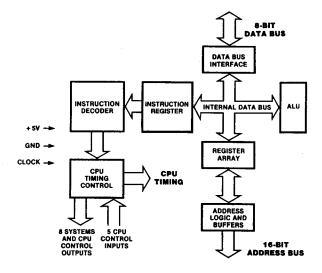

The CPU also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single +5V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits; the CPU is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the processors. Subsequent text provides more detail on the I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. Z80C CPU Block Diagram

Table 1. Z80C CPU Registers

|                                    | Register           | Size (Bits) | Remarks                                                                                                                                             |

|------------------------------------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| A, A'                              | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                   |

| F, F'                              | Flags              | 8           | See Instruction Set.                                                                                                                                |

| B, B'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                              |

| C, C'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                              |

| D, D'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                              |

| E, E'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                              |

| H, H'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                              |

| L, L'                              | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                              |

|                                    |                    |             | Note: The (B,C), (D,E), and (H,L) sets are combined as follows:  B — High byte C — Low byte  D — High byte E — Low byte  H — High byte L — Low byte |

|                                    | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                        |

| R                                  | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically incremented and placed on the address bus during each instruction fetch cycle.      |

| IX                                 | Index Register     | 16          | Used for indexed addressing.                                                                                                                        |

| IY .                               | Index Register     | 16          | Used for indexed addressing                                                                                                                         |

| SP                                 | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in instruction set.                                                                          |

| PC                                 | Program Counter    | 16          | Holds address of next instruction.                                                                                                                  |

| IFF <sub>1</sub> -IFF <sub>2</sub> | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                           |

| IMFa-IMFb                          | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                              |

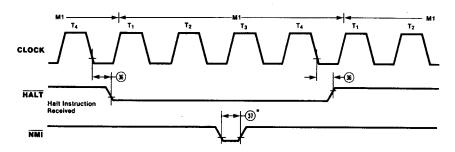

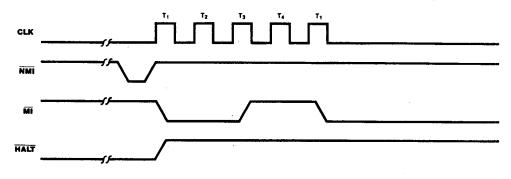

failure has been detected. After recognition of the \$\overline{NMI}\$ signal (providing \$\overline{BUSREQ}\$ is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

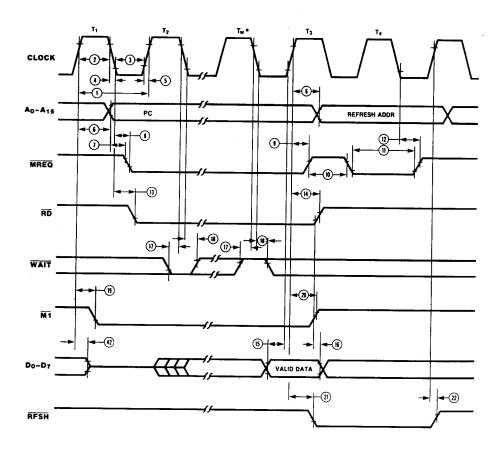

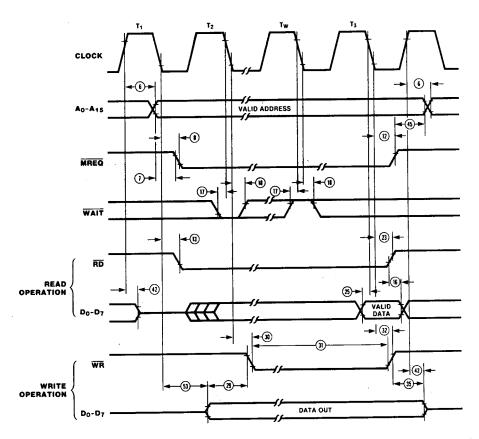

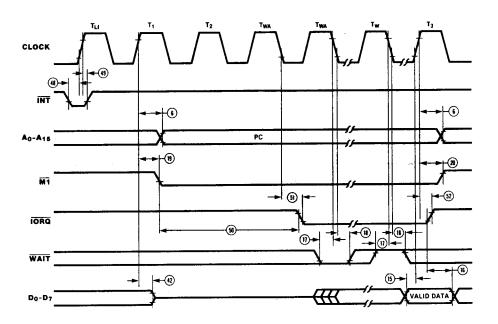

Maskable Interrupt (INT). Regardless of the interrupt mode set by the user, the CPU response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by the CPU (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (M1) cycle in which IORQ becomes active rather than MREQ, as in a normal M1 cycle. In addition, this special M1 cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request.

**Mode 0 Interrupt Operation.** This mode is similar to the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus. This is normally a Restart instruction, which will initiate a call

to the selected one of eight restart locations in page zero of memory. Unlike the 8080, the Z80 CPU responds to the Call instruction with only one interrupt acknowledge cycle followed by two memory read cycles.

**Mode 1 Interrupt Operation.** Mode 1 operation is very similar to that for the  $\overline{NMI}$ . The principal difference is that the Mode 1 interrupt has only one restart location, 0038H.

Mode 2 Interrupt Operation. This interrupt mode has been designed to most effectively utilize the capabilities of the Z80 microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit vector on the data bus during the interrupt acknowledge cycle. The CPU forms a pointer using this byte as the lower 8 bits and the contents of the I register as the upper 8 bits. This points to an entry in a table of addresses for interrupt service routines. The CPU then jumps to the routine at that

address. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines. These routines may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0 (A<sub>a</sub>) must be a zero.

Interrupt Enable/Disable Operation. Two flip-flops, IFF1 and IFF2, referred to in the register description, are used to signal the CPU interrupt status. Operation of the two flip-flops is described in Table 2. For more details, refer to the Z80 CPU Technical Manual (03-0029-01) and Z80 Assembly Language Programming Manual (03-0002-01).

Table 2. State of Flip-Flops

| Action                       | IFF <sub>1</sub> | IFF <sub>2</sub> | Comments                                                                     |

|------------------------------|------------------|------------------|------------------------------------------------------------------------------|

| CPU Reset                    | 0                | 0                | Maskable interrupt                                                           |

| DI instruction execution     | 0                | 0                | Maskable interrupt<br>INT disabled                                           |

| El instruction execution     | 1                | 1                | Maskable interrupt                                                           |

| LD A,I instruction execution | •                | •                | IFF <sub>2</sub> → Parity flag                                               |

| LD A,R instruction execution | •                | •                | IFF <sub>2</sub> → Parity flag                                               |

| Accept NMI                   | 0                | •                | Maskable interrupt                                                           |

| RETN instruction execution   | IFF <sub>2</sub> | •                | IFF <sub>2</sub> → IFF <sub>1</sub> at completion of an NMI service routine. |

#### **INSTRUCTION SET**

The microprocessor has one of the most powerful and versatile instruction sets available in any 8-bit microprocessor. It includes such unique operations as a block move for fast, efficient data transfers within memory, or between memory and I/O. It also allows operations on any bit in any location in memory.

The following is a summary of the instruction set which shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. For an explanation of flag notations and symbols for mnemonic tables, see the Symbolic Notations section which follows these tables. The Z80 CPU Technical Manual (03-0029-01). the Programmer's Reference Guide (03-0012-03), and Assembly Language Programming Manual (03-0002-01) contain significantly more details for programming use.

| ۱r | ne instructions are divided into the following categorie |

|----|----------------------------------------------------------|

|    | 8-bit loads                                              |

|    | 16-bit loads                                             |

|    | Exchanges, block transfers, and searches                 |

|    | 8-bit arithmetic and logic operations                    |

|    | General-purpose arithmetic and CPU control               |

|    | 16-bit arithmetic operations                             |

|    | Rotates and shifts                                       |

|   | Bit set, reset, and test operations |

|---|-------------------------------------|

|   | Jumps                               |

|   | Calls, returns, and restarts        |

|   | Input and output operations         |

| Δ | variety of addressing modes are im  |

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include:

| Immediate          |

|--------------------|

| Immediate extended |

| Modified page zero |

| Relative           |

| Extended           |

| Indexed            |

| Register           |

| Register indirect  |

| Implied            |

| Bit                |

|                    |

## 8-BIT LOAD GROUP

|                | Symbolic                |   |   |   | Fk | ngs |     |   |   |    | Opcod       | •   |     | No. of | No. of M | No. of T |       |       |

|----------------|-------------------------|---|---|---|----|-----|-----|---|---|----|-------------|-----|-----|--------|----------|----------|-------|-------|

| Mnemonic       | Operation               | S | Z |   | H  |     | P/V | N | C | 76 | 543         | 210 | Hex | Bytes  | Cycles   | States   | Com   | ments |

| LD r, r'       | r ← r'                  | • | • |   |    | Х   | •   | • | • | 01 | r           | r'  |     | 1      | 1        | 4        | r, r' | Reg.  |

| LD r, n        | r ← n                   | • | • | Χ | •  | Х   | •   | • | • | 00 | r           | 110 |     | 2      | 2        | 7        | 000   | В     |

|                |                         |   |   |   |    |     |     |   |   |    | <b>←</b> n→ |     |     |        |          |          | 001   | С     |

| LD r, (HL)     | r ← (HL)                | • | • | Χ | •  | Х   | •   | • | • | 01 | r           | 110 |     | 1      | 2        | 7        | 010   | D     |

| LD r, (IX + d) | r ← (IX + d)            | • | • | Х | •  | Χ   | •   | • | • | 11 | 011         | 101 | DD  | 3      | 5        | 19       | 011   | Ε     |

|                |                         |   |   |   |    |     |     |   |   | 01 | r           | 110 |     |        |          |          | 100   | н     |

|                |                         |   |   |   |    |     |     |   |   |    | <b>~</b> d→ |     |     |        |          |          | 101   | L     |

| LD r, (IY + d) | $r \leftarrow (IY + d)$ | • | • | Х | •  | Х   | •   | • | • | 11 | 111         | 101 | FD  | 3      | 5        | 19       | 111   | Α     |

|                |                         |   |   |   |    |     |     |   |   | 01 | r           | 110 |     |        |          |          |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | <b>←</b> d→ |     |     |        |          |          |       |       |

| LD (HL), r     | (HL) ← r                | • | • | Х | •  | Х   | •   | • | • | 01 | 110         | ſ   |     | 1      | 2        | 7        |       |       |

| LD (IX + d), r | (IX+d) <del>←</del> r   | • | • | Χ | •  | Χ   | •   | • | • | 11 | 011         | 101 | DD  | 3      | 5        | 19       |       |       |

|                |                         |   |   |   |    |     |     |   |   | 01 | 110         | r   |     |        |          |          |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | <b>←</b> d→ |     |     |        |          |          |       |       |

| LD (IY + d), r | (IY+d) <del></del> r    | • | • | Х | •  | Х   | •   | • | • | 11 | 111         | 101 | FD  | 3      | 5        | 19       |       |       |

|                |                         | • |   |   |    |     |     |   |   | 01 | 110         | r   |     |        |          |          |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | <b>←</b> d→ |     |     |        |          |          |       |       |

| LD (HL), n     | (HL) ← n                | • | • | Х | •  | Х   | •   | • | • | 00 | 110         | 110 | 36  | 2      | 3        | 10       |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | +n→         |     |     |        |          |          |       |       |

| LD (IX + d), n | (IX + d) ← n            | • | • | Х | •  | Х   | •   | • | • | 11 | 011         | 101 | DD  | 4      | 5        | 19       |       |       |

|                |                         |   |   |   |    |     |     |   |   | 00 | 110         | 110 | 36  |        |          |          |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | ←d →        |     |     |        |          |          |       |       |

|                |                         |   |   |   |    |     |     |   |   |    | ←n→         |     |     |        |          |          |       |       |

## 8-BIT LOAD GROUP (Continued)

|              | Symbolic              |          |          |   | FI | ags | ,   |     |   |    | Орсос        | le . |     | No. of | No. of M | No. of T |          |

|--------------|-----------------------|----------|----------|---|----|-----|-----|-----|---|----|--------------|------|-----|--------|----------|----------|----------|

| Mnemonic     | Operation             | S        | Z        |   | Н  | •   |     | V N | С |    | 543          |      | Hex | Bytes  | Cycles   | States   | Comments |

| LD (IY+d), n | (IY+d) <del>←</del> n | •        | •        | Х | •  | х   | •   | •   | • | 11 | 111          | 101  | FD  | 4      | 5        | 19       |          |

|              |                       |          |          |   |    |     |     |     |   | 00 | 110          | 110  | 36  |        |          |          |          |

|              |                       |          |          |   |    |     |     |     |   |    | <b>←</b> d → | •    |     |        |          |          |          |

|              |                       |          |          |   |    |     |     |     |   |    | <b>←</b> n → | •    |     |        |          |          |          |

| LD A, (BC)   | A ← (BC)              | •        | •        | Χ | •  | Х   | •   | •   | • | 00 | 001          | 010  | OA  | 1      | 2        | 7        |          |

| LD A, (DE)   | A ← (DE)              | •        | •        | Χ | •  | Х   | •   | •   | • | 00 | 011          | 010  | 1A  | 1      | 2        | 7        |          |

| LD A, (nn)   | A ← (nn)              | •        | •        | Χ | •  | Х   | •   | •   | • | 00 | 111          | 010  | 3A  | 3      | 4        | 13       |          |

|              |                       |          |          |   |    |     |     |     |   |    | <b>←</b> n→  |      |     |        |          |          |          |

|              |                       |          |          |   |    |     |     |     |   |    | <b>←</b> n → | •    |     |        |          |          |          |

| LD (BC), A   | (BC) ← A              | •        | •        | Χ | •  | Х   | •   | •   | • | 00 | 000          | 010  | 02  | 1      | 2        | 7        |          |

| LD (DE), A   | (DE) ← A              | •        | •        | Х | •  | Х   | •   | •   | • | 00 | 010          | 010  | 12  | 1      | 2        | 7        |          |

| _D (nn), A   | (nn) ← A              | •        | •        | Χ | •  | Х   | •   | ٠   | • | 00 | 110          | 010  | 32  | 3      | 4        | 13       |          |

|              |                       |          |          |   |    |     |     |     |   |    | <b>←</b> n → |      |     |        |          |          |          |

|              |                       |          |          |   |    |     |     |     |   |    | ←n→          |      |     |        |          |          |          |

| LD A, I      | A←I                   | <b>‡</b> | #        | Х | 0  | Χ   | IFF | 0   | • | 11 | 101          | 101  | ED  | 2      | 2        | 9        |          |

|              |                       |          |          |   |    |     |     |     |   | 01 | 010          | 111  | 57  |        |          |          |          |

| ∟DA, R       | A←R                   | <b>‡</b> | <b>‡</b> | Χ | 0  | Х   | IFF | 0   | • | 11 | 101          | 101  | ED  | 2      | 2        | 9        |          |

|              |                       |          |          |   |    |     |     |     |   | 01 | 011          | 111  | 5F  |        |          | •        |          |

| .D I, A      | I ← A                 | •        | •        | Х | •  | Х   | •   | •   | • | 11 | 101          | 101  | ED  | 2      | 2        | 9        |          |

|              |                       |          |          |   |    |     |     |     |   | 01 | 000          | 111  | 47  |        | _        | =        |          |

| .D R, A      | R←A                   | •        | •        | Х | •  | Х   | •   | •   | • | 11 | 101          | 101  | ED  | 2      | 2        | 9        |          |

|              |                       |          |          |   |    |     |     |     |   | 01 | 001          | 111  | 4F  | •      | -        | -        |          |

NOTE: IFF, the content of the interrupt enable flip-flop, (IFF  $_{\!2}$  ), is copied into the P/V flag.

## **16-BIT LOAD GROUP**

| Mnemonic    | Symbolic<br>Operation                                | s | z |   | Fla | ags | P/V | N | С |    | Opcode<br>543 |     | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Con      | nmenti   |

|-------------|------------------------------------------------------|---|---|---|-----|-----|-----|---|---|----|---------------|-----|-----|-----------------|--------------------|--------------------|----------|----------|

| LD dd, nn   | dd ← nn                                              | • | • | X | •   | Х   | •   | • | • | 00 | dd0<br>+ n →  | 001 |     | 3               | 3                  | 10                 | dd       | Pair     |

|             |                                                      |   |   |   |     |     |     |   |   |    | +n→           |     |     |                 |                    |                    | 00<br>01 | BC<br>DE |

| LD IX, nn   | IX ← nn                                              | • | • | X | •   | X   | •   | • | • | 11 | 011           | 101 | DD  | 4               | 4                  | 14                 | 10       | HL       |

|             |                                                      |   |   |   |     |     |     |   |   | 00 | 100<br>←n→    | 001 | 21  |                 |                    |                    | 11       | SP       |

| 150         |                                                      |   |   |   |     |     |     |   |   |    | <b>←</b> n →  |     |     |                 |                    |                    |          |          |

| .D IY, nn   | IY ← nn                                              | • | • | X | •   | Х   | •   | • | • | 11 | 111           | 101 | FD  | 4               | 4                  | 14                 |          |          |

|             |                                                      |   |   |   |     |     |     |   |   | 00 | <b>←</b> n→   | 001 | 21  |                 |                    |                    |          |          |

| LD HL, (nn) | H ← (nn + 1)                                         | • | • | х | •   | Х   | •   | • |   | 00 | ←n→<br>101    | 010 | 2A  | 3               | 5                  | 16                 |          |          |

|             | L ← (nn)                                             |   |   |   |     |     |     |   |   |    | ←n→<br>←n→    |     |     |                 |                    |                    |          |          |

| LD dd, (nn) | $dd_H \leftarrow (nn + 1)$<br>$dd_L \leftarrow (nn)$ | • | • | X | •   | X   | •   | • | • | 11 | 101           | 101 | ED  | 4               | 6                  | 20                 |          |          |

|             | 40[ 4- (IIII)                                        |   |   |   |     |     |     |   |   | 01 | dd1<br>←n→    | 011 |     |                 |                    |                    |          |          |

|             |                                                      |   |   |   |     |     |     |   |   |    | +n→           |     |     |                 |                    |                    |          |          |

NOTE:  $(PAIR)_H$ ,  $(PAIR)_L$  refer to high order and low order eight bits of the register pair respectively. e.g.,  $BC_L = C$ ,  $AF_H = A$ .

## 16-BIT LOAD GROUP (Continued)

| Mnemonic               | Symbolic<br>Operation                             | s | z |   | Fla<br>H | gs  | P/V | N | С | 76   | Opcod<br>543 |       | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Comme | 118 |

|------------------------|---------------------------------------------------|---|---|---|----------|-----|-----|---|---|------|--------------|-------|-----|-----------------|--------------------|--------------------|-------|-----|

| DIX, (nn)              | IX <sub>H</sub> ← (nn + 1)                        | • | • | × | •        | χ.  | •   | • | • | 11   | 011          | 101   | DD  | 4               | 6                  | 20                 |       | +   |

| <b>-</b> 17 (, (, 11 ) | IX <sub>I</sub> ← (nn)                            |   |   | ^ |          | ^   |     |   |   | 00   | 101          |       | 2A  |                 | ·                  |                    |       |     |

|                        |                                                   |   |   |   |          |     |     |   |   | ••   | +n→          | • • • |     |                 |                    |                    |       | į   |

|                        |                                                   |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       |     |

| D IY, (nn)             | IY <sub>H</sub> ← (nn + 1)                        |   |   | x |          | Х   |     |   |   | 11   | . 111        |       | FD  | 4               | 6                  | 20                 |       |     |

| J 11, (1.1.)           | IY <sub>L</sub> ← (nn)                            |   |   | ^ |          | •   |     |   |   | 00   | 101          |       | 2A  | ,               | ·                  |                    |       |     |

|                        | 115 (111)                                         |   |   |   |          |     |     |   |   | 00   | +n→          | 0.0   |     |                 |                    |                    |       |     |

|                        |                                                   |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       |     |

| O (nn), HL             | (nn + 1) ← H                                      |   |   | Х |          | х   |     |   |   | 00   | 100          | 010   | 22  | 3               | 5                  | 16                 |       |     |

| ٠, (١١١), ١١١          | (nn)+-L                                           | - | • | ^ | •        | ^   | •   |   | • | 00   | +n→          | 010   |     | J               | J                  |                    |       |     |

|                        | (111)                                             |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       |     |

| D (nn), dd             | (nn + 1) ← dd <sub>H</sub>                        |   |   | ¥ |          | х   |     |   |   | 11   | 101          | 101   | ED  | 4               | 6                  | 20                 |       |     |

| - (rii), uu            | (nn) ← dd <sub>L</sub>                            | • | • | ^ | •        | ^   | -   | • | • | 01   | dd0          |       | LD  | 7               | J                  | 20                 |       |     |

|                        | (iii) · uu[                                       |   |   |   |          |     |     |   |   | U    | + n →        | 011   |     |                 |                    |                    |       |     |

|                        |                                                   |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       |     |

| O (nn), IX             | (nn + 1) ← IX <sub>H</sub>                        |   |   | ¥ |          | х   |     |   |   | 11   | 011          | 101   | DD  | 4               | 6                  | 20                 |       | i   |

| - (ι ιι η, ι∧          | (nn) ← IX <sub>L</sub>                            | - | • | ^ | •        | ^   | •   | • | • | 00   | 100          |       | 22  | 7               | J                  | 20                 |       | İ   |

|                        | (111) - 12(                                       |   |   |   |          |     |     |   |   | w    | +n→          | 010   | ~~  |                 |                    |                    |       |     |

|                        |                                                   |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       |     |

| O (nn), IY             | (nn+1) ← IY <sub>H</sub>                          |   |   | ¥ |          | X · |     |   |   | 11   | 111          | 101   | FD  | 4               | 6                  | 20                 |       |     |

| J (1111), 11           | (nn) ← IY <sub>L</sub>                            | • | • | ^ | Ī        | ^   | •   | • | • | 00   | 100          |       | 22  | 7               | Ū                  | 20                 |       |     |

|                        | (iii) · II[                                       |   |   |   |          |     |     |   |   | 00   | +n→          | 010   | 22  |                 |                    |                    |       |     |

|                        |                                                   |   |   |   |          |     |     |   |   |      | +n→          |       |     |                 |                    |                    |       | 1   |

| D SP. HL               | SP - HL                                           | _ |   | х |          | х   |     | _ |   | 11   | 111          | 001   | F9  | 1               | 1                  | 6                  |       | i   |

| O SP. IX               | 4SP + IX                                          | - | • | x | •        | x   | •   |   | • | 11   | 011          | 101   | DD  | 2               | 2                  | 10                 |       |     |

| J UF, IA               | 10F 1-IA                                          | • | • | ^ | •        | ^   | •   | • | • | 11   | 111          | 001   | F9  | -               | -                  |                    |       |     |

| D SP, IY               | SP + IY                                           |   |   | х |          | х   |     |   |   | 11   | 111          | 101   | FD  | 2               | 2                  | 10                 |       |     |

| 5 51,11                | G( - 11                                           | - | • | ^ | •        | ^   | -   | - | - | 11   | 111          | 001   | F9  | -               | •                  |                    | qq Pa | air |

| USH qq                 | (SP - 2) ← qq <sub>L</sub>                        |   |   | ¥ |          | х   |     |   |   | 11   | qq0          | 101   |     | 1               | 3                  | 11                 | 00 B  | -   |

|                        | (SP - 1) ← qq <sub>H</sub>                        | • | ٠ | ^ | •        | ^   | •   | • | • | 1,1  | 440          |       |     | •               | •                  | •••                | 00 DI |     |

|                        | (SP → SP - 2                                      |   |   |   |          |     |     |   |   |      |              |       |     |                 |                    |                    | 10 H  | - 1 |

| USH IX                 | (SP-2) + IXL                                      |   |   | ¥ |          | х   |     |   |   | 11   | 011          | 101   | DD  | 2               | 4                  | 15                 | 11 AF | - 1 |

| 00111A                 | (SP - 1) ← IX <sub>H</sub>                        | • | • | ^ | •        | ^   | •   | • | • | 11   | 100          | 101   | E5  | -               | 7                  | .0                 | ^     |     |

|                        | SP→SP-2                                           |   |   |   |          |     |     |   |   | - 11 | ,00          | 101   | LU  |                 |                    |                    |       | -   |

| USHIY                  | SP-2) ← IY <sub>L</sub>                           |   |   | ¥ |          | х   |     |   |   | 11   | 111          | 101   | FD  | 2               | 4                  | 15                 |       | i   |

| OOMII                  |                                                   | • | • | ^ | •        | ^   | -   | • | • | 11   | 100          | 101   | E5  | _               | 7                  |                    |       |     |

|                        | $(SP-1) \leftarrow IY_H$<br>$SP \rightarrow SP-2$ |   |   |   |          |     |     |   |   | 11   | 100          | 101   | ES  |                 |                    |                    |       |     |

| OP oc                  | or → or - 2<br>qq <sub>H</sub> ← (SP + 1)         |   |   | v | _        | х   |     |   |   | 11   | qq0          | 001   |     | 1               | 3                  | 10                 |       |     |

| OP qq                  |                                                   | • | • | ^ | •        | ^   | •   | • | • | 11   | 440          | 001   |     | '               | 3                  | .0                 |       |     |

|                        | qqL ← (SP)<br>SP → SP +2                          |   |   |   |          |     |     |   |   |      |              |       |     |                 |                    |                    |       |     |

| OD IV                  |                                                   |   | _ | v | _        | v   | _   | _ | _ | 11   | 011          | 101   | DD  | 2               | 4                  | 14                 |       |     |

| OP IX                  | IX <sub>H</sub> + (SP + 1)                        | • | • | ^ | •        | Х   | •   | • | • | 11   | 011<br>100   | 001   | E1  | 2               | 4                  | 1-4                |       |     |

|                        | IX <sub>L</sub> ← (SP)                            |   |   |   |          |     |     |   |   | 11   | 100          | w     | E1  |                 |                    |                    |       |     |

|                        | SP → SP +2                                        |   |   |   |          | v   |     | _ |   |      | 444          | 404   |     |                 |                    | 14                 |       |     |

| OP IY                  | IY <sub>H</sub> ← (SP + 1)                        | • | • | X | •        | X   | . • | • | • | 11   | 111          | 101   | FD  | 2               | 4                  | 14                 |       |     |

|                        | IY <sub>L</sub> ← (SP)                            |   |   |   |          |     |     |   |   | 11   | 100          | 001   | E1  |                 |                    |                    |       |     |

|                        | SP → SP + 2                                       |   |   |   |          |     |     |   |   |      |              |       |     |                 |                    |                    |       |     |

NOTE: (PAIR)<sub>H</sub>, (PAIR)<sub>L</sub> refer to high order and low order eight bits of the register pair respectively, e.g., BC<sub>L</sub> = C, AF<sub>H</sub> = A.

## EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS

|             | Symbolic                                                      |   |                      |   |          | ags |          |     |   | 1        | Орсос      | ie         |          | No. of | No. of M | No. of T |                                                                                        |

|-------------|---------------------------------------------------------------|---|----------------------|---|----------|-----|----------|-----|---|----------|------------|------------|----------|--------|----------|----------|----------------------------------------------------------------------------------------|

| Mnemonic    | Operation                                                     | S | Z                    |   | Н        |     | P/       | V N | С | 76       | 543        | 210        | Hex      | Bytes  | Cycles   | States   | Comments                                                                               |

| EX DE, HL   | DE ++ HL                                                      | • | •                    | X | •        | X   | •        | •   | • | 11       | 101        | 011        | EB       | 1      | 1        | 4        |                                                                                        |

| EX AF, AF'  | AF ↔ AF′                                                      | • | •                    | Х | •        | Х   | •        | •   | • | 00       | 001        | 000        | 08       | 1      | 1        | 4        |                                                                                        |

| EXX         | BC ++ BC'<br>DE ++ DE'<br>HL ++ HL'                           | • | •                    | × | •        | X   | •        | •   | • | 11       | 011        | 001        | D9       | 1      | 1        | 4        | Register bank<br>and auxiliary<br>register bank<br>exchange                            |

| EX (SP), HL | H ++ (SP + 1)<br>L ++ (SP)                                    | • | •                    | X | •        | X   | •        | •   | • | 11       | 100        | 011        | E3       | 1      | 5        | 19       | o o name                                                                               |

| EX (SP), IX | IX <sub>H</sub> ++ (SP + 1)<br>IX <sub>1</sub> ++ (SP)        | • | •                    | X | •        | X   | •        | •   | • | 11<br>11 | 011<br>100 | 101<br>011 | DD<br>E3 | 2      | 6        | 23       |                                                                                        |

| EX (SP), IY | IYH ++ (SP+1)                                                 |   |                      | Y |          | Y   |          |     |   | 11       | 111        | 101        | FD       | 2      | 6        | 23       |                                                                                        |

| (o. ),      | IYL ++ (SP)                                                   |   |                      | ^ |          | ^   | ①        |     | • | 11       |            | 011        | E3       | 2      | 0        | 23       |                                                                                        |

| LDI         | (DE) ← (HL)<br>DE ← DE + 1<br>HL ← HL + 1<br>BC ← BC - 1      | • | •                    | X | 0        | X   | Ť        |     | • | 11<br>10 | 101<br>100 | 101<br>000 | ED<br>A0 | 2      | 4        | 16       | Load (HL) into<br>(DE), increment<br>the pointers and<br>decrement the<br>byte counter |

| LDIR        | (DE) ← (HL)                                                   |   |                      | ¥ | 0        | v   | @        | 0   |   | 11       | 101        | 101        | ED       | 2      | 5        | 21       | (BC)                                                                                   |

|             | DE ← DE+1<br>HL ← HL+1<br>BC ← BC-1<br>Repeat until<br>BC = 0 |   |                      |   | •        | ••  | •        | ·   |   | 10       |            | 000        | B0       | 2      | 4        | 16       | If BC = 0                                                                              |

|             |                                                               |   |                      |   |          |     | ①        |     |   |          |            |            |          |        |          |          |                                                                                        |

| LDD         | (DE) ← (HL)  DE ← DE – 1  HL ← HL – 1  BC ← BC – 1            | • | •                    | X | 0        | X   |          | 0   | • | 11<br>10 | 101<br>101 | 101<br>000 | ED<br>A8 | 2      | 4        | 16       |                                                                                        |

| LDDR        | (DE) <del></del> (HL)                                         |   |                      | x | 0        | х   | <b>②</b> | 0   | • | 11       | 101        | 101        | ED       | 2      | 5        | 21       | If BC ≠ 0                                                                              |

|             | DE + DE - 1 HL + HL - 1 BC + BC - 1 Repeat until BC = 0       |   |                      |   | •        |     |          | •   |   | 10       | 111        | 000        | B8       | 2      | 4        | 16       | If BC = 0                                                                              |

| CPI         | A - (HL)<br>HL ← HL+1<br>BC ← BC-1                            | ŧ | <b>③</b><br><b>•</b> | x | <b>‡</b> | x   | <b>①</b> | 1   | • | 11<br>10 | 101<br>100 | 101<br>001 | ED<br>A1 | 2      | 4        | 16       |                                                                                        |

NOTE: ① P/V flag is 0 if the result of BC - 1 = 0, otherwise P/V = 1.

② P/V flag is 0 only at completion of instruction.

③ Z flag is 1 if A = HL, otherwise Z = 0.

## EXCHANGE, BLOCK TRANSFER, BLOCK SEARCH GROUPS (Continued)

|          | Symbolic                                                | _        | _      |   |          | ıgs |     |   | _ |          | Opcod      |            |          | No. of | No. of M |        |                           |

|----------|---------------------------------------------------------|----------|--------|---|----------|-----|-----|---|---|----------|------------|------------|----------|--------|----------|--------|---------------------------|

| Mnemonic | Operation                                               | 5        | Z      |   | Н        |     | P/V | N | C | 76       | 543        | 210        | Hex      | Bytes  | Cycles   | States | Comments                  |

|          |                                                         |          | 3      |   |          |     | 1   |   |   | •        |            |            |          |        |          |        |                           |

| CPIR     | A – (HL)                                                | ‡        | #      | X | <b>‡</b> | X   | ŧ   | 1 | • | 11       | 101        | 101        | ED       | 2      | 5        | 21     | If BC ≠ 0 and<br>A ≠ (HL) |

| •        | HL ← HL + 1 BC ← BC − 1 Repeat until A = (HL) or        |          |        |   |          |     |     |   |   | 10       | 110        | 001        | B1       | 2      | 4        | 16     | If BC = 0 or<br>A = (HL)  |

|          | BC = 0                                                  |          | 3      |   |          |     | ①   |   |   |          |            |            |          |        |          |        |                           |

| CPD      | A - (HL)<br>HL ← HL - 1<br>BC ← BC - 1                  | *        | •      | X | *        | X   | •   | 1 | • | 11<br>10 | 101<br>101 | 101<br>001 | ED<br>A9 | 2      | 4        | 16     |                           |

| CPDR     | A – (HL)                                                | <b>‡</b> | ③<br>• | X | <b>‡</b> | X   | 0   | 1 | • | 11       | 101        | 101        | ED       | 2      | 5        | 21     | If BC ≠ 0 and<br>A ≠ (HL) |

|          | HL ← HL − 1 BC ← BC − 1 Repeat until A = (HL) or BC = 0 |          |        |   |          |     |     |   |   | 10       | 111        | 001        | В9       | 2      | 4        | 16     | If BC = 0 or<br>A = (HL)  |

NOTE:

P/V flag is 0 if the result of BC - 1 = 0, otherwise P/V = 1.

P/V flag is 0 only at completion of instruction.

Takes if A = (HL), otherwise Z = 0.

## 8-BIT ARITHMETIC AND LOGICAL GROUP

| Mnemonic       | Symbolic<br>Operation | s        | z        |   | Fla<br>H | gs | P/V | N | С        | 76 | Opcode<br>543 210 | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Com     | ments       |

|----------------|-----------------------|----------|----------|---|----------|----|-----|---|----------|----|-------------------|-----|-----------------|--------------------|--------------------|---------|-------------|

| ADD A, r       | A+A+r                 |          | <b>‡</b> | Х | <b>‡</b> | X  | ٧   | 0 | <b>‡</b> | 10 | 000 r             |     | 1               | 1                  | 4                  | r       | Reg.        |

| ADD A, n       | A ← A+n               | <b>‡</b> | #        | Х | <b>‡</b> | Х  | ٧   | 0 | <b>‡</b> | 11 | 000 110           |     | 2               | 2                  | 7                  | 000     | В           |

|                |                       |          |          |   |          |    |     |   |          |    | ←n→               |     |                 |                    |                    | 001     | C           |

|                |                       |          |          |   |          |    |     |   |          |    |                   |     |                 |                    |                    | 010     | D           |

| ADD A, (HL)    | A - A+(HL)            | <b>‡</b> |          | Х | <b>‡</b> | Х  | ٧   | 0 | <b>‡</b> | 10 | 000 110           |     | 1               | 2                  | 7                  | 011     | E           |

| ADD A, (IX + o | d) A←A + (IX + d)     | <b>‡</b> |          | Х | <b>‡</b> | Х  | ٧   | 0 | <b>‡</b> | 11 | 011 101           | DD  | 3               | 5                  | 19                 | 100     | н           |

|                |                       |          |          |   |          |    |     |   |          | 10 | 000 110           |     |                 |                    |                    | 101     | L           |

|                |                       |          |          |   |          |    |     |   |          |    | ←d→               |     |                 |                    |                    | 111     | Α           |

| ADD A, (IY+c   | (b+YI)+A→A (b         | <b>‡</b> | <b>‡</b> | Х | <b>‡</b> | Х  | ٧   | 0 | <b>‡</b> | 11 | 111 101           | FD  | 3               | 5                  | 19                 |         |             |

|                |                       |          |          |   |          |    |     |   |          | 10 | 000 110           |     |                 |                    |                    |         |             |

|                |                       |          |          |   |          |    |     |   |          |    | -d-               |     |                 |                    |                    |         |             |

| ADC A, s       | A - A+s+CY            | <b>‡</b> | #        | Х | <b>‡</b> | Х  | ٧   | 0 | <b>‡</b> |    | 001               |     |                 |                    |                    | s is ar | ny of r, n, |

| SUB s          | A ← A – s             | <b>‡</b> | <b>‡</b> | Х | <b>‡</b> | X  | ٧   | 1 | <b>‡</b> |    | 010               |     |                 |                    |                    | (HL),   | (IX+d),     |

| SBC A, s       | A - A-s-CY            | <b>‡</b> | #        | Х | <b>‡</b> | Х  | ٧   | 1 | <b>‡</b> |    | 011               |     |                 |                    |                    | (IY+    | d) as       |

| AND s          | A - A > s             | <b>‡</b> | #        | Х | 1        | Х  | Ρ   | 0 | 0        |    | 100               |     |                 |                    |                    | show    | n for ADD   |

| OR s           | A←A>s                 | <b>‡</b> | <b>‡</b> | Х | 0        | Х  | Ρ   | 0 | 0        |    | 110               |     |                 |                    |                    | instru  | ction. The  |

| XOR s          | A - Aes               | <b>‡</b> |          | Х | 0        | Х  | Ρ   | 0 | 0        |    | 101               |     |                 |                    |                    |         | ated bits   |

| CP s           | A-s                   | <b>‡</b> | <b>‡</b> | Х | <b>‡</b> | Х  | ٧   | 1 | <b>‡</b> |    | 111               |     |                 |                    |                    |         | e the       |

|                |                       |          |          |   |          |    |     |   |          |    |                   |     |                 |                    |                    | 000     | in the      |

|                |                       |          |          |   |          |    |     |   |          |    |                   |     |                 |                    |                    | ADD     | set above   |

## 8-BIT ARITHMETIC AND LOGICAL GROUP (Continued)

| Mnemonic   | Symbolic<br>Operation | 8        | z        |   | Fla      | ngs | P/V | N | С |    | Opcod<br>543 | je<br>210 | Hex | No. of<br>Bytes | No. of M<br>Cycles |    | Comments |

|------------|-----------------------|----------|----------|---|----------|-----|-----|---|---|----|--------------|-----------|-----|-----------------|--------------------|----|----------|

| INC r      | r≠r+1                 | <b>‡</b> | <b>‡</b> | х | #        | Х   | ٧   | 0 | • | 00 | r            | 100       |     | 1               | 1                  | 4  |          |

| INC (HL)   | (HL) ←                |          |          |   |          |     |     |   |   |    |              |           |     |                 |                    |    |          |

|            | (HL) + 1              | <b>‡</b> | <b>‡</b> | Х | <b>‡</b> | Х   | ٧   | 0 | • | 00 | 110          | 100       |     | 1               | 3                  | 11 |          |

| INC (IX+d) | (IX + d) <del>←</del> | <b>‡</b> |          | X | <b>‡</b> | Х   | ٧   | 0 | • | 11 | 011          | 101       | DD  | 3               | 6                  | 23 |          |

|            | (1X + d) + 1          |          |          |   |          |     |     |   |   | 00 | 110          | 100       |     |                 |                    |    |          |

|            |                       |          |          |   |          |     |     |   |   |    | <b>-</b> -d- | . —       |     |                 |                    |    |          |

| INC (IY+d) | (IY + d) ←            |          |          | X | <b>‡</b> | Х   | ٧   | 0 | • | 11 | 111          | 101       | FD  | 3               | 6                  | 23 |          |

|            | (IY+d)+1              |          |          |   |          |     |     |   |   | 00 | 110          | 100       |     |                 |                    |    |          |

|            |                       |          |          |   |          |     |     |   |   |    | <b>-</b> d-  | _         |     |                 |                    |    |          |

| DEC m      | m <b>←</b> m – 1      | #        | <b>*</b> | X | <b>‡</b> | X   | ٧   | 1 | • |    |              | 101       |     |                 |                    |    |          |

NOTE: m is any of r, (HL), (IX + d), (IY + d) as shown for INC. DEC same format and states as INC. Replace 100 with 101 in opcode.

## GENERAL-PURPOSE ARITHMETIC AND CPU CONTROL GROUPS

|          | Symbolic                |          |          |     | FI       | ngs |    |     |          | (        | Орсос      | le         |          | No. of | No. of M | No. of T |                                            |

|----------|-------------------------|----------|----------|-----|----------|-----|----|-----|----------|----------|------------|------------|----------|--------|----------|----------|--------------------------------------------|

| Mnemonic | Operation               | \$       | Z        |     | H        |     | PΛ | / N | C        | 76       |            | 210        | Hex      | Bytes  | Cycles   | States   | Comments                                   |

| DAA      | <b>@</b>                | <b>‡</b> | <b>‡</b> | X   | *        | X   | Р  | •   | <b>‡</b> | 00       | 100        | 111        | 27       | 1      | 1        | 4        | Decimal adjust                             |

| CPL      | A <del>-</del> A        | •        | •        | · X | 1        | X   | •  | 1   | •        | 00       | 101        | 111        | 2F       | 1      | 1        | 4        | Complement accumulator (one's complement). |

| NEG      | A - 0 - A               | <b>‡</b> | \$       | X   | <b>‡</b> | Х   | ٧  | 1   | <b>‡</b> | 11       | 101        | 101        | ED       | 2      | 2        | 8        | Negate acc.                                |

|          |                         |          |          |     |          |     |    |     |          | 01       | 000        | 100        | 44       |        |          |          | (two's complement).                        |

| CCF      | CY ← CY                 | •        | •        | X   | X        | X   | •  | 0   | ‡        | 00       | 111        | 111        | 3F       | 1      | . 1      | 4        | Complement carry flag.                     |

| SCF      | CY ← 1                  | •        | •        | X   | 0        | X   | •  | 0   | 1        | 00       | 110        | 111        | 37       | 1      | 1        | 4        | Set carry flag.                            |

| NOP      | No operation            | •        | •        | Х   | •        | Х   | •  | •   | •        | 00       | 000        | 000        | 00       | 1      | 1        | 4        | - 1                                        |

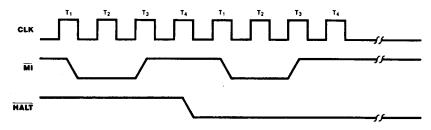

| HALT     | CPU halted              | •        | •        | Х   | •        | Х   | •  | •   | •        | 01       | 110        | 110        | 76       | 1      | 1        | 4        |                                            |

| DI ★     | IFF ← 0                 | •        | •        | Х   | •        | Х   | •  | •   | •        | 11       | 110        | 011        | F3       | 1      | 1        | 4        |                                            |

| El ★     | IFF ← 1                 | •        | ٠        | Х   | •        | Х   | •  | •   | •        | 11       | 111        | 011        | FB       | 1      | 1        | 4        | :                                          |

| IM 0     | Set interrupt           | •        | •        | Х   | •        | Х   | •  | •   | •        | 11       | 101        | 101        | ΕD       | 2      | 2        | 8        |                                            |

|          | mode 0                  |          |          |     |          |     |    |     |          | 01       | 000        | 110        | 46       |        |          |          |                                            |

| IM 1     | Set interrupt<br>mode 1 | •        | •        | X   | •        | X   | •  | •   | •        | 11       | 101        | 101        | ED       | 2      | 2        | 8        |                                            |

| IM 2     | Set interrupt           |          |          | х   |          | х   | _  |     |          | 01<br>11 | 010<br>101 | 110<br>101 | 56<br>ED | •      | •        | •        | :                                          |

|          | mode 2                  | •        |          | ^   | •        | ^   | •  | •   | •        | 01       | 011        | 110        | ED<br>5E | 2      | 2        | 8        | !                                          |

NOTES: @ converts accumulator content into packed BCD following add or subtract with packed BCD operands. IFF indicates the interrupt enable flip-flop.

CY indicates the carry flip-flop.

\* indicates interrupts are not sampled at the end of EI or DI.

## **16-BIT ARITHMETIC GROUP**

|            | Symbolic                |          |          |   | Fla | igs |     |   |          | (  | Opcod | e   |     | No. of | No. of M | No. of T |                 |               |

|------------|-------------------------|----------|----------|---|-----|-----|-----|---|----------|----|-------|-----|-----|--------|----------|----------|-----------------|---------------|

| Mnemonic   | Operation               | s        | Z        |   | Н   |     | P/V | N | C        |    | 543   |     | Hex | Bytes  | Cycles   | States   | Com             | merits        |

| ADD HL, ss | HL ← HL + ss            | •        | •        | Х | Х   | Х   | •   | 0 | <b>‡</b> | 00 | ssi   | 001 |     | 1      | 3        | 1,1      | SS              | R <b>e</b> g. |

|            |                         |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          | 00              | В¢            |

| ADC HL, ss | HL <del>←</del>         |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          | 01              | D₿            |

|            | HL+ss+CY                | <b>‡</b> | <b>‡</b> | Х | Х   | Х   | ٧   | 0 | <b>‡</b> | 11 | 101   | 101 | ED  | 2      | 4        | 15       | 10              | HL.           |

|            |                         |          |          |   |     |     |     |   |          | 01 | ss1   | 010 |     |        |          |          | 11              | SP            |

| SBC HL, ss | HL ←                    |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          |                 |               |

| 1          | HL-ss-CY                | <b>‡</b> | #        | Х | Х   | Х   | ٧   | 1 | <b>‡</b> | 11 | 101   | 101 | ED  | 2      | 4        | 15       |                 |               |

|            |                         |          |          |   |     |     |     |   |          | 01 | ss0   | 010 |     |        |          |          |                 |               |

| ADD IX, pp | IX + IX + pp            | •        | •        | Х | Х   | Х   | •   | 0 | <b>‡</b> | 11 | 011   | 101 | DD  | 2      | 4        | 15       | pp              | Reg.          |

|            |                         |          |          |   |     |     |     |   |          | 01 | pp1   | 001 |     |        |          |          | 00              | В¢            |

|            |                         |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          | Q1 <sup>′</sup> | Ð₿            |

|            |                         |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          | 10              | IX            |

|            |                         |          |          |   |     |     |     |   |          |    |       |     |     |        |          |          | 11              | SP            |

| ADD IY, rr | $IY \leftarrow IY + rr$ | •        | •        | Х | Х   | Х   | •   | 0 | <b>‡</b> | 11 | 111   | 101 | FD  | 2      | 4        | 15       | rr              | Reg.          |

|            |                         |          |          |   |     |     |     |   |          | 00 | rr1   | 001 |     |        |          |          | 00              | В¢            |

| NC ss      | ss ss + 1               | •        | •        | Х | •   | Х   | •   | • | •        | 00 | ss0   | 011 |     | 1      | 1        | 6        | 01              | D€            |

| NC IX      | IX - IX+1               | •        | •        | Х | •   | Х   | •   | • | •        | 11 | 011   | 101 | DD  | 2      | 2        | 10       | 10              | ΙΥ            |

|            |                         |          |          |   |     |     |     |   |          | 00 | 100   | 011 | 23  |        |          |          | 11              | SP            |

| NC IY      | $IY \leftarrow IY + 1$  | •        | •        | Х | •   | Х   | ٠   | • | •        | 11 | 111   | 101 | FD  | 2      | 2        | 10       |                 |               |

|            |                         |          |          |   |     |     |     |   |          | 00 | 100   | 011 | 23  |        |          |          |                 |               |

| DEC ss     | ss - ss - 1             | •        | •        | Х | •   | Х   | •   | • | •        | 00 | ss1   | 011 |     | 1      | 1        | 6        |                 |               |

| DEC IX     | $IX \leftarrow IX - 1$  | •        | •        | Х | •   | Χ   | •   | • | •        | 11 | 011   | 101 | DD  | 2      | 2        | 10       |                 |               |

|            |                         |          |          |   |     |     |     |   |          | 00 | 101   | 011 | 2B  |        |          |          |                 |               |

| DEC IY     | $IY \leftarrow IY - 1$  | •        | •        | Х | •   | Х   | •   | • | •        | 11 | 111   | 101 | FD  | 2      | 2        | 10       |                 |               |

|            |                         |          |          |   |     |     |     |   |          | 00 | 101   | 011 | 2B  |        |          |          |                 |               |

## **ROTATE AND SHIFT GROUP**

|       | Symbolic       |   |   |   | Fla | igs |     |   |          |    | Opcod | e   |           | No. of | No. of M | No. of T |                                           |

|-------|----------------|---|---|---|-----|-----|-----|---|----------|----|-------|-----|-----------|--------|----------|----------|-------------------------------------------|

| Mnemo | onic Operation | S | Z |   | Н   |     | P/V | N | С        | 76 | 543   | 210 | Hex       | Bytes  | Cycles   | States   | Comments                                  |

| RLCA  | CY + 7 + 0 +   | • | • | X | 0   | x   | •   | 0 | <b>‡</b> | 00 | 000   | 111 | 07        | 1      | 1        | 4        | Rotate left circular                      |

| RLA   | CY 7 4 0       | • | • | X | 0   | X   | •   | 0 | <b>‡</b> | 00 | 010   | 111 | <b>17</b> | 1      | 1        | 4        | accumulator<br>Rotate lefi<br>accumulator |

| RRCA  | 7 → 0 CY       | • | • | x | 0   | x   | •   | 0 | <b>‡</b> | 00 | 001   | 111 | 0F        | 1      | 1        | 4        | Rotate right<br>circular<br>accumulator   |

| RRA   | 7-0-CY         | • | • | X | 0   | X   | •   | 0 | <b>‡</b> | 00 | 011   | 111 | 1F        | 1      | 1        | 4        | Rotate right                              |

## ROTATE AND SHIFT GROUP (Continued)

| Mnemoni   | Symbolic<br>ic Operation                                    | s          | z        |   | Fla | ıgs | PΛ | / N | С        | 76               | Opcod<br>543        |            | Hex      | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | Comments                                                                       |

|-----------|-------------------------------------------------------------|------------|----------|---|-----|-----|----|-----|----------|------------------|---------------------|------------|----------|-----------------|--------------------|--------------------|--------------------------------------------------------------------------------|

| RLCr      |                                                             | <b>‡</b>   | <b>‡</b> | x | 0   | x   | P  | 0 ' | • •      | 11<br>00         | 001                 | 011<br>r   | СВ       | 2               | 2                  | 8                  | Rotate left<br>circular                                                        |

| RLC (HL)  | (T-0                                                        | ‡<br>      | <b>‡</b> | X | 0   | X   | P  | 0   | *        | 11<br><b>0</b> 0 | 001<br>000          | 011<br>110 | СВ       | 2               | 4                  | 15                 | register r. r Reg.                                                             |

| RLC (IX+  |                                                             | .‡         | <b>‡</b> | X | 0   | X   | P  | 0   | *        | 11<br>11<br>00   | 011<br>001<br>← d → |            | DD<br>CB | 4               | 6                  | 23                 | 001 C<br>010 D<br>011 E<br>001 H<br>101 L<br>111 A                             |

| RLC (IY+c | a) )                                                        | <b>‡</b>   | <b>‡</b> | X | 0   | X   | P  | 0   | #        | 11<br>11         | 111<br>001<br>+-d→  | 101<br>011 | FD<br>CB | 4               | 6                  | 23                 |                                                                                |

| RLm       | m = r, (HL, (IX + d), d)                                    | ٠          | ‡<br>d)  | x | 0   | x   | Р  | 0   | *        | 00               |                     | 110        |          | ř               |                    |                    | Instruction<br>format and<br>states are as<br>shown for                        |

| RRC m     | $m = r_{i}(HL),(IX + d),$                                   | ‡<br>,(IY+ | <b>‡</b> | x | 0   | x   | P  | 0   | *        |                  | 001                 |            |          |                 |                    |                    | RLCs. To form<br>new opcode<br>replace 000<br>or RLCs with                     |

| Rm (      | + [7 → 0] → [CY]<br>m = r,(HL),(IX + d),                    | ‡<br>(IY+  | ‡<br>d)  | x | 0   | x   | P  | 0   | *        |                  | 011                 |            |          |                 |                    |                    | shown code.                                                                    |

| SLA m     | $CY = 7 \leftarrow 0 \leftarrow 0$ $m = r_1(HL), (iX + d),$ |            |          | x | 0   | x   | P  | 0   | <b>‡</b> |                  | 100                 |            |          |                 |                    |                    | :                                                                              |

| SRAm [    | $m = r_i(HL), (iX + d),$                                    | ‡<br>(IY+  |          | x | 0   | X   | Р  | 0   | <b>*</b> | . 2.             | 101                 |            |          |                 |                    |                    |                                                                                |

| SRLm •    | m = r, (HL), (IX + d), (IX + d)                             |            |          | X | 0   | X   | Ρ  | 0   | <b>‡</b> |                  | 111                 |            |          |                 |                    |                    | :                                                                              |

| RLD 7-4   | 20 74 20<br>(HL)                                            |            | *        | x | 0   | x   | P  | 0   | •        | 11<br>01         | 101<br>101          | 101<br>111 | ED<br>6F | 2               | 5                  |                    | Rotate digit<br>left and<br>right between<br>the accumu-<br>lator and          |

| RD 7-4    | 30 - 74 30<br>(HL)                                          | <b>‡</b>   | <b>‡</b> | x | 0   | x   | Р  | 0   | •        | 11<br>01         | 101<br>100          | 101<br>111 | ED<br>67 | 2               | 5                  | 18                 | location (HL). The content of the upper half of the accumulator is unaffected. |

## BIT SET, RESET AND TEST GROUP

|                     | Symbolic                           |   |          | • | Fla | ngs |     |   |     | (  | Opcod       | •   |     | No. of | No. of M | No. of T |       |            |

|---------------------|------------------------------------|---|----------|---|-----|-----|-----|---|-----|----|-------------|-----|-----|--------|----------|----------|-------|------------|

| Mnemonic            | Operation                          | 8 | Z        |   | Н   |     | P/V | N | C   | 76 | 543         | 210 | Hex | Bytes  | Cycles   | States   | Соп   | ments      |

| BIT b, r            | Z←rb                               | х | <b>‡</b> | х | 1   | Х   | х   | 0 | •   | 11 | 001         | 011 | СВ  | 2      | 2        | 8        | r     | Reg.       |

|                     |                                    |   |          |   |     |     |     |   |     | 01 | ь           | r   |     |        |          |          | 000   | В          |

| BIT b, (HL)         | Z ← (HL) <sub>b</sub>              | X | <b>‡</b> | Х | 1   | Х   | Х   | 0 | •   | 11 | 001         | 011 | CB  | 2      | 3        | 12       | 001   | С          |

|                     |                                    |   |          |   |     |     |     |   |     | 01 | b           | 110 |     |        |          |          | 010   | D          |

| BIT b,(IX + d)b     | $Z \leftarrow (IX + d)_b$          | X | <b>‡</b> | X | 1   | Х   | X   | 0 | •   | 11 | 011         | 101 | DD  | 4      | 5        | 20       | 011   | E          |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | 001         | 011 | СВ  |        |          |          | 100   | Н          |

|                     |                                    |   |          |   |     |     |     |   |     |    | <b>-</b> d- | •   |     |        |          |          | 101   | L          |

|                     |                                    |   |          |   |     |     |     |   |     | 01 | b           | 110 |     |        |          |          | 111   | Α          |

|                     | •                                  |   |          |   |     |     |     |   |     |    |             |     |     |        |          |          | b     | Bit Teste  |

| BIT b, $(1Y + d)_b$ | Z ← (IY + d) <sub>b</sub>          | X | <b>‡</b> | X | 1   | Х   | X   | 0 | •   | 11 | 111         | 101 | FD  | 4      | 5        | 20       | 000   | 0          |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | 001         | 011 | CB  |        |          |          | 001   | 1          |

|                     |                                    |   |          |   |     |     |     |   |     |    | <b>←</b> d→ | •   |     |        |          |          | 010   | 2          |

|                     |                                    | • |          |   |     |     |     |   |     | 01 | b           | 110 |     |        |          |          | 011   | 3          |

| SET b, r            | r <sub>b</sub> ← 1                 | • | •        | Х | •   | Х   | •   | • | . • | 11 | 001         | 011 | CB  | 2      | 2        | 8        | 100   | 4          |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | b           | r   |     |        |          |          | 101   | 5          |

| SET b, (HL)         | (HL) <sub>b</sub> ← 1              | • | •        | X | •   | Χ   | •   | • | •   | 11 | 001         | 011 | CB  | 2      | 4        | 15       | 110   | 6          |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | b           | 110 |     |        |          |          | 111   | 7          |

| SET b, (IX + d)     | (IX+d) <sub>b</sub> <del>-</del> 1 | • | •        | X | •   | X   | •   | • | •   | 11 | 011         | 101 | DD  | 4      | 6        | 23       |       |            |

|                     |                                    | - |          |   |     |     |     |   |     | 11 | 001         | 011 | CB  |        |          |          |       |            |

|                     |                                    |   |          |   |     |     |     |   |     |    | ←d→         | •   |     |        |          |          |       |            |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | b           | 110 |     |        |          |          |       |            |

| SET b, (IY+d)       | $(iY+d)_b \leftarrow 1$            | • | •        | X | •   | Х   | •   | • | •   | 11 | 111         | 101 | FD  | 4      | 6        | 23       |       |            |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | 001         | 011 | CB  |        |          |          |       |            |

|                     |                                    |   |          |   |     |     |     |   |     |    | ←d →        | •   |     |        |          |          |       |            |

|                     |                                    |   |          |   |     |     |     |   |     | 11 | b           | 110 |     |        |          |          |       |            |

| RES b, m            | m <sub>b</sub> ← 0                 | • | •        | X | •   | X   | •   | • | •   | 10 |             |     |     |        |          |          | -     | uu uein    |

|                     | m≡r, (HL),                         |   |          |   |     |     |     |   |     |    |             |     |     |        | •        |          | •     | ode replac |

|                     | (1X+d), $(1Y+d)$                   |   |          |   |     |     |     |   |     |    |             |     |     |        |          |          |       | of SET b,  |

|                     |                                    |   |          |   |     |     |     |   | •   |    |             |     |     |        |          |          | with  | 10 Flag    |

|                     |                                    |   |          |   |     |     |     |   |     |    |             |     |     |        |          |          | and   | time       |

|                     |                                    |   |          |   |     |     |     |   |     |    |             |     |     |        |          |          | state | s for SET  |

|                     |                                    |   |          |   |     |     |     |   |     |    |             |     |     |        |          |          | instr | uction.    |

NOTE: The notation  $m_{\mbox{\scriptsize b}}$  indicates location m, bit b (0 to 7).

## **JUMP GROUP**

| Mnemonic  | Symbolic<br>Operation | s | z |    | FI | <b>ag</b> s |   | ۷N | С |    | Opco<br>543 | <b>ie</b><br>210 | Hex | No. of<br>Bytes | No. of M<br>Cycles | No. of T<br>States | •      | nments            |

|-----------|-----------------------|---|---|----|----|-------------|---|----|---|----|-------------|------------------|-----|-----------------|--------------------|--------------------|--------|-------------------|

| JP nn     | PC ← nn               | • | • | х  | •  | Х           | • | •  | • | 11 | 000         | 011              | СЗ  | 3               | 3                  | 10                 | œ      | Condition         |

|           |                       |   |   |    |    |             |   |    |   |    | ←n-         | •                |     |                 |                    |                    | 000    | NZ (non-zero)     |

|           |                       |   |   |    |    |             |   |    |   |    | <b>←</b> n~ | •                |     |                 |                    |                    | 001    | Z (zero)          |

| JP cc, nn | If condition cc       |   | • | Х  | •  | Χ           | • | •  | • | 11 | œ           | 010              |     | 3               | 3                  | 10                 | 010    | NC (non-carry)    |

|           | is true PC←nn,        |   |   |    |    |             |   |    |   |    | ←n-         | •                |     |                 |                    |                    | 011    | C (carry)         |

|           | otherwise             |   |   |    |    |             |   |    |   |    | ←n-         | •                |     |                 |                    |                    | 100    | PO (parity odd)   |

| _         | continue              |   |   |    |    |             |   |    |   |    |             |                  |     |                 |                    |                    | 101    | PE (parity even)  |

| JR e      | PC ← PC+e             | • | • | Х  | •  | Х           | • | •  | • | 00 |             | 000              | 18  | 2               | 3                  | 12                 | 110    | P (sign positive) |

|           | _                     |   |   |    |    |             |   |    |   | •  | -e-2        |                  |     |                 |                    |                    | 111    | M (sign negiative |